热门标签

热门文章

- 1步进电机基本知识_步进电机知识

- 212.2 算法模型三大框架(Encoder-Only、Encoder-Decoder、Decoder-Only)_bert是encode only的吗

- 3Python编程基础:Python简介及开发环境搭建_python开发环境

- 4c++入门

- 5python视频框架_Python视频编辑库:MoviePy

- 6鸿蒙系统开发【加解密算法库框架】安全

- 7Visual Studio Code 插件Polacode的使用技巧

- 8Weblogic 常见漏洞分析与利用_weblogic漏洞

- 9python cv2.imread 读取中文路径的图片返回为None的问题_imread python 中文

- 10ChatGPT的前世今生,到如今AI领域的竞争格局,本文带你一路回看!_chatgpt——circuit mind

当前位置: article > 正文

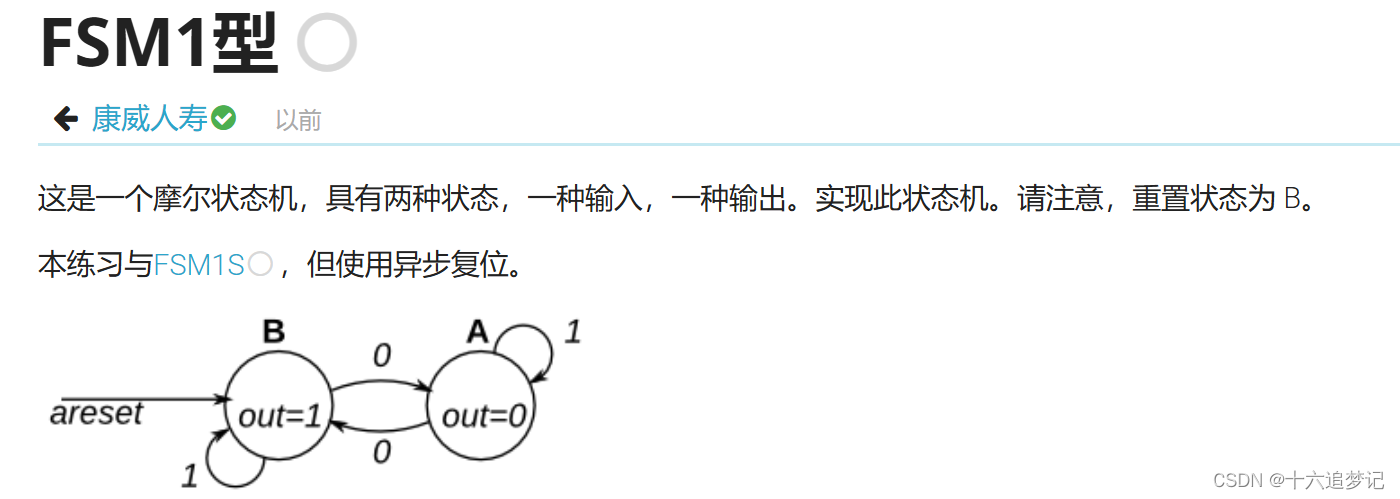

Verilog刷题笔记48——FSM1型异步复位_verilog fsm

作者:从前慢现在也慢 | 2024-08-01 19:29:08

赞

踩

verilog fsm

题目:

解题:

module top_module( input clk, input areset, // Asynchronous reset to state B input in, output out);// parameter A=0, B=1; reg state, next_state; always @(*) begin // This is a combinational always block // State transition logic case(state) A:begin if(in==0) next_state=B; else next_state=A; end B:begin if(in==0) next_state=A; else next_state=B; end endcase end always @(posedge clk, posedge areset) begin // This is a sequential always block // State flip-flops with asynchronous reset if(areset) state<=B; else state<=next_state; end // Output logic assign out = (state == A)?0:1; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

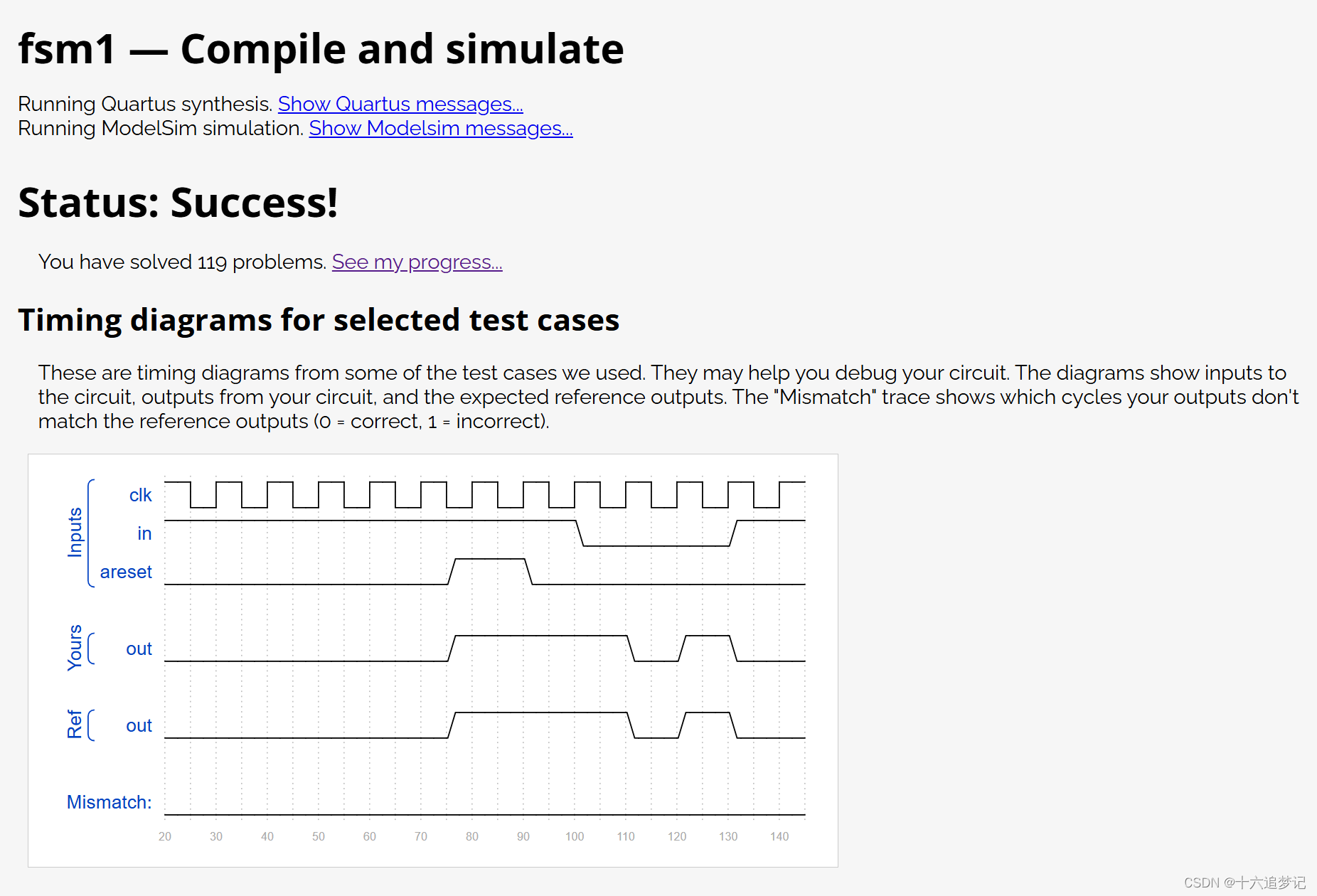

结果正确:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/915575

推荐阅读

相关标签