热门标签

热门文章

- 1Yolov5项目在RK3588s设备上的部署(RMYC2023技术分享)_基于yolov5与arcface算法实现人脸检测并部署于开发板rk3588上以及拓展

- 2ROS2学习笔记(1)在Ubuntu22.04中安装ROS2_ros2 ubuntu

- 3ArkTS基础学习笔记_arkts文档

- 4css补充2:flex布局,居中方案等_css flex 居中

- 5unity关于场景烘焙及材质问题_unity 烘培模型设置

- 6Linux常用命令_linux logcat

- 7AndroidStudio检测不到华为手机_android studio怎么驱动什么都装好了还识别不出来鸿蒙华为手机

- 8命令行工具: logcat 使用详解

- 9一文读懂“语言模型”

- 10深入了解Android蓝牙Bluetooth【基础+进阶】_android 蓝牙

当前位置: article > 正文

基于FPGA的时间数字转换(TDC)设计(二:多相位设计)_tdc fpga

作者:你好赵伟 | 2024-04-09 08:44:32

赞

踩

tdc fpga

1、多相位TDC计时FPGA代码设计

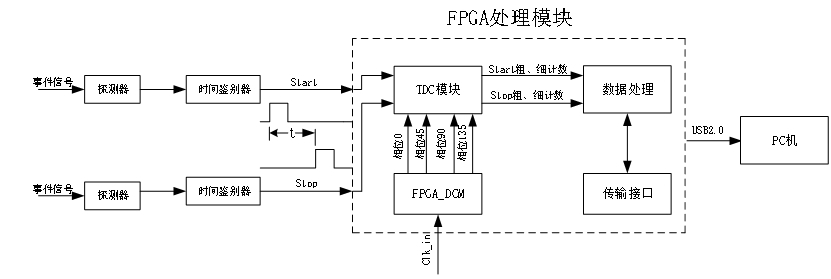

接上期的讲解,本期主要讲多相位TDC计时的FPGA代码实现。图1为TDC测量实现系统图。时间信号经过探测器后,转换为电信号,一般探测器出来的信号幅度和脉宽都比较小,需要时间鉴别器进行比较和整形,以便于FPGA能够识别。经过FPGA TDC计时模块后,测量出两信号的时间差。将打包好的数据,通过USB2.0接口传输给上位机软件。

图1 TDC测量实现框图

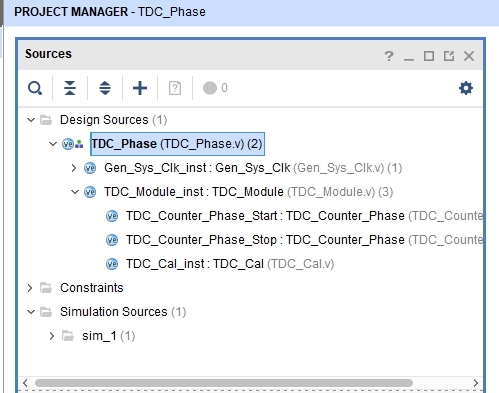

在本方案中,TDC计时设计的时间分辨率为312.5ps,主频为400Mhz(2.5ns),采用8相位设计,这样就可以满足设计要求了。根据笔者经验,多相位采用Xilinx FPGA芯片最多能做到16相位,最小分辨率大概在156ps左右。读者可以在评论中留言讨论或者向笔者索要工程文件。图2为多相位TDC计时实现FPGA代码架构,主要由时钟产生模块,TDC模块等组成。

图2 多相位TDC计时实现FPGA代码架构

1.1 多相时钟产生模块

时钟模块负责产生

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/你好赵伟/article/detail/391563

推荐阅读

相关标签