- 1HTML转义字符对照表(部分)_

- 2深度学习中,网络、模型、算法有什么区别_大模型算法和推荐算法 卷积神经网络的区别

- 3查准查全:情感分析与自然语言处理的结合

- 4实现:mysql-5.7.42 到 mysql-8.2.0 的升级(rpm方式)_升级数据库版本

- 5PMP证书的含金量高吗?值得考吗?_pmp证书你值得拥有

- 6Impala安装文档完整版_apache-impala-4.1.2.tar.gz

- 77-15 树的遍历 (25分)

- 8ROS和MATLAB实现服务通信_mworks可以和ros

- 9v-for中为什么要用key?有什么作用,为什么不能以index作为key?_遍历数组的时候 为什么要加key属性,如果使用数组的index会发生什么问题

- 10spring boot 开启kafka事务_kafka开启事物

FPGA——状态机_fpga状态机

赞

踩

本来想只是学学状态机,但是碰到状态机就不可能不谈FPGA,刚好之前没有特别的深入了解,所以刚好在这里了解一下。

一、FPGA

(一)什么是FPGA

首先,FPGA是Field Programmable Gate Array的简写,翻译过来就是“现场可编程门阵列”。它是一个集成电路,可以对其反复配置以执行无限多的功能。

具体而言,FPGA就是由可编程逻辑功能块和可编程I/O模块排成阵列组成,并由可编程的内部连线连接这些逻辑功能块和I/O模块来实现不同的设计,而一般来说,现在都是用的Verilog来进行这些方面的编程。

1.FPGA的架构:

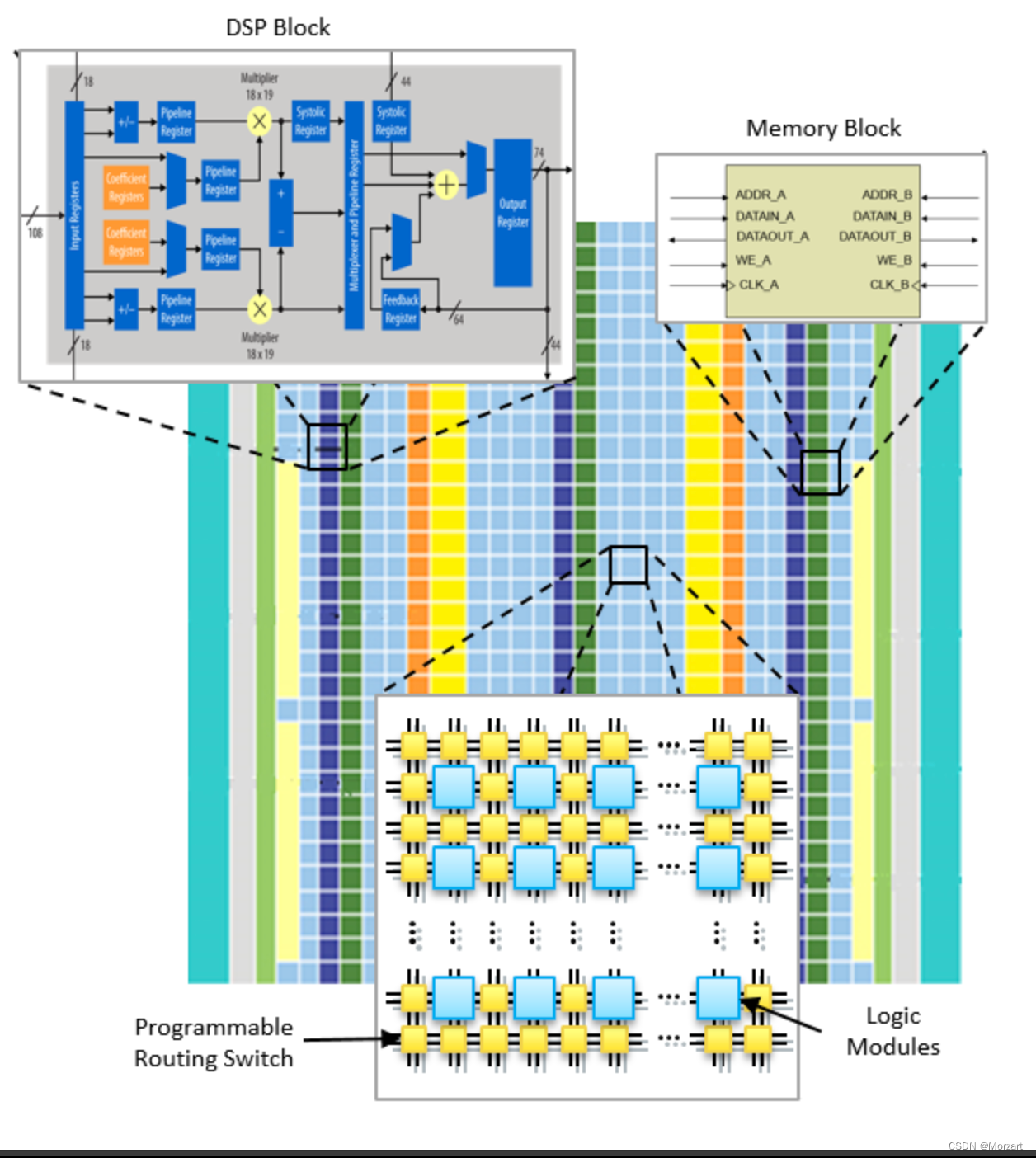

一个FPGA由几个小的计算单元组成。通过编程计算单元并将它们连接起来就可将定制数据路径直接构建到架构中,,如下图所示。

可以从上图看出,FPGA是由DSP Block(数字信号处理器模块)、Memory Block(内存块)、Programmable Routing Switch(可编程路由交换机)以及Logic Block(逻辑模块)组合而成的。

2.FPGA的运行方式

FPGA不同于其他使用冯诺依曼结构的处理器,他是基于逻辑门与触发器并行执行操作的,即当CLOCK上升沿到来时所有的触发器都会有动作,它不像冯氏结构处理器一样需要进行取指令->执行的操作。因此对于一些复杂、重复性不强任务,FPGA不如冯氏结构处理器,但是对于重复性强的任务FPGA就比较适合了。

(二)FPGA的特点

1.低时延

FPGA是由用户自定义处理流程,可以直接决定片上的 CLB 是如何相连的,数十万个 CLB 可以独立运算,即 SIMD、MISD (Multiple Instruction Single Data) 和 MIMD (Multiple Instruction Multiple Data) 的处理都可以在 FPGA 实现,由于处理流程已经映射到硬件上,不需要再额外花费时间获取和编译指令, 同样不需要像CPU一样花费时间在乱序执行等步骤,这使得 FPGA 在数据处理中具有非常低的时延。

2.并行处理

因为FPGA的运行方式,所以它比冯氏结构更好进行并行任务的处理,因此在一些数据处理上速度要快很多。

二、状态机

而基于这种由逻辑功能块和可编程I/O模块进行并行执行的FPGA,我们也需要处理具有先后顺序的东西,所以在这时就需要使用到状态机。

(一)状态机(FSM)

FSM(Finite State Machine),也称为同步有限状态机,之所以说“同步”是因为状态机中所有的状态跳转都是在时钟的作用下进行的,而“有限”则是说状态的个数是有限的。状态机的每一个状态代表一个事件,从执行当前事件到执行另一事件我们称之为状态的跳转或状态的转移,我们需要做的就是执行该事件然后跳转到一下时间,这样我们的系统就“活”了,可以正常的运转起来了。状态机通过控制各个状态的跳转来控制 流程,使得整个代码看上去更加清晰易懂,在控制复杂流程的时候,状态机优势明显。

(二)Moore状态机和Mealy状态机

根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔(Moore)型状态机和米利(Mealy) 型状态机。

1.摩尔状态机

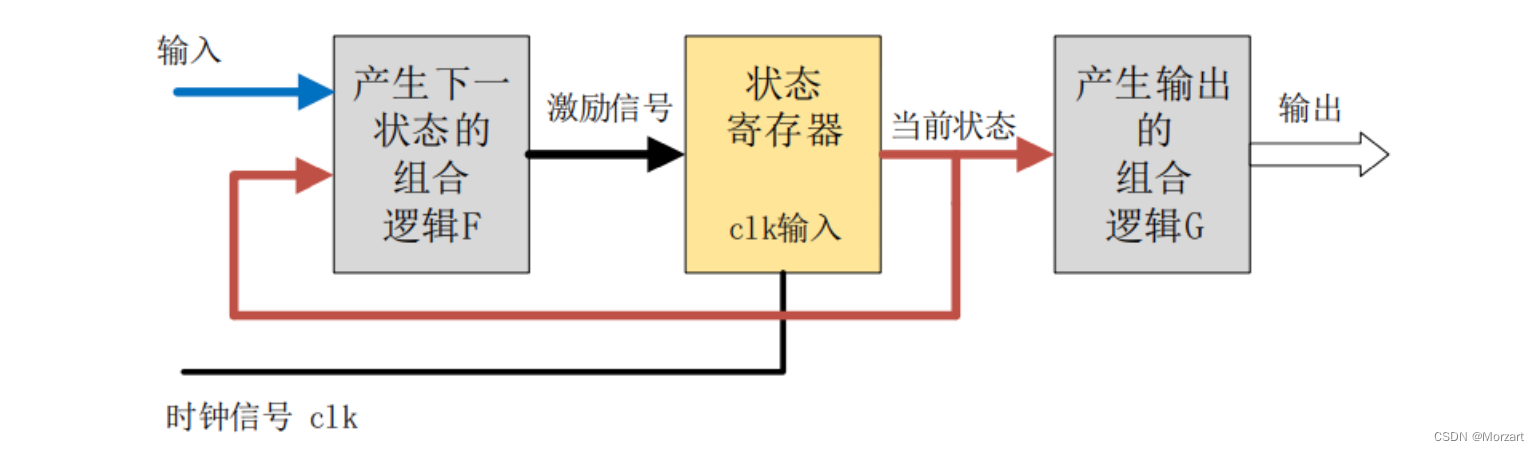

由上图可知,模型中第一个方框是指产生下一状态的组合逻辑 F,F 是当前状态和输 入信号的函数,状态是否改变、如何改变,取决于组合逻辑 F 的输出;第二框图是指状态寄存器,其由一 组触发器组成,用来记忆状态机当前所处的状态,状态的改变只发生在时钟的跳边沿;第三个框图是指产生输出的组合逻辑 G,状态机的输出是由输出组合逻辑 G 提供的,G 也是当前状态的函数。

2.米利状态机

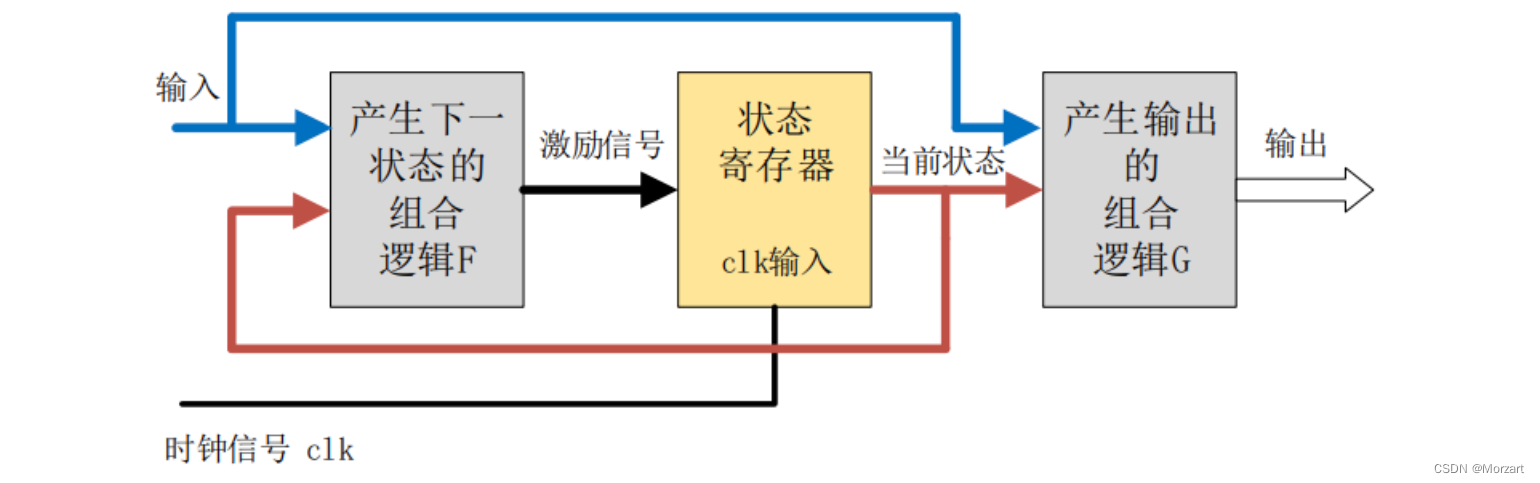

上图为米利状态机,对比摩尔状态机的模型可以发现,其区别在于摩尔状态机的输出只取决于当前状态,而米利状态机的输出由当前状态和输入条件决定的。

3.异同

-

Moore型的输出只与当前状态有关,而Mealy型的输出还与输入相关。

-

在实现相同功能的情况下,Mealy型状态机所需要的状态数比Moore型少,Moore需要待状态稳定才输出。

-

输出时序上,Moore状态机同步输出,Mealy状态机异步输出。

-

输出变化上,Mealy状态机比Moore状态机领先一个时钟周期。

(三)状态机描述方式

状态机不仅分为Moore和Mealy类型,还有着不同的描述方式。一般分为:一段式、二段式、三段式,

1.一段式状态机

最主要的特征是只有一个always块。在这个always块内既描述状态转移,又含有组合逻辑输入/输出,当前状态用寄存器输出;在这种状态机的写法中,组合逻辑电路和时序逻辑电路都在一起,没有分开;因此这种写法增加了代码的复杂度且不利于代码的维护和修改,同时也不利于后期约束。

2.二段式状态机

最主要的特征是有两个always块,将组合逻辑和时序逻辑分开。其中一个always块采用同步时序描述状态转移,而另一个always块采用组合逻辑来判断状态转移的条件,描述状态转移规律及输出;在这种写法下,需要定义两个状态,分别是现态和次态,通过现态和次态的转换来实现状态转移;两段式状态机可以清晰完整的显示出状态机的结构,有利于代码的维护和后期修改,同时也降低编写复杂度。

3.三段式状态机

最主要的特征是有三个always块。区别于两段式状态机的关键在于两段式状态机直接采用组合逻辑输出,而三段式状态机则通过在组合逻辑后再增加一级寄存器实现逻辑输出

- 一个always块采用同步时序描述状态转移

- 一个always块采用组合逻辑判断转移条件、转移状态规律,

- 一个always块采用同步时序描述状态的输出

这种三段式状态机的写法代码非常清晰,极大降低了编写维护代码的复杂度,最大程度清晰完整的显示出状态机的结构。同时可以有效地滤除两段式状态机组合逻辑输出可能产生的毛刺信号;另外对于总线形式的输出来说,容易使总线数据对齐,从而减小总线数据间的偏移,减小接收端数据采样出错的频率;但是三段式消耗的资源相对多一点,并且三段式从输入到输出比一段式和二段式会延时一个时钟周期。

4.状态机的编码方式

①独热码

即 One-Hot 编码,又称一位有效编码,每个码元值只有一位是’1’,其他位都是’0’,

如S0=3’b001,S1=3’b010,S2=3’b100

即N个状态需要N个触发器。独热码状态机的速度仅与到某特定状态的转移数量有关而与状态数量无关,速度很快。且由于其状态译码简单,所以节省和简化了组合逻辑电路。FPGA器件由于寄存器数量多而逻辑门资源紧张,采用独热编码可以有效提高FPGA资源的利用率和电路的速度。独热码还具有设计简单、修改灵活和易于调试、易于综合、易于寻找关键路径、易于进行静态时序分析等优点。因此尽量采用独热编码。

②格雷码

在相邻状态的转换中,每次只有一位比特位发生变化,可以减少产生毛刺和一些暂态的可能,但不适合于有很多状态跳转的情况。

递归生成码表

这种方法基于格雷码是反射码的事实,利用递归的如下规则来构造:

-

1位格雷码有两个码字

-

(n+1)位格雷码中的前2n个码字等于n位格雷码的码字,按顺序书写,加前缀0

-

(n+1)位格雷码中的后2n个码字等于n位格雷码的码字,按逆序书写,加前缀1 [4]

-

n+1位格雷码的集合 = n位格雷码集合(顺序)加前缀0 + n位格雷码集合(逆序)加前缀1

| 2位格雷码 | 3位格雷码 | 4位格雷码 | 4位自然二进制码 |

|---|---|---|---|

| 00 | 000 | 0000 | 0000 |

| 01 | 001 | 0001 | 0001 |

| 11 | 011 | 0011 | 0010 |

| 10 | 010 | 0010 | 0011 |

| 110 | 0110 | 0100 | |

| 111 | 0111 | 0101 | |

| 101 | 0101 | 0110 | |

| 100 | 0100 | 0111 | |

| 1100 | 1000 | ||

| 1101 | 1001 | ||

| 1111 | 1010 | ||

| 1110 | 1011 | ||

| 1010 | 1100 | ||

| 1011 | 1101 | ||

| 1001 | 1110 | ||

| 1000 | 1111 |

③2进制

二进制编码为最紧凑的编码,采用顺序的二进制数编码的每个状态。

| state0 | state1 | state2 | state3 |

|---|---|---|---|

| 表示为:00 | 01 | 10 | 11 |

优点在于它使用状态向量的位数最小。但其从一个状态转换到另一个状态时,可能会有多位比特位发生变化,[有中间态产生] 瞬变次数多,易产生毛刺,引发逻辑错误

四、参考引用

「Intel」1.1. FPGA概述

「FPGA研究院」FPGA、 CPU、GPU、ASIC区别

FPGA的基本原理(详细+入门)

FPGA和CPU、GPU有什么区别?为什么越来越重要?

「无牙大白鲨」FPGA状态机

「皮皮祥」三种状态机的区别?

「多喝烫水-」Verilog --状态机编码方式