- 1python在财务上的应用论文,python在财务领域的应用_python财会npv

- 2Python之Opencv教程(1):读取图片、图片灰度处理_读取灰度图

- 3vue-cli自定义创建项目-eslint依赖冲突解决方式_conflicting peer dependency: eslint-plugin-vue@7.2

- 4【Python基础】一文搞懂:Python 中 csv 文件的写入与读取_python csv

- 5安全领域中如何有效的使用机器学习_安全评价怎么和机器学习结合

- 6探秘MBTI原理:如何解读你的性格密码?(包含API

- 7详解数组的下标_数组下标

- 8Pytorch:Transformer(Encoder编码器-Decoder解码器、多头注意力机制、多头自注意力机制、掩码张量、前馈全连接层、规范化层、子层连接结构、pyitcast) part2

- 9自动驾驶合集5_异构数据高维输入空间

- 10ROS笔记(三)用键盘控制模型在gazebo中移动_gazebo如何移动模型

基于FPGA读写MT25QL FLASH芯片_fm25q128a fpga读写数据

赞

踩

在FPGA上面根据SPI接口协议用verilog语言读写MT25QL128ABA FLASH芯片

目录

前言

FLASH存储器又称闪存,是一种长寿命的非易失性存储器,一般用来保存一些重要的设置信息或者程序等等。本文将在介绍FLASH有关的基础知识后,说明如何配置MT25QL128ABA这块FLASH芯片,包含对相关指令的解析和读写操作需要注意的点,当然,仿真图必不可少了,文中也有给出相应的仿真图。

提示:以下是本篇文章正文内容,希望能帮助到各位,转载请附上链接。

一、FLASH简介

FLASH存储器又称闪存,是一种长寿命的非易失性(在断电情况下仍能保持所存储的数据信息)存储器,一般用来保存一些重要的设置信息或者程序等等。

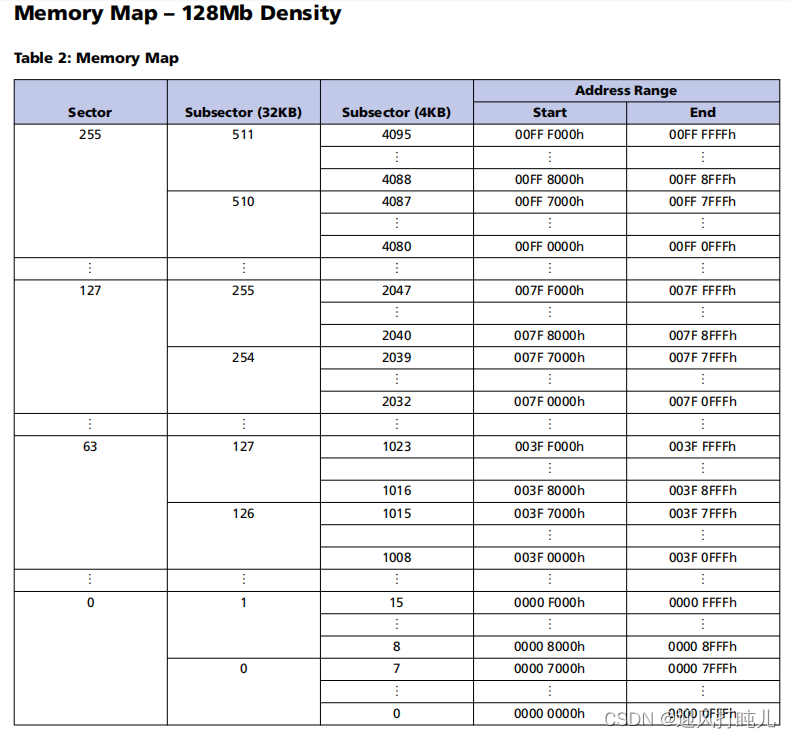

介绍的FLASH芯片型号为MT25QL128ABA,它是由Micron公司生产的一款高性能FLASH芯片。这款芯片的总容量为128Mbit,16MB,整个存储阵列被分成4096个4KB子扇区,每页的容量为256字节。它支持Standard SPI、Dual SPI和Quad SPI三种SPI协议通信方式,最大支持的传输数据频率可达133MHz。

二、管脚信息

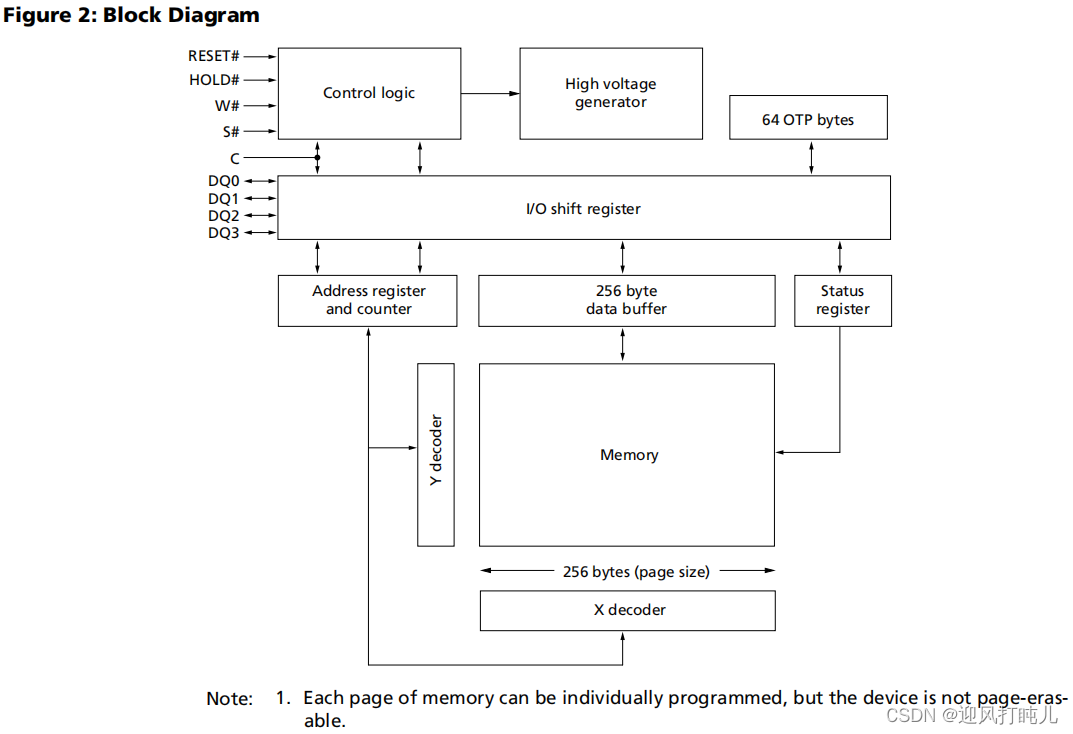

阅读该图可知DQ引脚进出的数据与Memory之间有一个I/O shift register ,还有一个256字节的数据缓存器(256 byte data buffer),这将导致写入的时候数据进来后先缓存在data buffer这里,再通过地址寄存器及计数器写入到Memory里面,所以写入是需要一定时间的。另外,写入数据之前要先进行擦除,让Memory里面所有Bit为高电平,擦除完成之后在进行写入。

需要注意的是,该FLASH芯片的每一页(256个字节)都可以单独编程,但器件不能进行页擦除,最小擦除单位是4KB(4096字节)的子扇区。

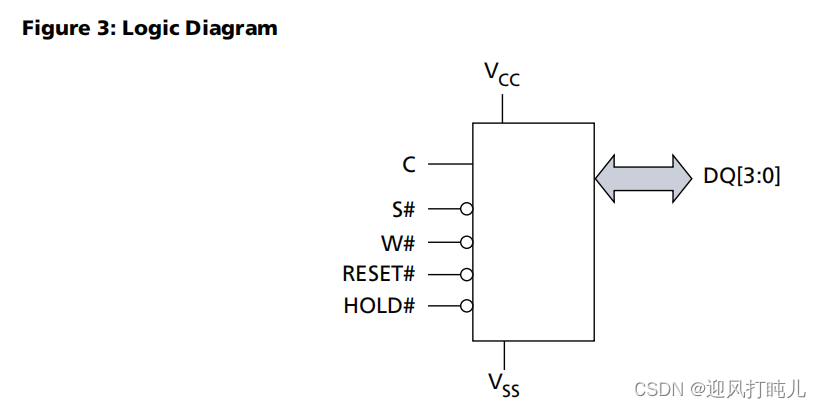

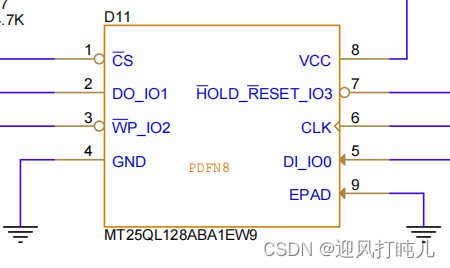

下图是该芯片的管脚定义信息。

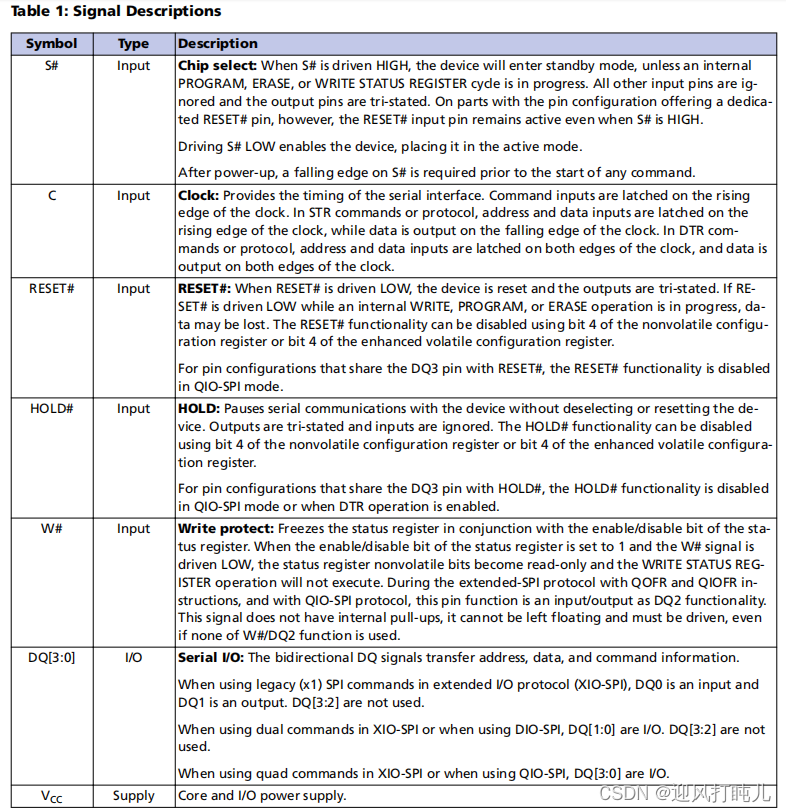

S# 输入片选,被驱动为高电平时,器件将进入待机模式,除非内部编程、擦除或写入状态寄存器周期正在进行中。所有其他输入引脚均被忽略,输出引脚为三态。然而,在具有提专用 RESET#引脚的 引脚配置的部件上,即使 S# 为高电平,RESET# 输入引脚仍保持活动状态。

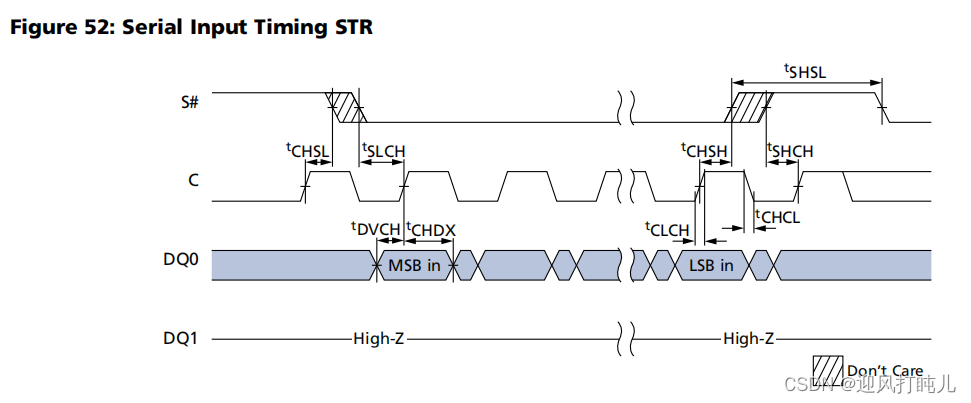

C 时钟,提供串行接口的时序。命令输入在上升沿被锁存时钟的边缘。在STR命令或协议中,地址和数据输入被锁存在时钟的上升沿输出,而数据在时钟的下降沿输出。在DTR命令或协议中,地址和数据输入在时钟的两个边沿被锁存,并且数据被锁存且在时钟的两个边沿输出。

RESET# 复位管脚

HOLD# 保持管脚,暂停通信,输入被忽略。

W# 输入写保护

DQ[3:0] 数据IO,当在扩展I/O协议(XIO‑SPI)中使用传统 (x1)SPI命令时DQ0是输入和DQ1是输出。不使用DQ[3:2]。 当在XIO‑SPI 中使用双命令或使用DIO‑SPI时,DQ[1:0]为I/O。DQ[3:2]不是 用过的。 当在XIO‑SPI中使用四指令或使用QIO‑SPI时,DQ[3:0]是I/O。

注意,带#的是低电平有效

注意,RESET#、HOLD#、W#这几个管脚与DQ复用,我程序中用的普通SPI,那么未用到的DQ2和DQ3都是驱动为高电平。

三、存储容量

擦除最小单位为4KB子扇区,读写最小单位为1页,256个字节。

四、操作命令顺序

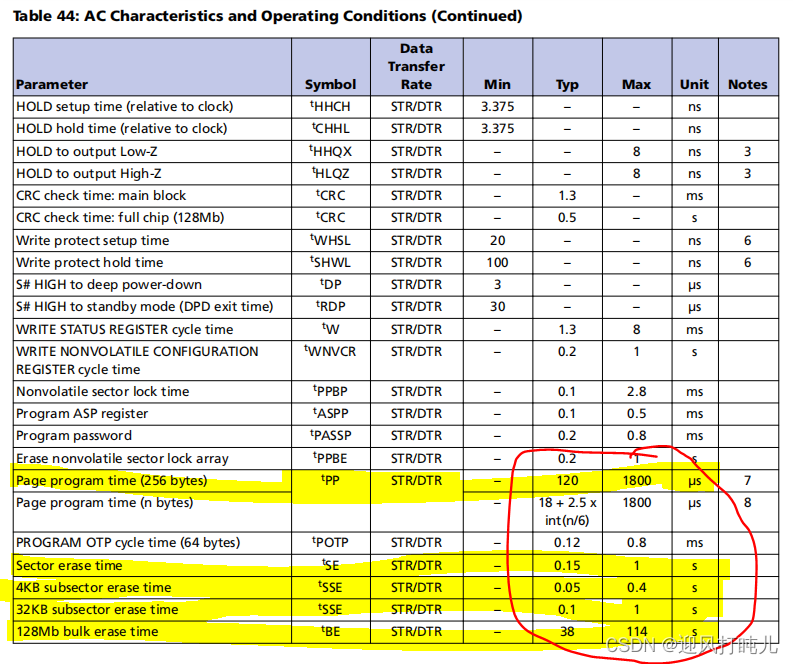

在进行擦除命令和写数据命令之前要进行使能,读不需要使能,随时都可以读,但需要注意,每次只能操作一个命令。在擦除和写之后要查看状态寄存器,因为擦除和写命令及数据发送完成后需要等待一定时间芯片方可真正完成擦除和写入。

如图所示,写和擦除均需要时间。我们会发现全擦至少要38s,不建议全擦,建议写哪里擦哪里。

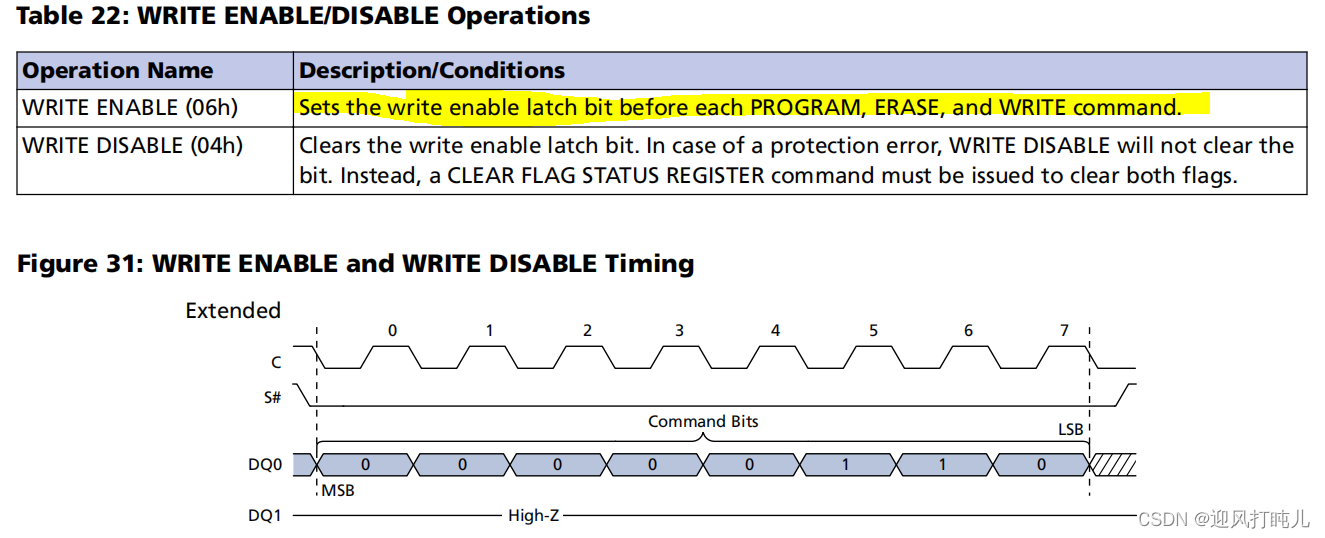

五、使能命令(06h)

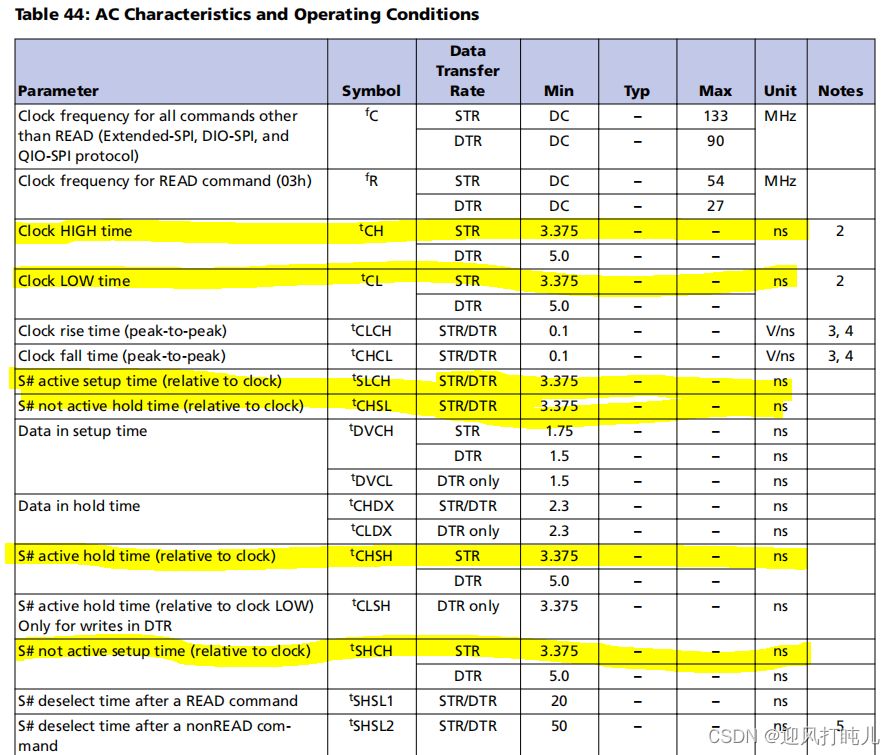

注意,这里面会有一些时序要求。比如时钟高低电平持续时间,比如相对于时钟,片选有效建立时间等等。

时序要求具体可参照芯片手册中提供的时序图。

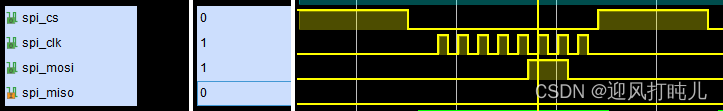

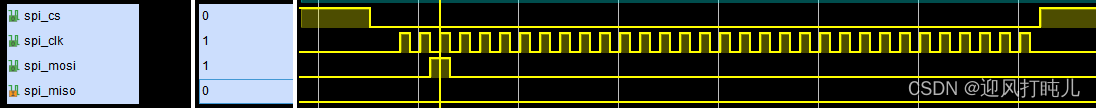

FPGA操作该命令时序图如下:

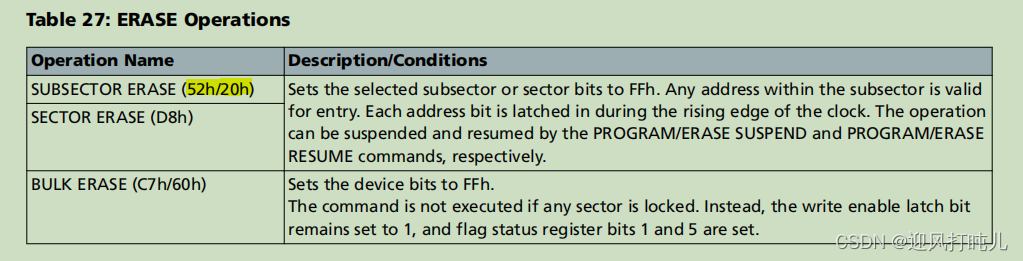

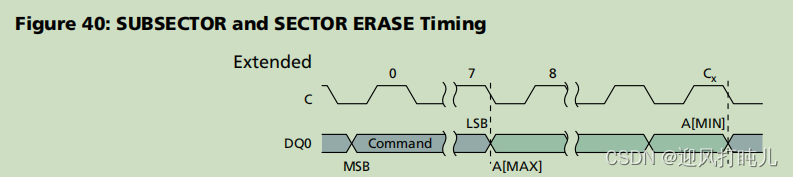

六、4KB区块擦除命令(20h)

52h和20h都可以。

FPGA操作该命令时序图如下(擦的地址为24'h000000):

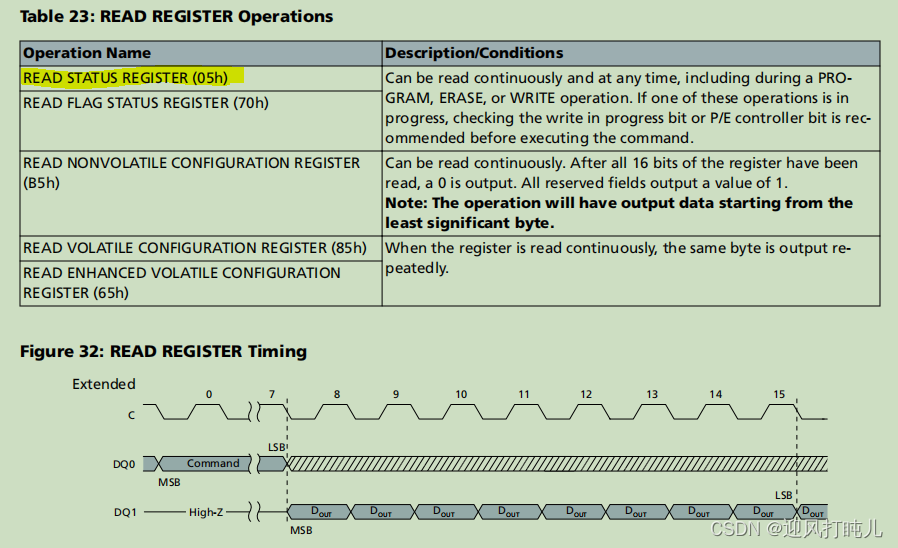

七、轮询指令(05h)

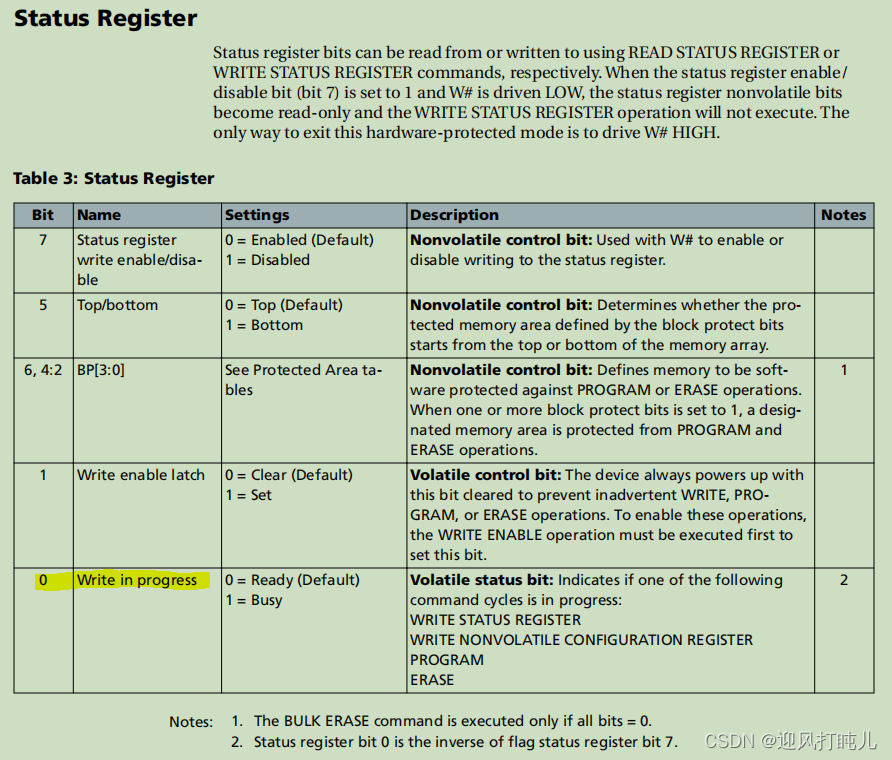

我们先来看一下状态寄存器,只用关心第0位,该位为0,说明可以执行擦除和写的命令,为1说明写和擦除正在进行中。

轮询指令就是用来查状态寄存器,它会一直循环读出状态寄存器的8bit值,我们如果发现最低位为0则可以通过控制时钟信号停止读取。

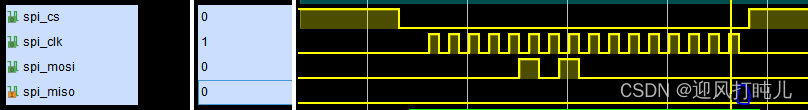

FPGA操作该命令时序图如下:

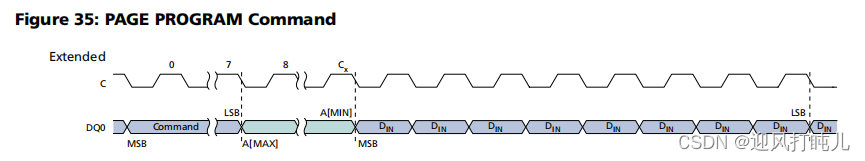

八、页写指令(02h)

先发命令,再发地址,再传数据。

FPGA操作该命令时序图如下:

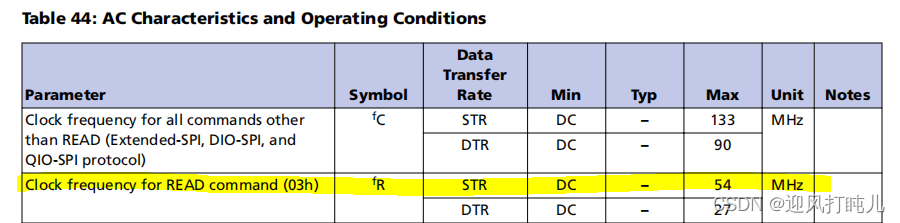

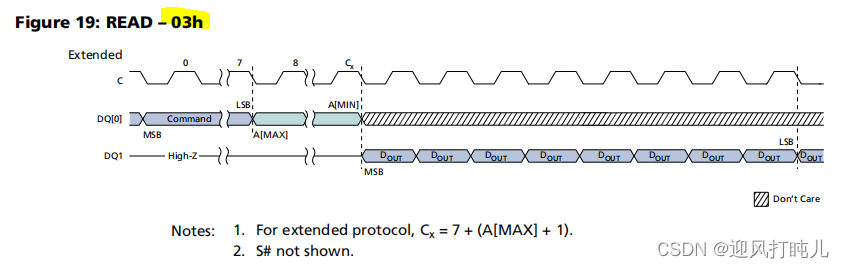

九、页读指令(03h)

我用的03h这个命令,最大速率可达54MHz,当然实际中用的25MHz。

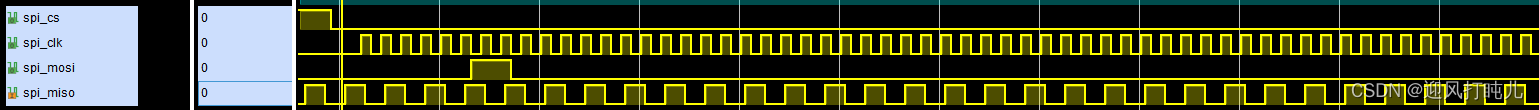

FPGA操作该命令时序图如下:

十、SPI时序

SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制从设备 (Slave)。一个 Master 设备可以通过提供 Clock 以及对 Slave 设备进行片选 (Slave Select) 来控制多个 Slave 设备, SPI 协议 还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给Slave 设备, Slave 设备本身不能产生或控制 Clock, 没有 Clock 则 Slave 设备不能正常工作。

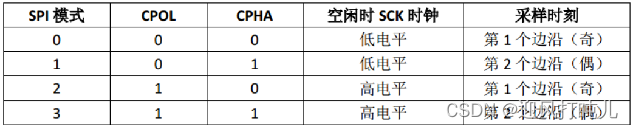

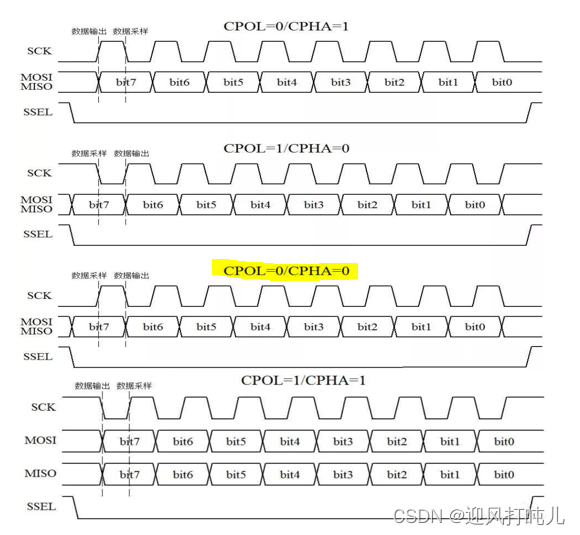

极性全称Clock Polarity,通常简写成CPOL。它是指时钟信号在空闲状态下是高电平还是低电平,当时钟空闲时为低电平即CPOL==0,反之则CPOL==1。

相位全称Clock Phase,通常简写成CKPHA。它是指时钟信号开始有效的第一个边沿和数据的关系。不管是时钟的上升沿采样还是下降沿采样,采样边沿为了满足建立时间和保持时间一般都是在数据稳定周期的正中间发生触发采样。因此当时钟信号有效的第一个边沿处于数据稳定期的正中间时我们定义CKPHA==0,反之时钟信号有效的第一个边沿不处于数据稳定期的正中间我们定义CKPHA==1。这样当CKPHA==0模式时我们先发生数据采样然后输出数据,当CKPHA==1模式时我们先发生数据输出然后进行数据采样。

SPI四种模式,我用的模式0。

参考资料

链接:https://download.csdn.net/download/m0_66360845/88962177

总结

以上就是今天要分享的全部内容,本文说明了如何配置MT25QL128ABA这块FLASH芯片,包含对相关指令的解析和读写操作需要注意的点,也给出了仿真图,当然,对于该FLASH的读写程序在实际中也已经验证通过了。