- 1OpenAI 再革程序员的命,GPT 给自己改 Bug!

- 2Appium+Python+pytest自动化测试框架的实战_python3、pytest+appium进行微信小程序ui自动化测试架构设计

- 3软件项目管理过程_软件项目管理过程各阶段的主要任务是什么?

- 4NLP入门之中文分词

- 5SQL之exists、not exists

- 6AIGC底层技术之大模型量化分析

- 7【IT人沟通技巧】如何学会结构化倾听_结构化倾听的案例

- 8万字总结Keras深度学习中文文本分类_r中keras处理中文文本

- 9Python爬取44130条用户观影数据,分析挖掘用户与电影之间的隐藏信息!_根据用户之前观影记录、提问记录或用户提供的反馈分析用户的观看习惯、历史记录以

- 102024华中杯C题光纤传感器平面曲线重建原创论文分享_基于光纤传感器的平面曲线重建算法建模模型假设

基于DRAM的CIM电路架构设计3.积分器设计_全差分密勒运放

赞

踩

根据系统设计需求和组织安排,记录一下架构里全差分运放的设计与功能。

目标:

1.50dB全差分运放

2.10ns来一次输入信号进行积分

3.最终积分到目标值,并清零复位

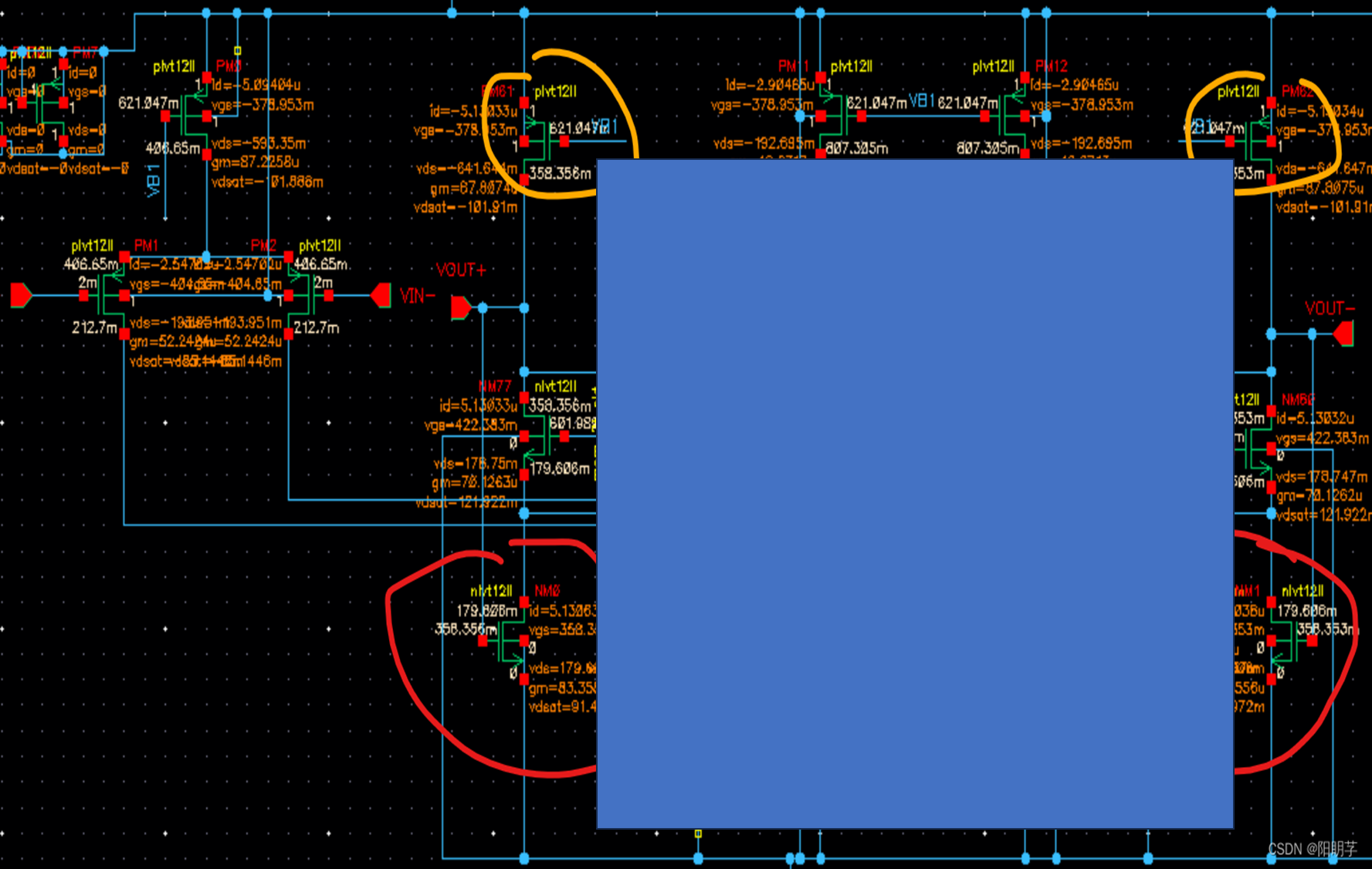

一、全差分运放设计

基于实验室师哥的运放直接拿来微调采用全差分的二级运放。第一级为共源共栅折叠运放,第二级。为共源极。结构中两级运放都通过mos管做了简单的共模反馈(这里的设计存疑)。右边为偏置电路,外部有电压基准源,因此这里只是三组简单的偏置电流镜。

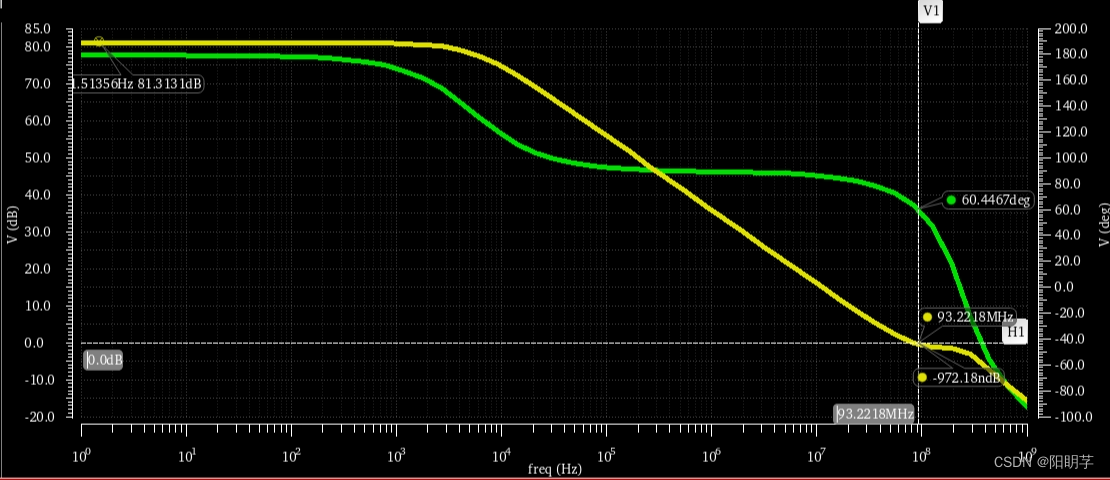

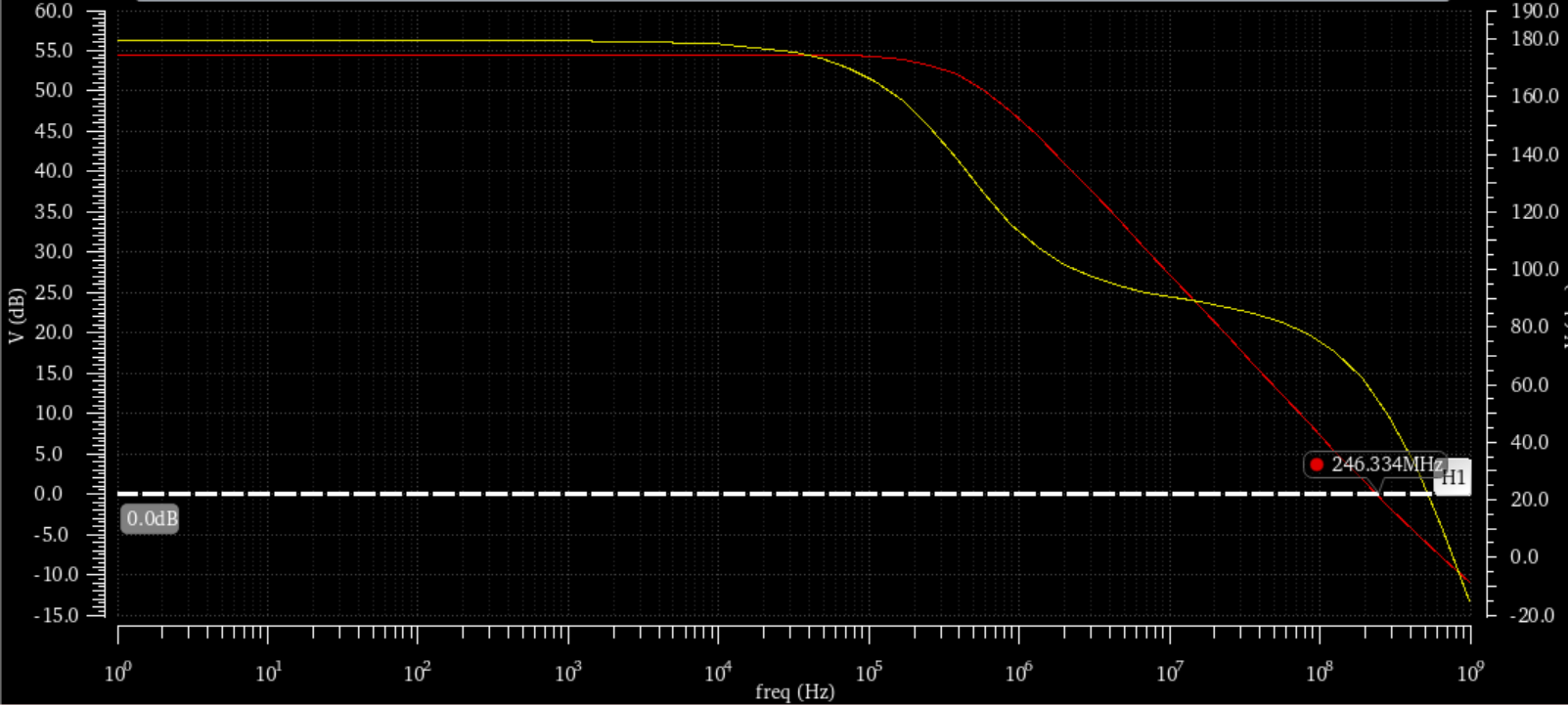

进行开环增益和相位裕度仿真,结果下

可以看到增益达到81.3dB,相位裕度60deg,增益带宽积大概100Mhz,而-3dB带宽甚至只有10kHz左右。这个带宽对于10ns的输入信号显然不太够,很容易失真。因此这里对阵列计算的输出结果需要延长保持时间或者增大运放带宽,考虑到增大带宽需要调管子参数,很麻烦。。。故最后让输入信号延长到100ns,其中90ns的积分时间和10ns的复位时间。高频信号同相叠加,则零点为左平面;高频信号反相叠加,则零点为右平面.右半平面零点会劣化相位而对增益的影响和左半平面相同。

因此从图中可以分析得知存在一个主极点,一个右半平面零点,以及一个次极点,其中右半平面零点在两个极点之间。这是可以遇见的,添加密勒电容后会引入一个右半平面零点。

对前面阵列计算的结果做了如下修改:

阵列是差分输出的,分别是V1,V0。第一个10ns进行数据写入,后面每100ns为一个周期进行积分运算,其中10ns为复位(这里应该是用来统计有多少个脉冲的,积分结果会略有衰减),90ns为实际积分时间,考虑到采样精度,最好稍晚一点测。之后进行多次循环,每次循环阵列都进行相同的计算,最后将积分结果除以次数得到一个较为准确的结果。后来经讨论后确定这种输入是有很大问题的。最大的问题就是积分器存在积分上限,即电源电压1V.而且跟前面的人沟通确认,输入信号其实是256个阵列通道,即每个通道才大概1/256V,故后面的验证采取小电压即可。

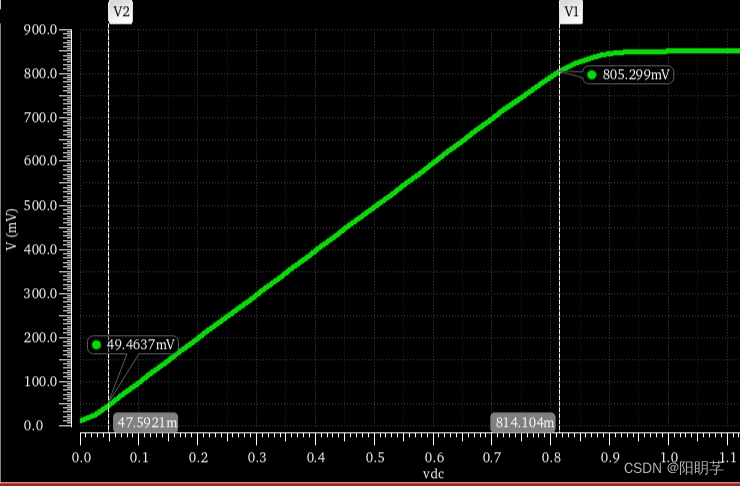

接着对输入共模范围进行仿真,结果如下:

线性范围大概在50mV-800mV。

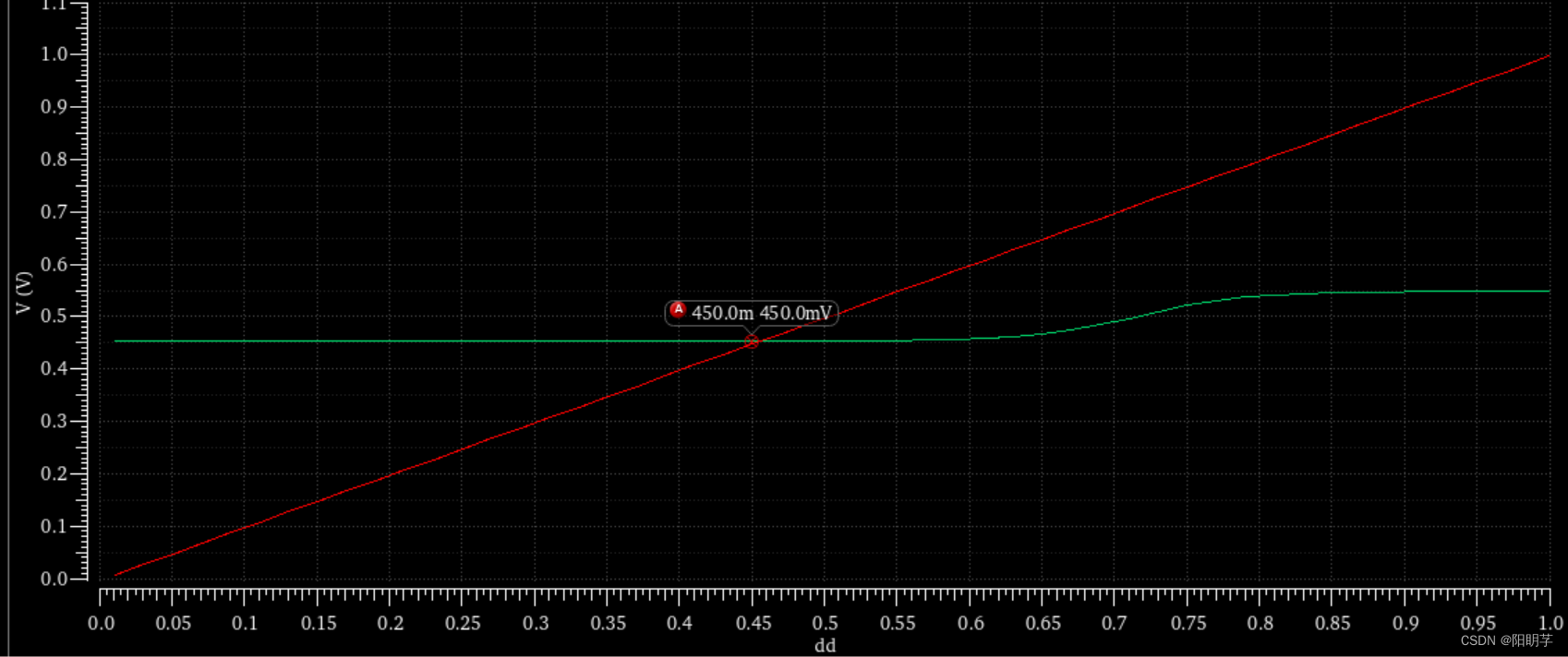

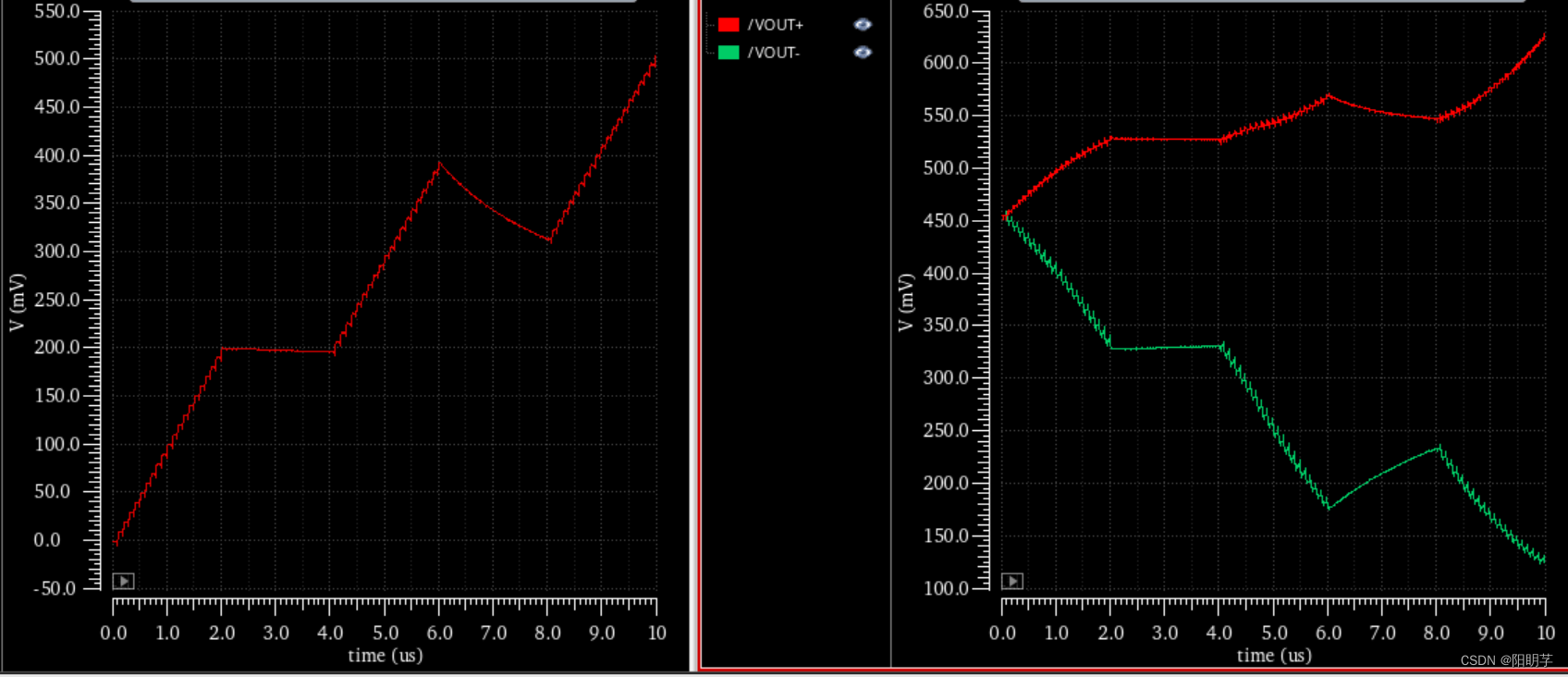

直流静态工作点约450mv。有意思的是绿线几乎是平的,看到电路内部可以发现这是由于反馈mos而被钳制了。

后来在画版图的时候发现这个电路的参数设计简直是灾难性的。。。。而且发现了一个电流镜复制的问题。有一个电流镜比例一开始是120n/1u,电流160n,复制10倍,且复制管为1u/1u,电流仿真结果是5.6u,按比例计算应该大概是12.8u,但当把两个管子调整为500n/500n,和10倍的500n/500n,结果却基本准确。这是为什么呢?

二、积分电路功能验证

然后我们对运放进行基本的积分器功能验证(即输入接电阻,负反馈接一个电容)。

结果显示极性可能接反了。

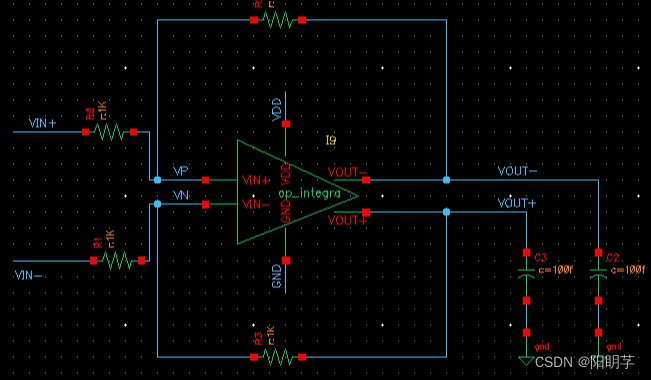

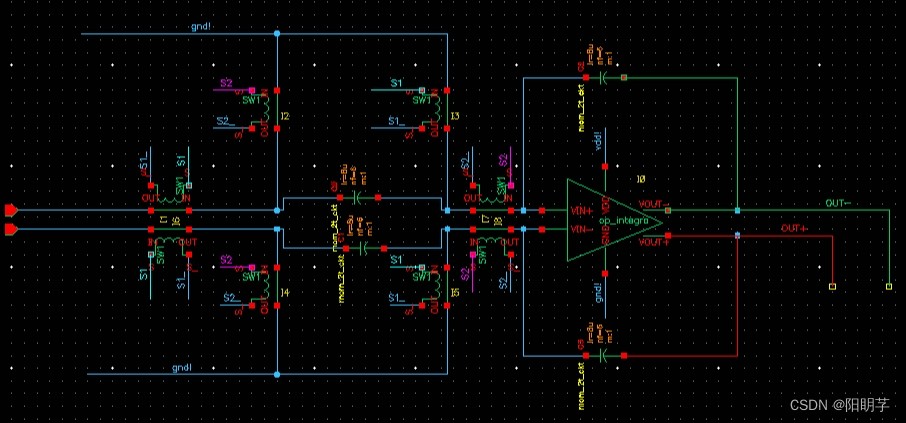

下面对实际积分电路进行仿真调整,原理图如下:

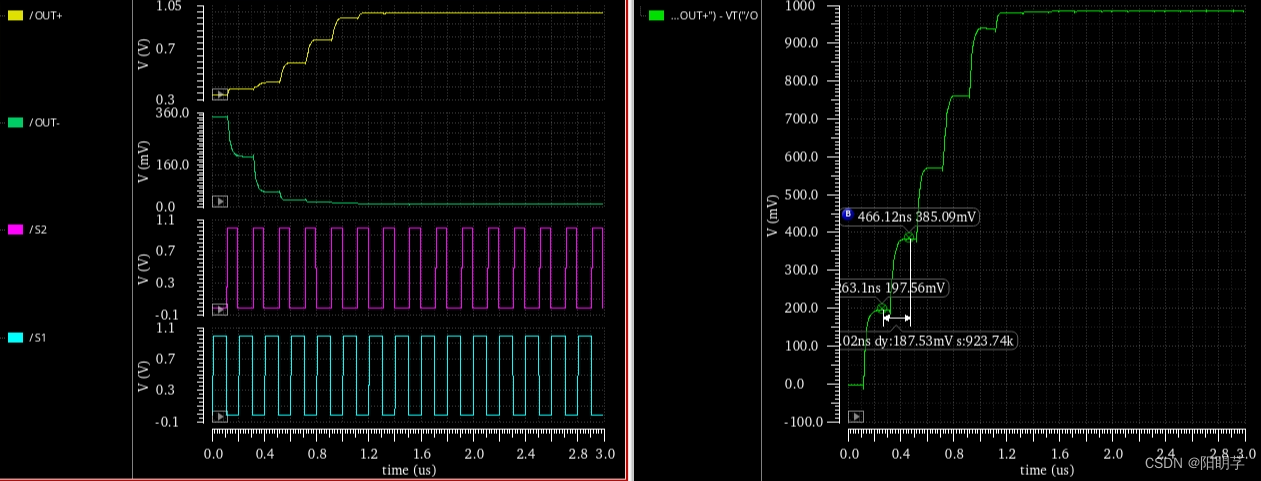

采用的最基本的全差分开关电容积分电路。电容都设置在10fF,正相输入端接0v,反相输入端接200mv,测试输出差模积分结果。先闭合开关S1让输入电容充电,然后断开S1,再闭合S2,将电荷转移到反馈电容,完成输出端的积分。最终输出结果基本准确,但可以发现随着积分次数的增加,精度逐渐下降。推测是由于开关电容的电荷注入效应以及失调电压和高频下增益下降造成的。对于高频下增益的下降需要增大带宽,这就需要调整运放的结构,emmm不是很愿意呢。失调电压做了仿真后发现很小,太大了的话可以采用失调存储来消除。至于电荷注入效应,这里采用互补的cmos开关来降低影响。分析来分析去,很显然调整带宽是最有效的。。。

这里有几个重要的设计点:两个开关的时序,电容大小,开关电容的电荷注入效应以及输入电压的大小。

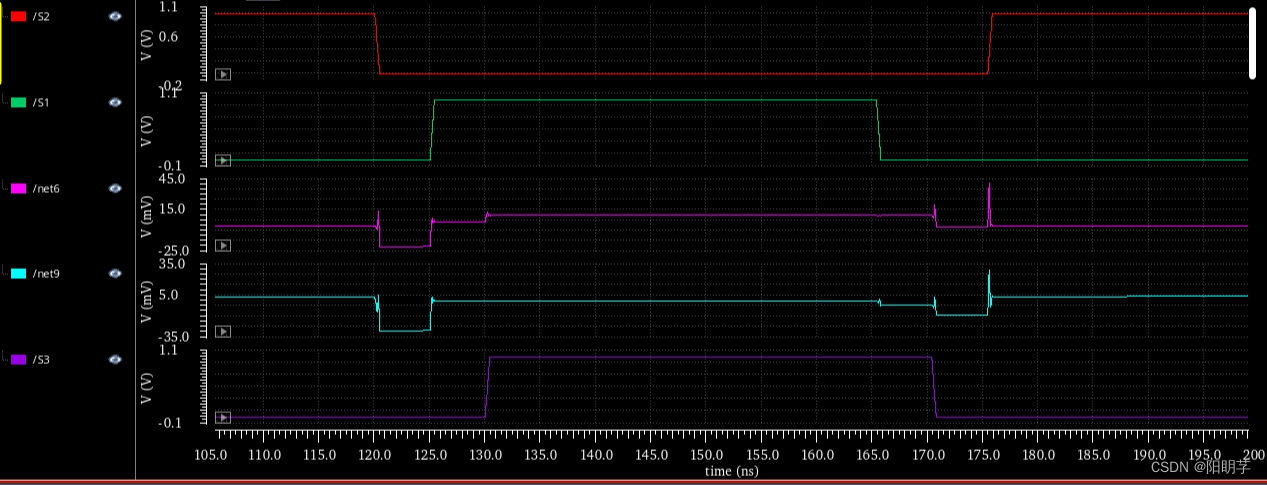

1.开关时序

积分器工作时,首先将S1闭合,对输入电容进行充电。然后断开S1,闭合S2,由于虚短虚地,输入电容两侧电压差变为0,故本来积攒的电荷会转移到反馈电容,引起输出电压变化。输入与输出电压关系为:

这里Cs为输入负载,Ch为反馈负载,输入电容反馈电容都暂定10fF用于初步仿真,也防止过度影响带宽,故输出电压差分积分值就等于输入电压差分值。

两个开关的时钟要注意两相不交叠,需要间隔一小段时间,以免同时闭合造成电荷泄露。因为方案里有要求积分器复位,所以这里设想可以在输出端和负相端之间连一个开关?或者内置一个复位信号?或者在输出端连接的负载电容另一端连接开关(这种方案估计会降低带宽,影响充放电)。

2.电容大小

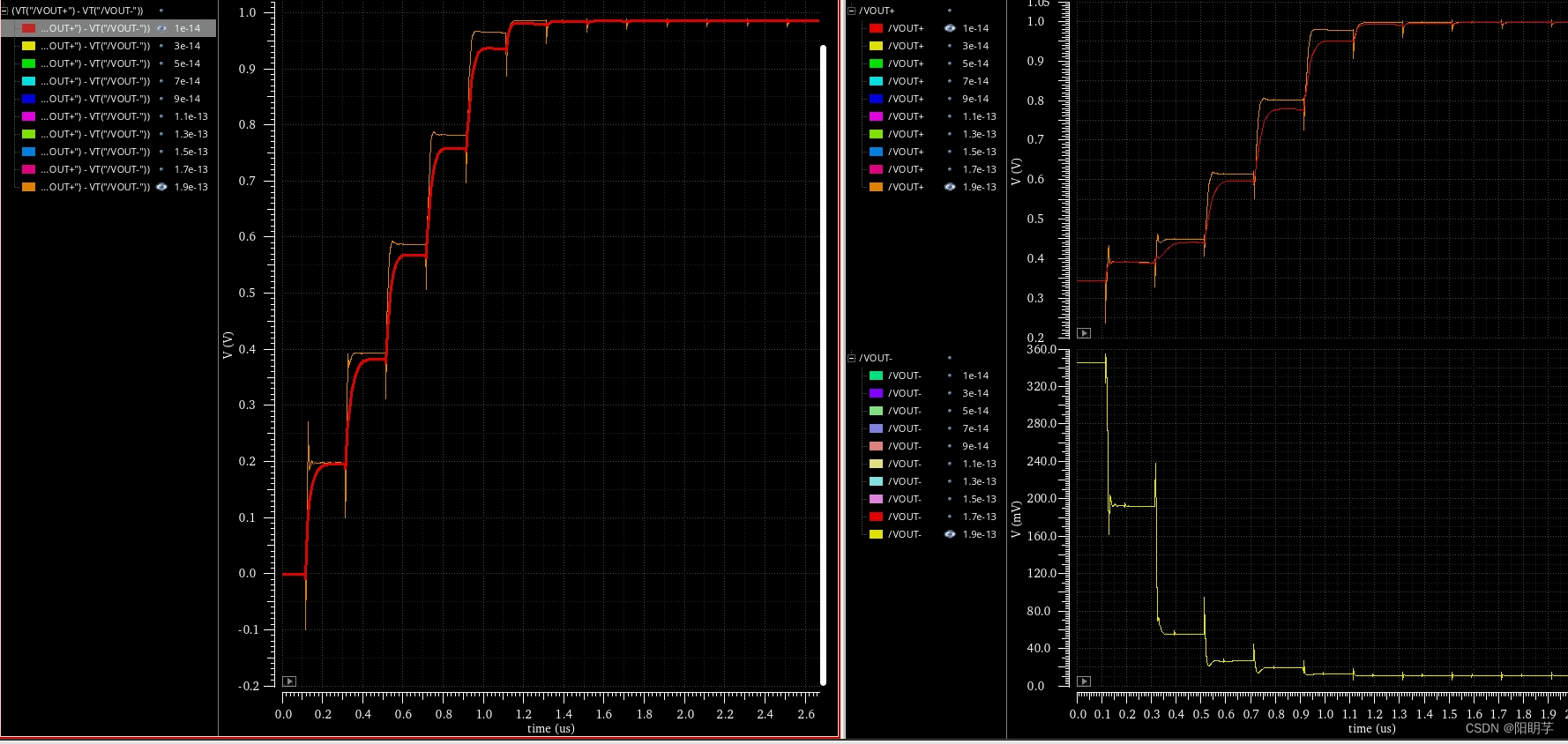

因为我们保证输入准确传导输出,所以输入电容和负载电容始终保持相同进行仿真。对C从10fF到200fF做参数仿真结果如下:

可以发现两点,首先是随着电容的增大,每次积分带来的电压抖动也变大,对于正相端先降后增,反相输入端先增后降,综合到差分输出的结果是先降后增,随着积分结果的变大,抖动几乎消除。

其次,随着积分次数的增加,每次积分量都会衰减,但C越大,衰减越小。根据一般的积分器公式,C越大,GBW越小,动态误差应该越大,这里让lz很疑惑。这里有个设想,电容小意味着等电压下存储的电荷少,容易受开关注入电荷影响。至于为何电容越小,充电越慢,这里留个问号

推导得到传输函数为

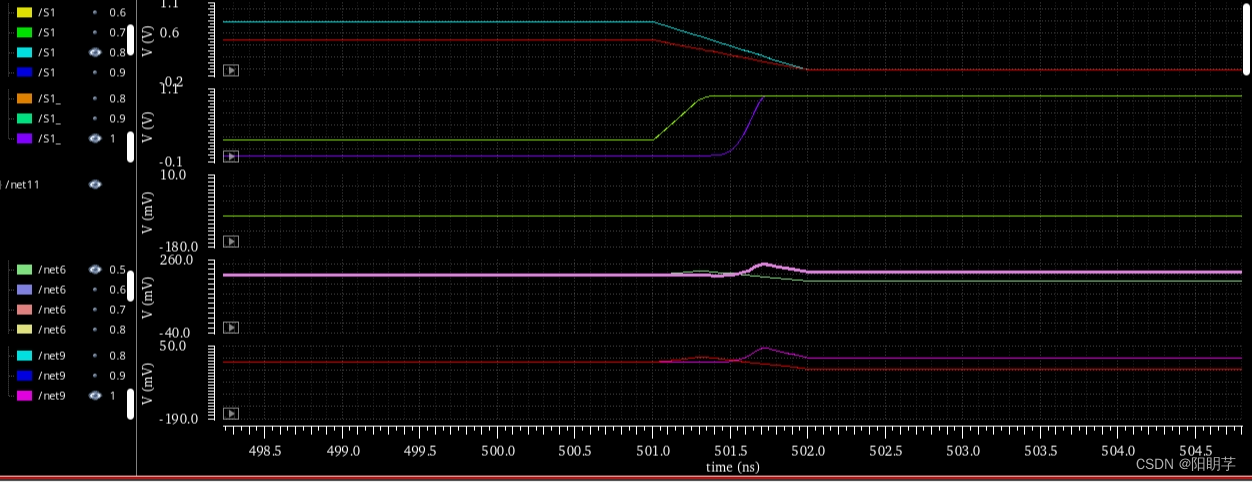

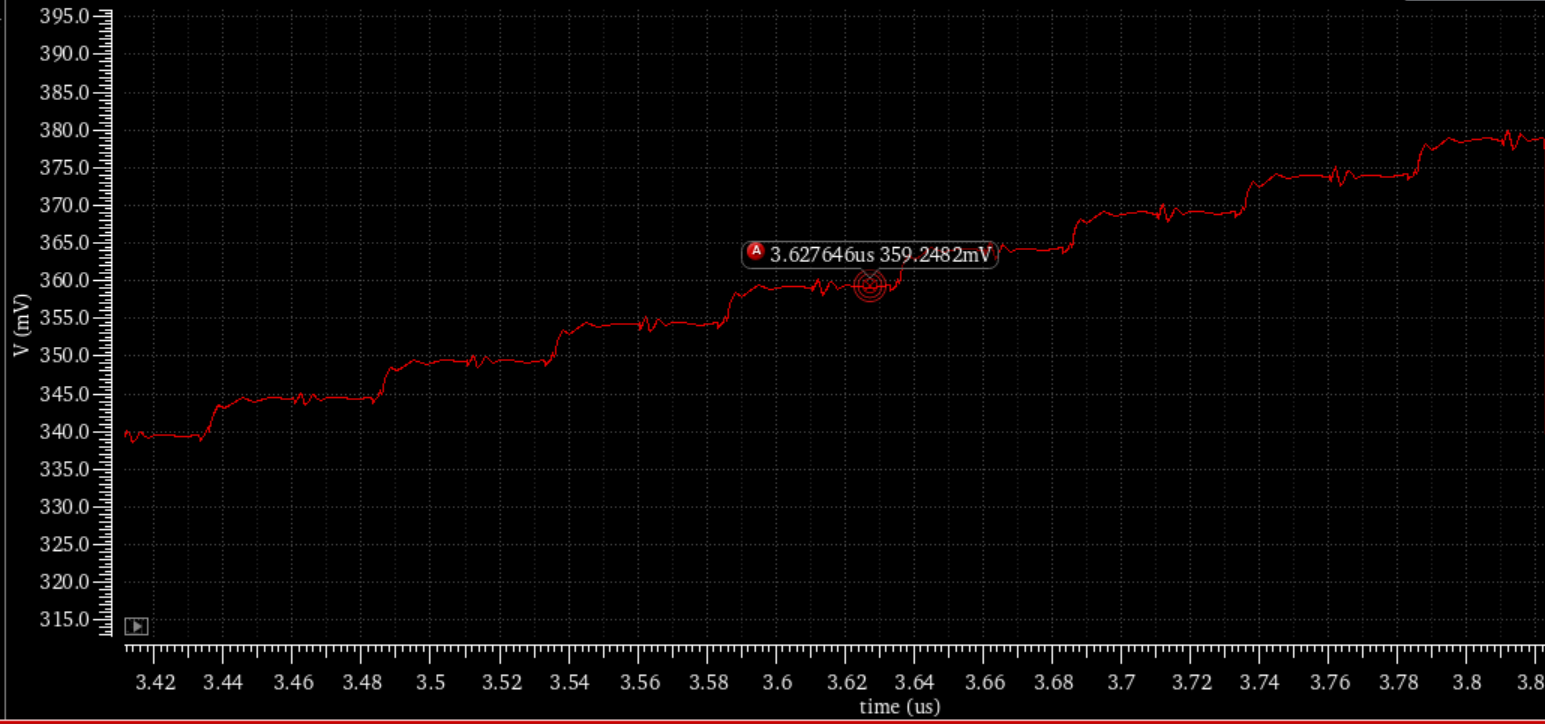

这里可以观察到电压会突然跳高,而且电容越大充电必然是越慢,所以大电容引起的误差这里推断不是因为电荷迁移,而是因为两侧电压的突变。lz这里初步推断,S2闭合后,Cs左电势从Vin降为0,引起Vp降低Vin,造成正相输出端电压下降。对正相单端进行仿真,得到结果如下:

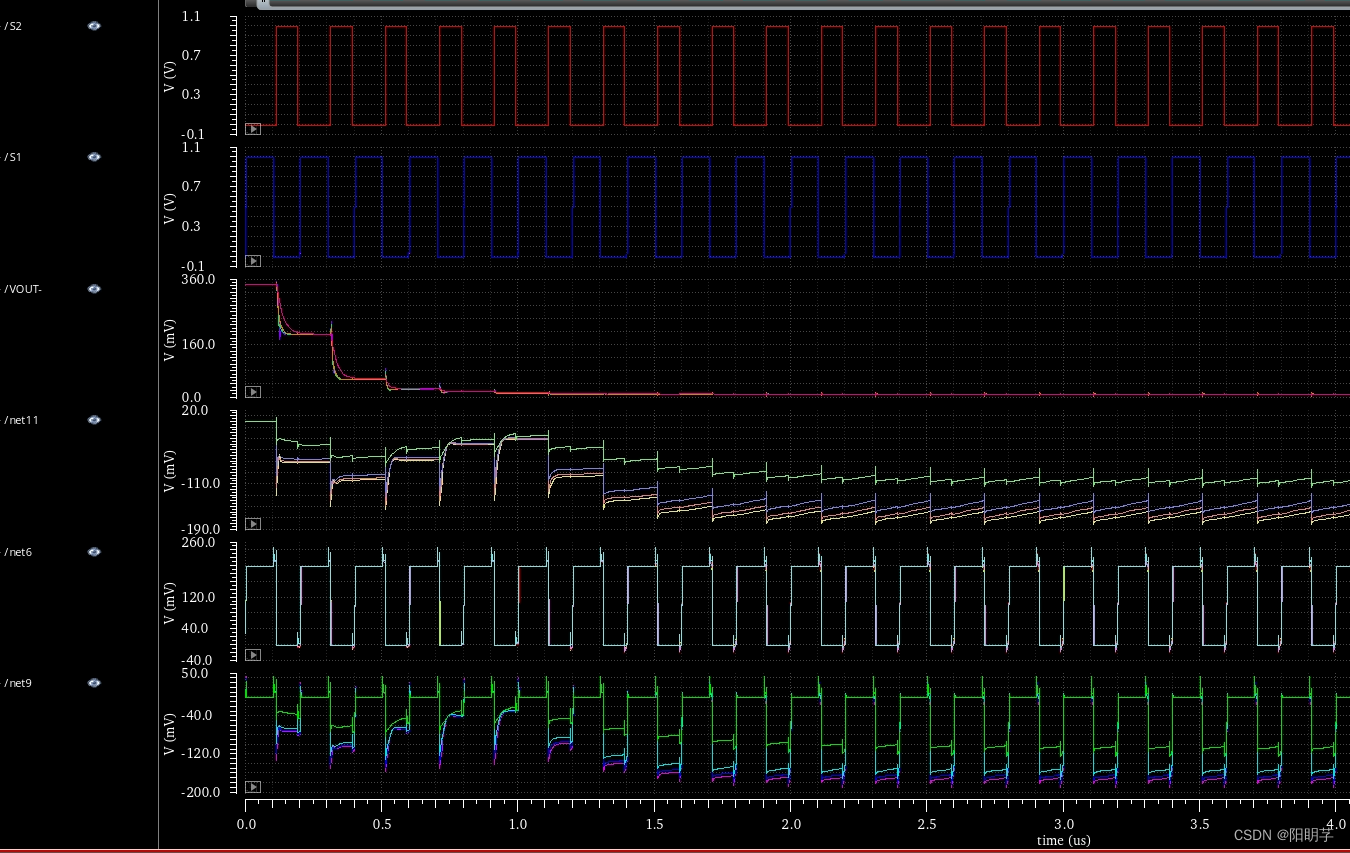

图中net11为负相输入端,net6为负相Cs左侧,net9为Cs右侧。可以发现,S1断开,会让net6有个突变(这里猜测应该是电荷注入效应),然后等待10ns,S2闭合,net6变为0,net9有个跟随net6的负跳变,但不等于-200mv,随着积分的增加,才会约为-200mv(电容如果小,则也会到不了),所以这里推测是受输出影响。

首先仿真下S1的电荷注入效应,从S1=1v图像可以发现很明显的电荷注入效应。而且由于S1和其反向信号S1_是由反相器得到的,因此会有延迟,这里的延迟应该是clk需要降到让pmos开启level所需的时间。当S1降低时,nmos慢慢关闭,而由于反相器的延迟,pmos还未关闭,因此输出信号几乎仍保持Vin。当clk达到足以使pmos开启,S1_才慢慢升高,开关里的pmos端关闭,注入正电荷,Vout,即net6升高,而clk同样也不需要完全降为0时才能让反相器完全反相,因此S1_又会更早地跳到高电平电源电压。之后nmos的负电荷注入占主导,net6微降低。很容易想到的是,反相器完全反向越快,nmos开关的影响时间就越长,net6就会更衰减。同样地,越慢则pmos的正电荷注入越明显。nmos引起的电压误差为。这里clk就是Vdd,为了降低误差应该降低clk。将clk从500mv从1v仿真。大概700mv左右注入的正负电荷可以抵消。因为正如前面所说,clk实际在一个更小的范围内就可以使反相器使能,因此反相器内部的电源保持1v,保证pmos开关即可。这样还省得调mos面积(乐)。对于S2的时序,由于是让电平降为0,所以可以暂时不管。此外这个误差公式也解释了为何电容越小,误差越大。

后续lz发现似乎这个思路有点问题,聚焦的应该是net6-net9的电压,而不只是net6。。。

两处S1开关同时关断会引起输入电容两边的电荷注入效应。net9处的与输入电压无关的电荷注入可以利用差分消除,但net6引入的电荷注入会再次干扰net9处的电压(因为此处S1开关还未完全关断)。因此这里可以分别用S1,S3控制net9,net6的关断,让net9稍早关断,这样即使net6有电荷注入,因为net9处是断掉的,电荷没有流入途径,所以并不会影响运放的输入(引入的电荷注入会被暂时转移到寄生电容等处,待S2闭合,即会流入地)。这里lz让S3稍早5ns关闭。事实上,lz先是尝试了利用反相器的延迟生成S1 S3,可后来发现正如前文所讲的问题,这会造成互补开关的不同时关断,且因为是反相器生成的S1控制信号,而电源又是固定1v的,就不能通过控制clk来让nmos和pmos的注入抵消。所以,还是分了两个时序。后面根据实际需求修改了下仿真时间,100ns一个周期,并把输入电压改为10mv。

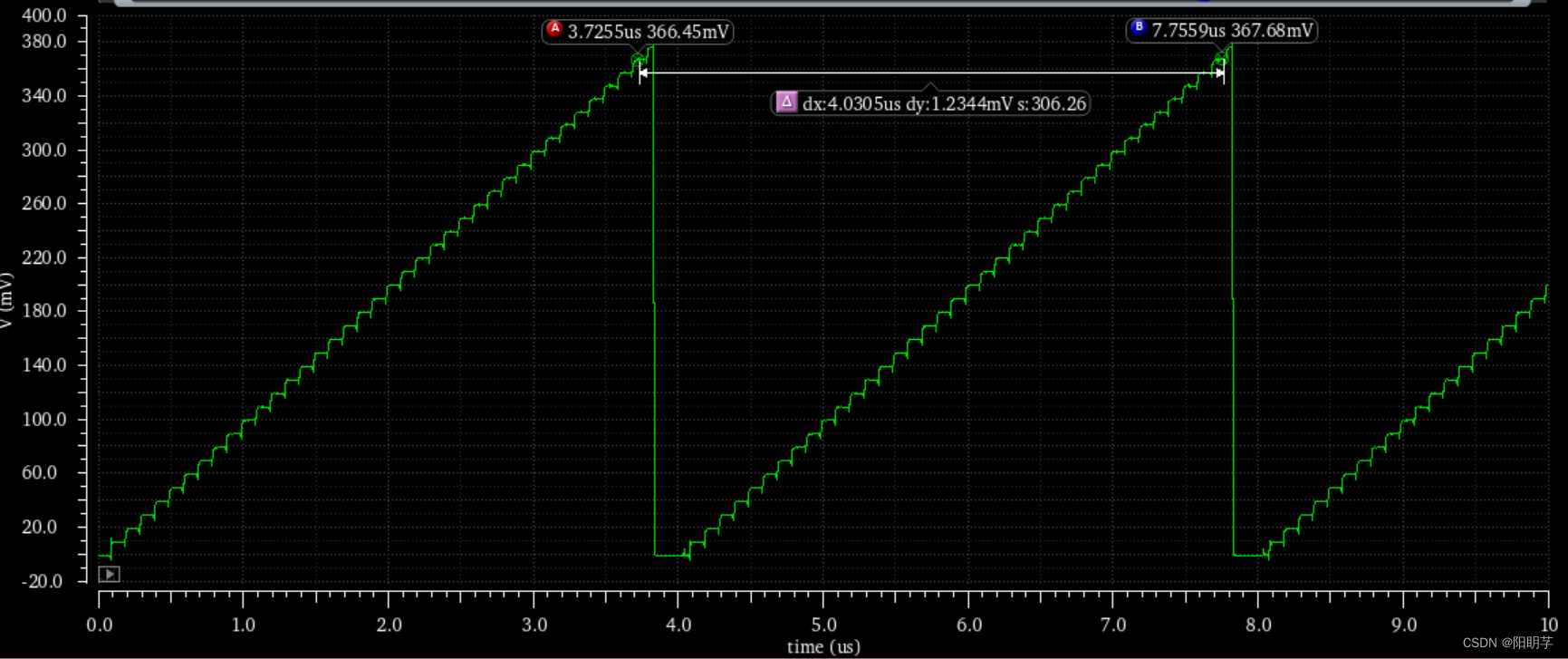

重新仿真后得到如下结果:

发现net6受nmos负电荷注入影响很大,与net9的差完全偏移10mv很多(这个时间段大概只有6mv),因此去修改cmos互补开关的pmos管大小或者clk信号的大小,让pmos关闭的更晚一些从而让nmos的注入时间减少。考虑到最后的电源管理,clk尽量还是保持1v。这里有个有意思的点,S3关断的时候net6会受电荷注入影响,但net9同样也降低了,而且取点得知电压差是要比S1刚关断时大,也即是说;又有负电荷注入了net9,最终总注入要比net6多,因此总电荷降低了。由于差分结构,理想情况下这个误差应该被消去,而且本身输入很小的情况下,这个输入误差就更容易通过时序抵消了,最终输出的结果也表明影响并不大。实际上,开头积分几乎没有误差,这就表明电荷注入的影响是很小的,更多的是受输出值的影响。(哭死。。。)。

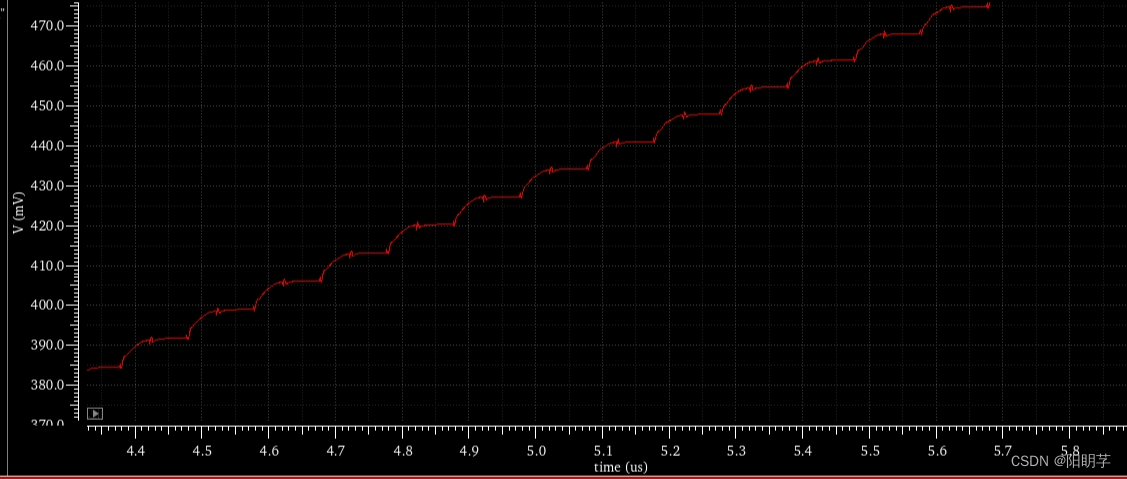

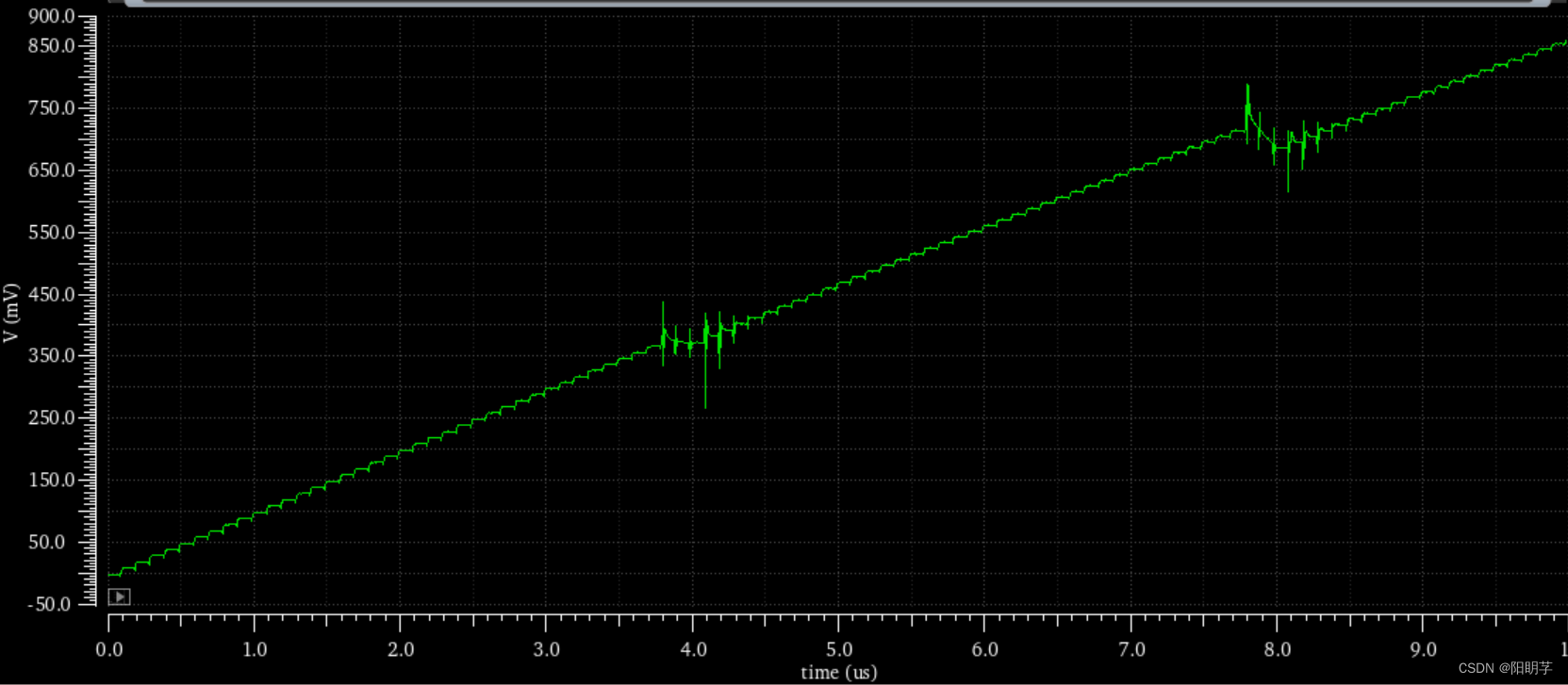

通过增大电容,积分的电荷数更多,因此抵抗误差越好。这里取100f,积分60次后结果大概530mv。开始积分结果还正确,但到后面大概每次只有7mv。那如果是带宽问题,应该一开始就会有误差呀?然后lz经高人指点,意识到是不是输出摆幅不够啊。。。

很明显发现,负端的电压下不去了!哦fuck。

下面开始调整运放的静态工作点。

再次回到原理图,想要调整输出端的静态工作点,则要从pmos电流镜的漏断入手。注意到,输出端接回了共源极下面的反馈mos栅极。仿真发现输出端静态工作点更多地受反馈管影响,这点其实是比较直观的,考虑沟道调制效应,pmos管显然漏源偏压更大,因此有足够多的裕度去补偿电流变化(既然电流镜很难复制过来,那这个运放的设计流程有待商榷,或者说这个反馈管有必要吗。是否可以用CMFB?占面积,本次设计面积裕度很小)。也即是说,应该要让支路电流增加,就可以增大反馈管的栅极电压。一方面增大pmos宽长比,另一方面减小nmos反馈管宽长比。但这又有个问题,电源电压因为是1V,因此输出摆幅很小,而且这里也不是轨至轨的设计,本身输出也达不到很大,也就是说很容易使nmos进入线性区(比方说,栅压500mv,过驱100mv,阈值电压100mv,那么nmos的vds为400mv=500mv-100mv=Vov)。因此这个运放的参数调整是有很大问题的。。。仿真发现增益和裕度倒还好,所以先基于此调整输出吧= =最终将输出调整到450mv,增益87dB,裕度72°。

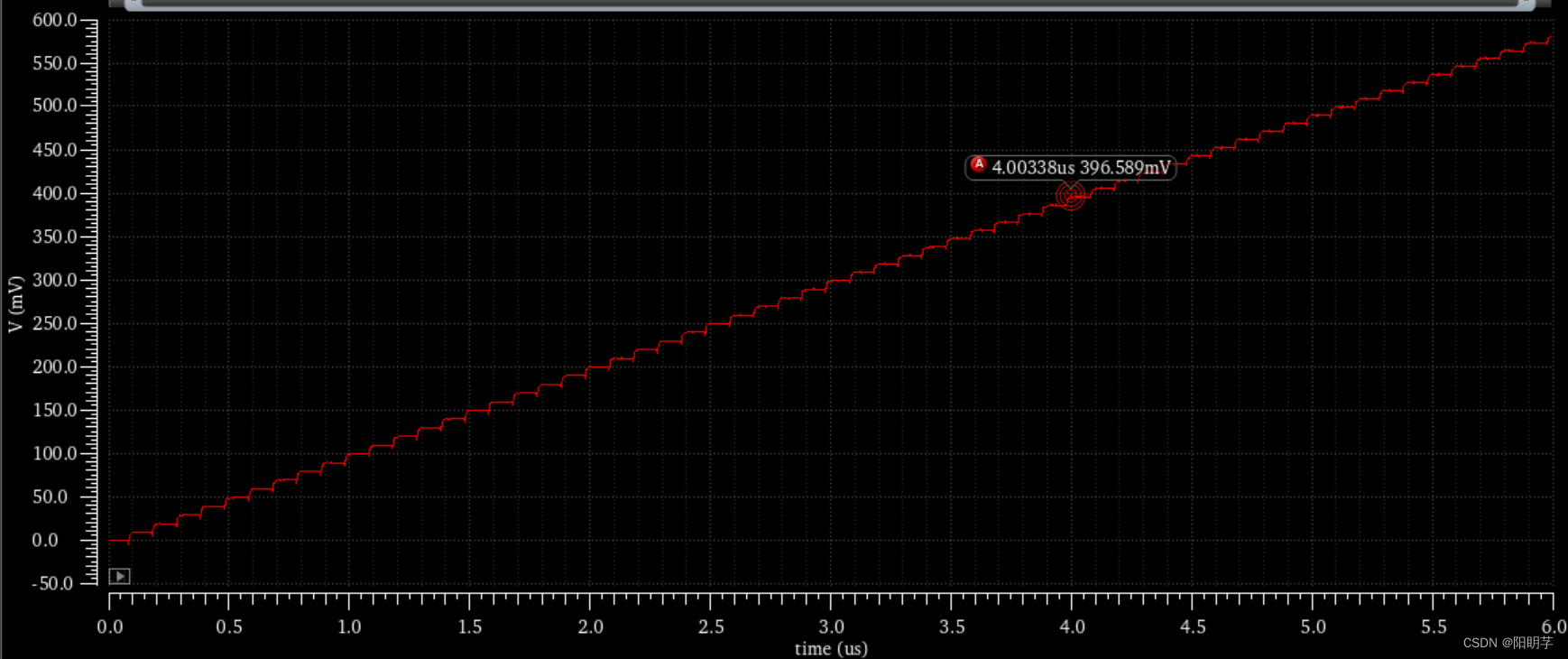

再次仿真积分器结果如下:

以4us处为例,理想结果是400mv,实际为397mv,在可接受范围内。

下面考虑复位功能,这里lz初步想了三种方案:

1.在运放输入和输出之间加开关,达到积分次数后闭合开关,将输出的差降为0

2.在运放输入端额外接入电源提供静态工作点

3.输出端接开关接地,达到积分次数后闭合

对于方案1,不需要额外电源,但可能每次积分初始状态会有误差。对于方案2,会要求额外功耗,但每次结果会更准确。对于方案3,可以让积分复位地更准确,但要考虑输出电容等带来的问题。

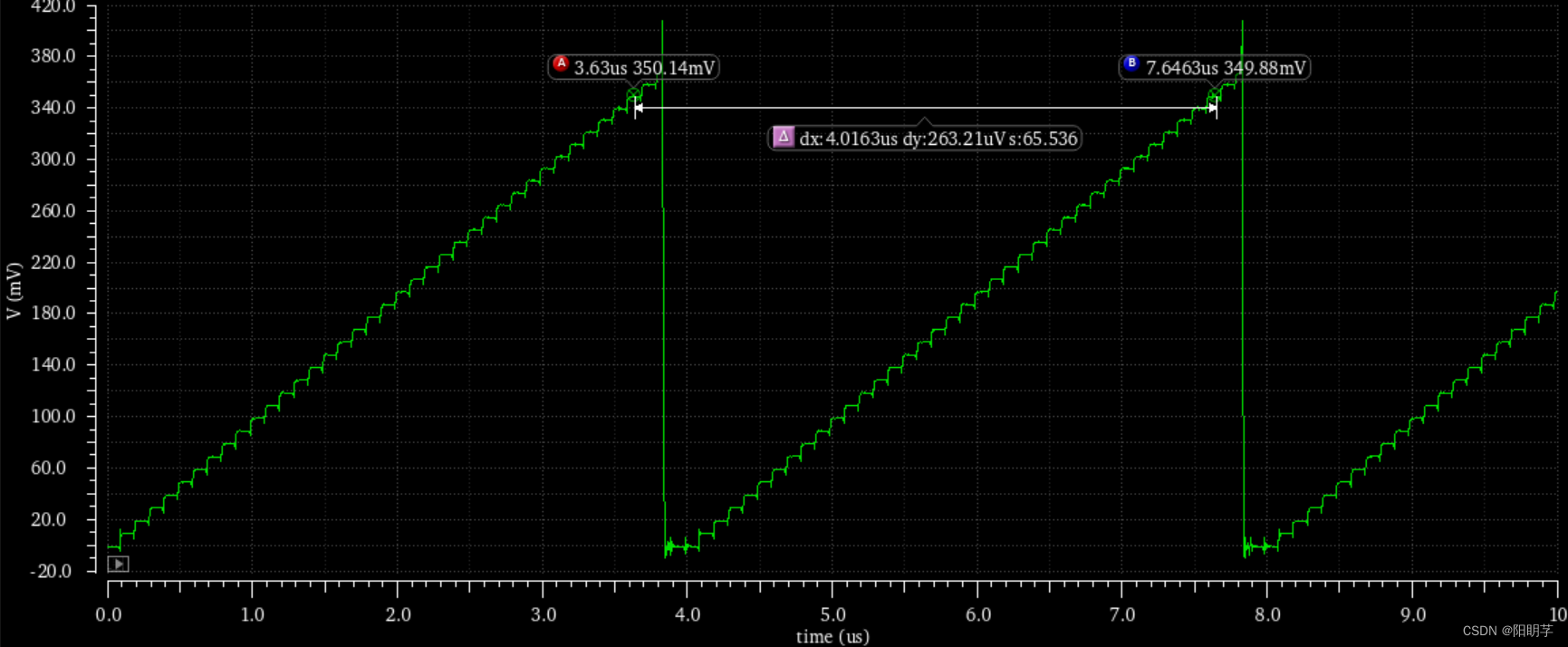

这里先对方案1进行仿真验证,设置开关为4us宽,闭合时间200ns,结果如下:

可以发现在开关没有闭合的时候积分就出现了比较大的误差(10mv),这里认为是因为开关并不是理想的,因此每次积分都会有电荷从输入和输出之间的开关流动,造成了误差。

再对方案2进行仿真,脉冲开关频率相同:

结果没有复位。因为输出端并没有地方释放电荷。可以调整接入的静态输入工作点以及多次开关并在复位阶段将前面的开关全都断开,但这会带来更多的功耗,效率很低,而且推测其实输出是降不到0的,而是跟第一次复位差不多的位置。故不采用这种方案。

最后对方案3进行仿真:

一开始只在输出端接开关时每次复位后初始积分会变为50mv而不是0v,后经过检查发现是输入静态工作点因为电荷的转移不相等了(正负相输出端接地后的衰减差与原来积分时的变化差不等),因此又额外在正负相之间接入开关,周期与输入端开关相等,误差大概在3mv。

三、补充

后来在画版图的时候发现BANDGAP的设计简直是灾难级的,参数设计很差,占用了很大额外面积而且不好画。因此一定要引以为鉴,在设计原理图的时候就要想要后续版图如何画。

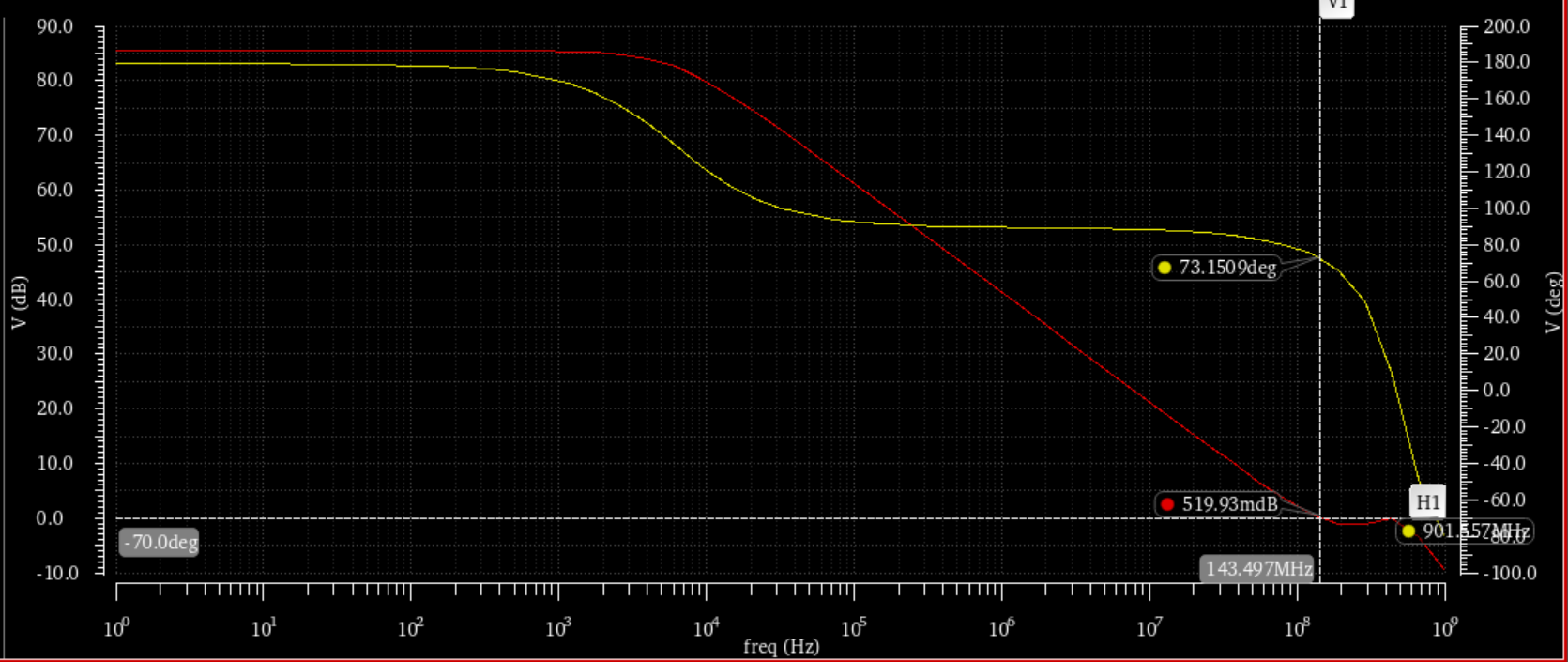

在去掉一个模块并且修改参数后,积分器效果显著上升。从性能特性表征来讲,输入信号和外围电路没变,bandgap主要影响运放的偏置电压,反映到性能上就是运放的增益、带宽等参数。观察带宽发现显著上升,但增益下去了,由于版图已经画完,后续再改进吧。。。

哦凑,放错了,这个是BG内部的运放,理论上应该也要增益大点。

哦凑,放错了,这个是BG内部的运放,理论上应该也要增益大点。

对比前面,积分效果很好。

看了下运放性能,对比前面的,93M→143M,60deg→73deg,80db→85db。从内部结构来看,bg只是提供一个vbias,到运放里,影响的就是偏置电路