- 1【Linux】权限管理(文件的访问者、类型和访问权限,chmod、chown、chgrp、umask,粘滞位)

- 2AI算法面试题总结三(计算机视觉)_ai视觉识别 算法模型选择

- 32023 年四川省职业院校师生技能大赛(中职组)网络建设与运维赛项(样题)——网络建设与调试、服务搭建与运维_四川 中职 网络建设与运维 赛题

- 4Java之加互斥锁_为对象加互斥锁

- 5二维小波变换_【外文文献速读】实时二维水波模拟

- 6Android权限系统(三):运行时权限检查和申请,PermissionController_android根据包名检查和设置权限

- 7正规表达式2

- 8iphone html5 模板,聊聊IPHONE6分辨率与适配

- 9大模型“暴力计算”时代,华为昇腾如何突围算力之困? | WAIC2023

- 10上职高学计算机可以考师范大学吗,职业高中也可以考大学,你知道吗?

FPGA(基于xilinx)中PCIe介绍以及IP核XDMA的使用_xilinx pcie

赞

踩

Xilinx中PCIe简介以及IP核XDMA的使用

例如:第一章 PCIe简介以及IP核的使用

一、PCIe总线概述

1.PCIe 总线架构

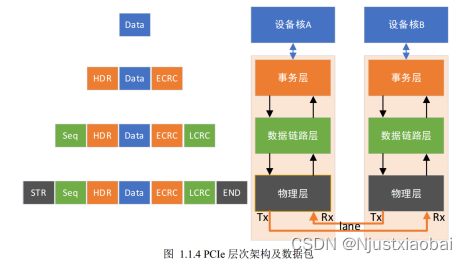

PCIe 总线架构与以太网的 OSI 模型类似,是一种分层协议架构, 分为事务层(Transaction Layer)、 数据链路层(Data Link Layer) 和物理层(Physical Layer)。 这些层中的每一层都分为两部分:一部分处理出站(要发送的)信息,另一部分处理入站(接收的)信息。

事务层

事务层的主要责任是事务层包 TLP(Transaction Layer Packet)的组装和拆卸。 事务层接收来自 PCIe 设备核心层的数据,并将其封装为 TLP。 TLP 用于传达事务,例如读取和写入,以及确定事件的类型。事务层还负责管理 TLP 的基于信用的流控制。 每个需要响应数据包的请求数据包都作为拆分事务实现。每个数据包都有一个唯一标识符,该标识符使响应数据包可以定向到正确的始发者。数据包格式支持不同形式的寻址,具体取决于事务的类型(内存、 I/O、 配置和消息)。数据包可能还具有诸如 No Snoop、 Relaxed Ordering 和基于 ID 的排序( IDO)之类的属性。事务层支持四个地址空间:包括三个 PCI 地址空间(内存、 I/O 和配置)并添加消息空间。该规范使用消息空间来支持所有先前 PCI 的边带信号,例如中断、 电源管理请求等,作为带内消息事务。

数据链路层

数据链路层充当事务层和物理层之间的中间阶段。数据链路层的主要职责包括链路管理和数据完整性,包括错误检测和错误纠正。数据链路层的发送方接受事务层组装的 TLP,计算并应用数据保护代码和 TLP序列号,以及将它们提交给物理层以在链路上传输。接收数据链路层负责检查接收到的 TLP 的完整性,并将它们提交给事务层以进行进一步处理。 在检测到 TLP 错误时,此层负责请求重发 TLP,直到正确接收信息或确定链路失败为止。数据链路层还生成并使用用于链路管理功能的数据包。为了将这些数据包与事务层( TLP)使用的数据包区分开,当指代在数据链路层生成和使用的数据包时,将使用术语“数据链路层数据包( DLLP)”。

物理层

PCIe 总线的物理层为 PCIe 设备间的数据通信提供传送介质,为数据传送提供可靠的物理环境。 物理层包括用于接口操作的所有电路,包括驱动器和输入缓冲器、 并行至串行和串行至并行转换、 PLL 和阻抗匹配电路。它还包括与接口初始化和维护有关的逻辑功能。物理层以实现特定的格式与数据链路层交换信息。该层负责将从数据链路层接收的信息转换为适当的序列化格式,并以与连接到链路另一端的设备兼容的频率和通道宽度在 PCI Express 链路上传输该信息。

在PCIe总线的物理链路的一个数据通路(Lane)中, 有两组差分信号,共4根信号线组成。其中发送端的TX与接收端的RX使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX与接收端的TX使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。

目前PCIe链路可以支持1、 2、 4、 8、 12、 16和32个Lane,即×1、 ×2、 ×4、 ×8、 ×12、 ×16和×32 宽度的PCIe链路。每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

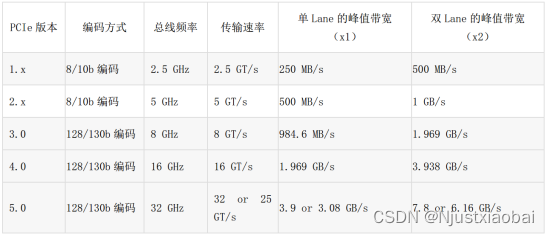

2.PCIe 不同版本的性能指标及带宽计算

GT/s——Giga transation per second(千兆传输/秒),即每秒内传输的次数,重点在于描述物理层通信协议的速率属性,可以不和链路宽度等关联。

GT/s——Giga transation per second(千兆传输/秒),即每秒内传输的次数,重点在于描述物理层通信协议的速率属性,可以不和链路宽度等关联。

Gbps——Giga bits per second(千兆位/秒)。 GT/s与Gbps 之间不存在确定的比例换算关系,要根据线路编码方式而定。

吞吐量 = 传输速率 * 线路编码方案

例如: PCIe 2.0协议传输速率为5.0GT/s,即每一条Lane上每秒钟内传输5G个Bit,PCIe 2.0的物理层协议中使用的是8b/10b的编码方案,因而PCIe 2.0协议的每一条Lane支持5GT/s *8/10=4Gbps=500MB/s的带宽。以一个PCIe 2.0 x2 的通道为例, x2 的可用带宽为4Gbps * 2 = 8Gbps = 1GB/s。

同理, PCIe 3.0协议传输速率为8.0GT/s,即每一条Lane上支持每秒钟内传输8G个Bit,而PCIe 3.0的物理层协议中使用的是128b/130b的线路编码方案,因而PCIe 3.0协议的每条Lane支持8GT/s * 128/130= 7.877Gbps=984.6MB/s的带宽。

3.PCIe 接口信号

1.电源与地信号

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源, PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

2.链路信号

PCIe链路的最大宽度为×32,但是在实际应用中, ×32的链路宽度极少使用。在一个处理器系统中,一般提供×16的PCIe插槽,并使用PETp0~15、 PETn0~15和 PERp0~15、 PERn0~15共64根信号线组成32对差分信号,其中16对PET xx信号用于发送链路,另外16对PERxx信号用于接收链路。除此之外PCIe总线还使用了下列辅助信号。

3.PERST#信号( #表示低电平有效)

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时, PCIe设备将进行复位操作。 PCIe总线定义了多种复位方式,其中Cold Reset和Warm Reset这两种复位方式的实现与该信号有关。

4.REFCLK+和REFCLK-信号

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制。 PCIe总线的接收端含有时钟恢复模块CDR(Clock Data Recovery), CDR将从接收报文中提取接收时钟,从而进行同步数据传递。值得注意的是,在一个PCIe设备中除了需要从报文中提取时钟外,还使用了REFCLK+和REFCLK-信号对作为本地参考时钟。

在PCIe设备配置空间的Link Control Register中,含有一个“CommonClockConfiguration”位。当该位为1时,表示该设备与PCIe链路的对端设备使用“同相位”的参考时钟;如果为0,表示该设备与PCIe链路的对端设备使用的参考时钟是异步的。使用PCIe进行机箱之间的互联,异步时钟不需要连接时钟线,降低连接难度。

5.WAKE#信号(休眠唤醒信号)

当PCIe设备进入休眠状态,主电源已经停止供电时, PCIe设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源Vcc。在PCIe总线中, WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。值得注意的是产生该信号的硬件逻辑必须使用辅助电源Vaux供电。

6.SMCLK和SMDAT信号

SMCLK和SMDAT信号与x86处理器的SMBus(System Mangement Bus)相关。 SMBus于1995年由Intel提出, SMBus由SMCLK和SMDAT信号组成。 SMBus源于I2C总线,但是与I2C总线存在一些差异。SMBus的最高总线频率为100KHz,而I2C总线可以支持400KHz和2MHz的总线频率。此外SMBus上的从设备具有超时功能,当从设备发现主设备发出的时钟信号保持低电平超过35ms时,将引发从设备的超时复位。在正常情况下, SMBus的主设备使用的总线频率最低为10KHz,以避免从设备在正常使用过程中出现超时。在SMbus中,如果主设备需要复位从设备时,可以使用这种超时机制。而I2C总线只能使用硬件信号才能实现这种复位操作,在I2C总线中,如果从设备出现错误时,单纯通过主设备是无法复位从设备的。

SMBus还支持Alert Response机制。当从设备产生一个中断时,并不会立即清除该中断,直到主设备向0b0001100地址发出命令。

上文所述的SMBus和I2C总线的区别还是局限于物理层和链路层上,实际上SMBus还含有网络层。SMBus还在网络层上定义了11种总线协议,用来实现报文传递。SMBus在x86处理器系统中得到了大规模普及,其主要作用是管理处理器系统的外部设备,并收集外设的运行信息,特别是一些与智能电源管理相关的信息。 PCI和PCIe插槽也为SMBus预留了接口,以便于PCI/PCIe设备与处理器系统进行交互。

7.JTAG 信号

JTAG (Joint Test Action Group) 是一种国际标准测试协议,与 IEEE 1149.1 兼容,主要用于芯片内部测

试。目前绝大多数器件都支持JTAG测试标准。 JTAG信号由TRST#、 TCK、 TDI、 TDO和TMS信号组成。其中TRST#为复位信号; TCK为时钟信号; TDI和TDO分别与数据输入和数据输出对应;而TMS信号为模式选择。

JTAG允许多个器件通过JTAG接口串联在一起,并形成一个JTAG链。目前FPGA和CPLD可以借用JTAG接口实现在线编程ISP(In-System Programming)功能。处理器也可以使用JTAG接口进行系统级调试工作,如设置断点、读取内部寄存器和存储器等一系列操作。除此之外JTAG接口也可用作“逆向工程”,分析一个产品的实现细节,因此在正式产品中,一般不保留JTAG接口。

二、XDMA

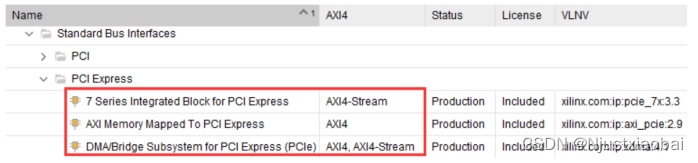

1.XDMA 与其它 PCIe IP 的区别

7 Series Integrated Block for PCI Express:7 Series Integrated Block for PCI Express 是最基础的PCIe IP, 实现的是PCIe 的物理层、链路层和事务层,提供给用户的是以 AXI4-stream 接口定义的TLP包。这是三种 IP 中“最小的”(即最少的资源)和最灵活的,也是开发难度最大的。该 IP 将大部分开发工作留给了用户。 用户如果要往主机发数据, 需要在逻辑端组好MEM_WR事务包送到AXI4-stream 接口,同样要从主机获取数据,就要发送MEM_RD事务包,然后获取到COMPLETE事务包,再从COMPLETE事务包中提取出数据。 使用该IP核,需要对PCIe 协议有清楚的理解, 特别是对事务包 TLP 报文格式。

7 Series Integrated Block for PCI Express:7 Series Integrated Block for PCI Express 是最基础的PCIe IP, 实现的是PCIe 的物理层、链路层和事务层,提供给用户的是以 AXI4-stream 接口定义的TLP包。这是三种 IP 中“最小的”(即最少的资源)和最灵活的,也是开发难度最大的。该 IP 将大部分开发工作留给了用户。 用户如果要往主机发数据, 需要在逻辑端组好MEM_WR事务包送到AXI4-stream 接口,同样要从主机获取数据,就要发送MEM_RD事务包,然后获取到COMPLETE事务包,再从COMPLETE事务包中提取出数据。 使用该IP核,需要对PCIe 协议有清楚的理解, 特别是对事务包 TLP 报文格式。

AXI Memory Mapped To PCI Express IP:该 IP 不仅封装了 7 Series Integrated Block for PCI Express IP,而且还提供了 AXI MM/S 桥。该桥不仅实现了 AXI4 tostream 的功能,还提供了事务层包 TLP 的组装和拆卸、地址转换、错误处理等功能。使用该 IP 时,用户只需通过 AXI4 接口接收和发送 PCIe 数据,不需要组装和拆卸事务包。 从逻辑资源消耗的角度来看, 居三种IP 之中,开发难度也是居三种 IP 之中。

DMA/Bridge Subsystem for PCI Express (PCIe)(XDMA):该 IP 不仅完成了事务层的组包解包,还添加了完整的 DMA 引擎。

XDMA 虽然简单易用,但 XDMA 也有它的局限,主要表现在两个方面:

1)XDMA 正如其名字中的 DMA 一样,适用与大批量的数据传输场景,不适合小数据场景。

2)XDMA 只能用于 PCIe 的终端( endpoint) 设备,不能用于 Root Port,另外二个 IP 既可以用于终端( endpoint)设备,也可以用与 Root Port。

PCIe 的终端设备如 PCIe 视频采集卡、显卡等。简单理解就是 PCIe 的终端设备只有 PCIe 金手指,没有PCIe 插槽,而 Root Port 带有 PCIe 插槽,可以插 PCIe 终端设备。由于一般开发 PCIe 应用大多是 PCIe 终端,所以第二点的局限性实际上较小。

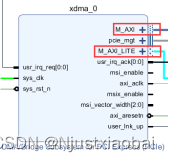

2.XDMA简介

XDMA 一般情况下使用AXI4接口, AXI4接口可以加入到系统总线互联,适用于大数据量异步传输, 而且通常情况下使用 XDMA 都会使用到 BRAM 或 DDR 内存; AXI4-Stream 接口适用于低延迟数据流传输。在配置页面可以选择AXI4或者AXIS。

XDMA不同接口的区别

AXI-MM接口,用于高性能、大带宽的数据传输,AXI Lite Master 接口,是简化版的 AXI 接口,用于较少数据量的通信,一般多用于配置外设寄存器等轻量级的数据传输场景。

AXI-MM接口,用于高性能、大带宽的数据传输,AXI Lite Master 接口,是简化版的 AXI 接口,用于较少数据量的通信,一般多用于配置外设寄存器等轻量级的数据传输场景。

DMA bypass就是普通的PCIE传输。一般会高于pcie to axi lite如果在DMA的长度比较小的情况下和DMA差不多效率但是如果是长度较大一般是DMA性能更好一点。PCIe DMA bypass占用的是另外一个BAR,一般是host直接发起操作,和DMA比比较消耗host资源,如果这个不是问题就可以用。

主机能够通过下面两个接口直接访问用户逻辑:

1)AXI4-Lite Master 配置接口:此端口是固定的 32 位端口,用于对用户配置和状态寄存器进行非性能关键的访问。

2)AXI Memory Mapped Master CQ 旁路( Bypass) 端口:此端口的宽度与 DMA 通道数据路径相同,旨在用于点对点传输等应用程序中可能需要的对用户内存的高带宽访问。

用户逻辑能够通过 AXI4-Lite Slave 配置接口访问 XDMA 内部配置和状态寄存器。在此接口上掌握的请求不会转发到 PCI Express。

三、IP核例化

参考文档https://www.xilinx.com/cgi-bin/docs/ipdoc?c=xdma;v=latest;d=pg195-pcie-dma.pdf。

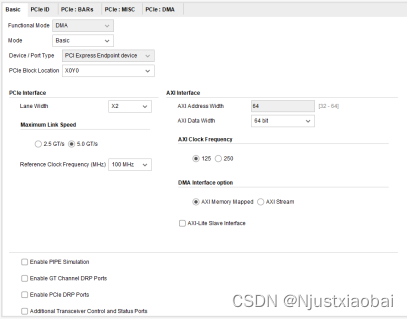

BACIS标签页

Functional Mode: 功能模式, 对于 A7 系列的FPGA 芯片,只支持 DMA 模式;

Mode:配置模式,选择 Basic 配置模式;

Device/Port Type: 设备/端口类型, 仅支持 PCI Express Endpoint device;

PCIe Block Location: FPGA 芯片中可选的 PCIe 块位置,默认为 X0Y0;

PCIe 接口选项:

Lane Width: 链路宽度,对于PCIe x2,选择 x2;

Max Link Speed: 最大链路速度,对应的是 PCIe 版本的传输速率,对于 PCIe 2.*,为 5.0GT/s;

Reference Clock: 参考时钟频率,选择 100MHz;

AXI 接口选项:

AXI Address Width: AXI 地址宽度, 当前, XDMA 仅支持 64 位宽度;

AXI Data Width: AXI 数据宽度;

AXI Clock Frequency: AXI 时钟频率

DMA Interface Option: DMA 接口选项,AXI4和AXIS

AXI4-Lite Slave Interface: 选择是否启用 AXI4-Lite Slave 接口以访问 DMA 状态寄存器;

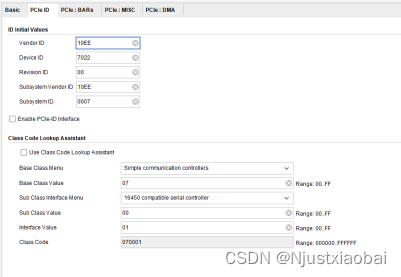

PCIe ID标签页

ID Initial Values:

Vendor ID(供应商 ID):用于识别器件或应用的制造商。有效标识由 PCI Special Interest Group 指定,以保证每个标识都唯一。默认值 10EEh 为赛灵思的供应商标识。

Device ID (器件 ID):对应于应用的唯一标识;默认值为 70h,该值取决于所选配置。该字段可采用任何值;请针对应用更改该值。默认器件 ID 参数取决于:

• 器件系列: 9 表示 UltraScale+, 8 表示 UltraScale, 7 表示 7 系列器件

• EP 或 RP 模式

• 链路宽度: 1 表示 x1, 2 表示 x2, 4 表示 x4, 8 表示 x8, F 表示 x16

• 链路速度: 1 表示 Gen1, 2 表示 Gen2, 3 表示 Gen3, 4 表示 Gen4

如果以上任意值发生更改,则将重新计算“器件 ID”值,以替换先前设置的值

Revision ID (版本 ID):表示器件或应用的版本;作为器件 ID 的扩展。默认值为 00h;请针对应用输入相应的值;

Subsystem Vendor ID (子系统供应商 ID):进一步限定器件或应用的制造商。请在此处输入子系统供应商 ID;默认值为 10EEh。通常,该值与供应商 ID 相同。将该值设为 0000h 可能导致合规性测试出现问题;

Subsystem ID (子系统 ID):进一步限定器件或应用的制造商。该值通常与器件 ID 相同;默认值取决于所选通道宽度和链路速度。将该值设为 0000h 可能导致合规性测试出现问题;

Enable PCIe-ID Interface:启用 PCIe-ID 接口。 如果选中该参数,那么根据选中的 PFx 数量,在 IP 顶层边界处会显示 PCIe ID 端口: cfg_vend_id、 cfg_subsys_vend_id、 cfg_dev_id_pf*、 cfg_rev_id_pf* 和cfg_subsys_id_pf*,并可供用户逻辑驱动。如未选中该参数,则不会在顶层显示这些端口,并根据自定义时设置的值来驱动这些端口。

Class Code Lookup Assistant:

Class Code Look-up Assistant (类代码查找助手):类代码查找助手可针对选定的器件常规功能提供对应的基本类、子类和接口值。

Class Code(类代码):类代码用于识别器件的常规功能,分为以下 3 个字节大小的字段:

• Base Class(基本类):用于广泛识别器件执行的功能类型。

• Sub-Class(子类):进一步具体识别器件功能。

• Interface(接口):用于定义特定寄存器级别编程接口(如果有),允许不从属于器件的软件与器件进行连接。

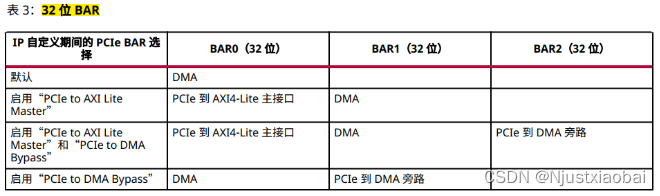

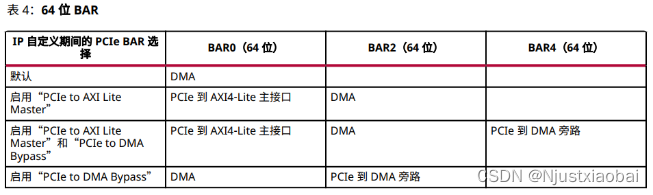

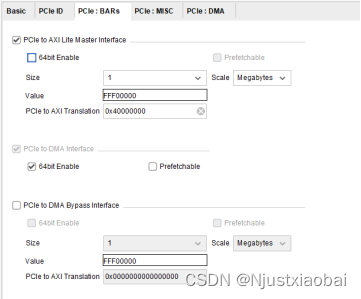

PCIe:BARs标签页

该标签页主要用于配置 BAR,所谓的使能和配置各接口 interface,其实质是配置不同的 BAR,首先介绍下什么是 BAR。 BAR 是 Base Address Register 的缩写,译为基址寄存器。 通过将读取或写入请求映射到基址寄存器( BAR),可以从主机访问 XDMA 内部的配置和状态寄存器以及用户逻辑中的配置和状态寄存器。 XDMA 根据 BAR 命中,将请求路由到适当的位置。 比如,对于 PCIe to AXI-Lite Master (BAR0)地址映射, 命中 PCIe 到 AXI4-Lite Master 的事务将路由到 AXI4-Lite 内存映射用户接口。该接口支持 32 位地址空间和 32 位读取和写入请求。 PCIe to AXI-Lite Master (BAR0)地址映射可由用户逻辑定义。

BAR分2种大小:

32位BAR:地址空间最小可达128字节或者最大可达2千兆字节(GB)。用于内存或I/O。

64位BAR:地址空间最小可达128字节或者最大可达8艾字节(EB)。仅用于内存。

BAR 也可分为两种类型(Type)——I/O 和内存:

I/O: I/O BAR 只能采用 32 位;“可预取 (Prefetchable)”选项不适用于 I/O BAR。仅限针对传统 PCIExpress 端点才能启用 I/O BAR。

内存(Memory):内存BAR可采用64位或32位,并且可预取。

与 BAR 寄存器相关的选项含义:

Size(大小):可用大小范围取决于所选 PCIe 器件/端口类型和 BAR 类型;

Value(值):基于当前选择分配给 BAR 的值;

64bit Enable:是否使用 64 位BAR;

Prefetchable(可预取):识别内存空间预取功能。

每个 BAR 空间可以单独选择 64bit Enable 选项。每个 64 位 BAR 空间都可以选择是否预取。

PCIe to AXI Lite Master Interface: 选择是否启用 AXI-Lite Master Interface 接口;该接口相当于显卡的用户接口, 主机侧可以通过该接口控制显卡的风扇转速、 LED 开关和显示效果等功能,所以当我们需要使用PCIe 接口控制 FPGA 侧的用户逻辑如控制 led 灯等则需要启用该接口;

Size 和 Value:定义用户侧空间的大小, 与 AXI-Lite Master Interface 对接的 AXI4-Lite 总线设备的空间大小有关, 可以根据实际需要来自定义大小;Size大小决定主机测能够访问的地址空间的大小

PCIe to AXI Translation:PCIe 到 AXI 的转换。主机一侧 BAR 地址为 0, 用户逻辑侧 AXI LIte的地址为 0x40000000,则主机访问AXI LIte用户逻辑时, XDMA 将根据该设置将主机侧 BAR地址0转换到AXI LIte总线地址 0x40000000。对与该值的设置有两种方式,一种是手动指定,然后修改后面 AXI LIte总线的偏移地址,另一种是先确定 AXI LIte总线的偏移地址,然后根据偏移地址设置该值。例如修改地址映射AXI LIte总线的偏移地址为 0x40000000,所以设置此值为 0x40000000。

此外, PCIe to AXI Translation 同样也是 AXI LIte总线的基地址,当 AXI LIte总线连接多个 AXI IP 核时,会有多个偏移地址,上位机访问其他 IP 核时的偏移地址是以 PCIe to AXI Translation 的值为基址 0 进行参考的,比如, AXI LIte总线连接的另一个 AXI IP 的偏移地址为 0x40010000,上位机访问该 IP 核的偏移地址就是该 IP 核的偏移地址 0x40010000 - PCIe to AXI Translation 的值 0x40000000=0x10000。 因此当 AXI LIte总线连接多个 AXI IP 核时,需确保 PCIe to AXI Translation 的值小于等于这些 AXI IP 核偏移地址的最小值

PCIe to DMA Interface: PCIe 至 DMA 接口,该接口默认一直开启,prefetchable和nonprefetchable(可预取和不可预取)。

PCIe to DMA Bypass Interface: 选择是否启用 PCIe 至 DMA 旁路接口。 DMA Bypass 就是普通的 PCIe传输, 不用 DMA 逻辑, 而是直接通过 PCIe 进行通信, 一般传输效率会高于 PCIe to AXI Lite。

关于 Prefetchable: 传统上,可预取性意味着预先将内存取出到一个小缓冲区中,以便读取操作变得更快。例如,如果你有两个 PCIe 总线通过网桥连接,如果主总线中的主机必须访问次要总线中的内存,那么网桥将从内存中获取数据并将其存储在网桥缓冲区中。然后主机可以定期访问它,它也会快得多。然而,内存必须是可预取的。如果内存是不可预取的,一旦数据被加载到桥接器的缓冲区,数据将从内存中丢失。如果主机不能从网桥收集数据,那么数据就永远丢失了。如果内存是可预取的,就没有数据丢失的风险。

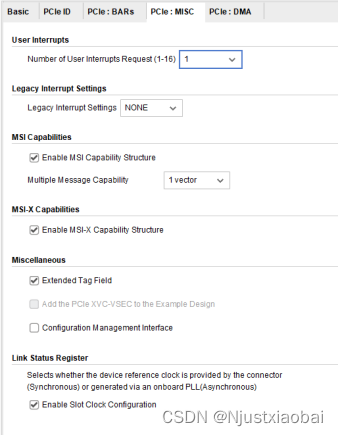

PCIe:MISC 标签页

Number of User Interrupt Request: 用户中断请求数, 最多可以选择 16 个用户中断请求;

Legacy Interrupt Settings: 可以选择传统中断之一: INTA, INTB, INTC 或 INTD;

MSI Capabilities: 默认情况下,启用 MSI 功能,并且启用 1 个向量, 最多可以选择 32 个向量。通常,Linux 仅将 1 个向量用于 MSI, 可以禁用此选项;

MSI-X Capabilities: 使能 MSI-X 功能;

Finite Completion Credits( Advanced 配置模式下有): 在支持有限完成信用的系统上,可以启用此选项以获得更好的性能;

Extended Tag Field: 扩展标签字段, 默认情况下,使用 6 位完成标签。对于 UltraScale 和 Virtex-7 器件,扩展标签选项提供了 64 个标签。对于 UltraScale +器件,扩展标签选项提供 256 个标签。如果未选择扩展标签选项,则 DMA 将 32 个标签用于所有设备

Configuration Management Interface: 是否使用 PCIe 配置管理接口;

关于 MSI-X 中断:用户可以尝试使用 MSI-X 中断,而不是 MSI 或传统中断。使用 MSI-X 中断,数据速率要优于使用 MSI 或基于传统中断的设计。

PCIe:DMA 标签页

Number of Read Channels: 主机到 PCIe 卡( H2C)的 DMA 读通道数, 对于 7 系列 Gen2 IP,最多两个( 通道数越多,同等情况下传输速率越快);

Number of Write Channels: PCIe 卡到主机( C2H)的 DMA 写通道数, 对于 7 系列 Gen2 IP,最多两个(通道数越多,同等情况下传输速率越快);

Number of Request IDs for Read channel:读通道的请求 ID 数,即每个通道的最大未完成请求数,可用的选择是从 2 到 64;

Number of Request IDs for Write channel:写通道的请求 ID 数,即每个通道的最大未完成请求数, 可用的选择是从 2 到 32;

Descriptor Bypass for Read (H2C):读描述符旁路 适用于所有选定的读通道。每个二进制数字对应一个通道。 LSB 对应于通道 0。值为 1 的位表示相应的通道启用了描述符旁路;

Descriptor Bypass for Write (C2H):写描述符旁路 适用于所有选定的写通道。每个二进制数字对应一个通道。 LSB 对应于通道 0。 值为 1 的位表示相应的通道启用了描述符旁路;

AXI ID Width: 默认值为 4 位宽, 也可以选择 2 位宽;

DMA Status port: DMA 状态端口可用于所有通道

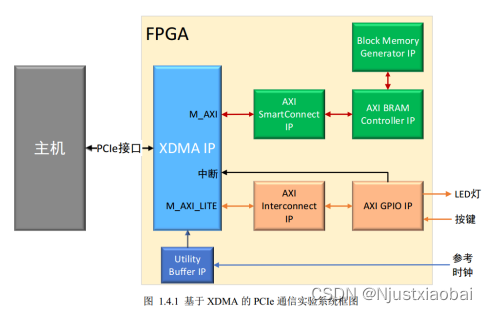

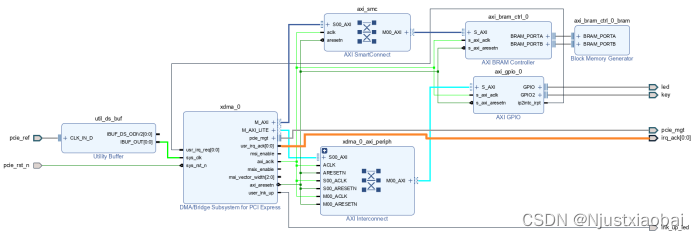

基于 XDMA 的 PCIe 子系统。

用户逻辑通过 AXI4 接口与 XDMA 进行交互,AXI4 Master 接口用来连接显存、 AXI Lite Master 接口用于控制 LED 灯和按键KEY,按键用于中断。

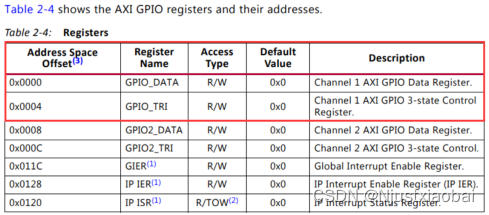

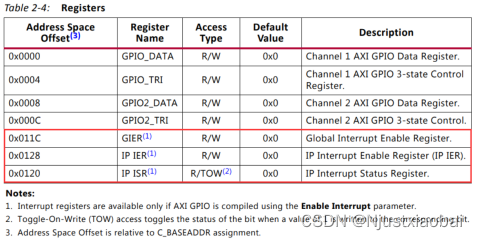

GPIO的寄存器地址

GPIO_DATA:配置各个接口的值

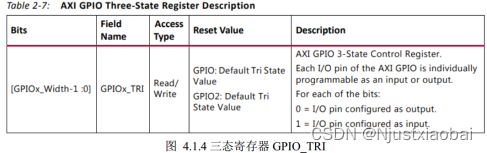

GPIO_TRI 用于动态配置 GPIO 的状态是输入还是输出,“ 0”时,配置对应的 GPIO 为输出

https://china.xilinx.com/support/documentation/ip_documentation/axi_gpio/v2_0/pg144-axi-gpio.pdf。

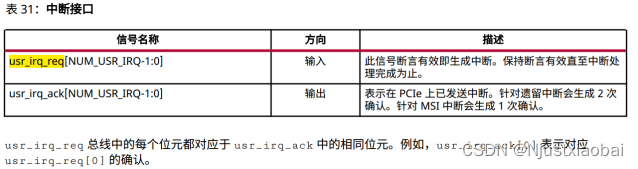

中断usr_irq_req

当使能 AXI GPIO IP 的中断寄存器后(上位机中设置),按下按键 KEY, AXI GPIO IP 核的中断输出引脚 ip2intc_irpt 会输出高电平,产生中断。

usr_irq_ack 信号输出的高电平时间很短,纳秒级,时间太短,,不能通过蜂鸣器判断是否响应。usr_irq_ack 信号的一般用途是,当用户自己设计中断源产生中断时,可以通过 usr_irq_ack 信号的电平状态来决定何时拉低 usr_irq_req 信号。

PCIe 支持三种中断类型:

✓ Legacy 中断

✓ MSI( Message Signaled Interrupt) 中断

✓ MSI-X 中断

Legacy 中断, 主要是为了兼容传统的 PCI,现在很少使用,不推荐使用。 Legacy中断设置可以选择 INTA、 INTB、 INTC 或 INTD; 一般选择 None,即不使用 Legacy 中断。

MSI 和 MSI-X 中断类型机制的基本原理相同,其中 MSI 中断机制最多只能支持 32 个中断请求,而且要求中断向量连续,而 MSI-X 中断机制可以支持更多的中断请求,而并不要求中断向量连续。 MSI-X 是 MSI的扩展——它们服务于相同的功能,但是可以承载更多的信息,并且更加灵活。 对于 XDMA 来说, MSI 和MSI-X 都最多支持 16 个可用的用户中断向量。

推荐使用MSI-X 中断,数据速率要优于使用 MSI 或基于传统中断的设计。MSI-X 中断优先于 MSI 中断, MSI 中断优先于 Legacy 中断,即如果同时启用了 Legacy 中断、 MSI和 MSI-X 中断, XDMA 只会产生 MSI-X 中断。

关于 AXI GPIO IP 核的寄存器空间可查阅 AXI GPIOIP 核的手册 pg144-axi-gpio.pdf 文件获得。https://china.xilinx.com/support/documentation/ip_documentation/axi_gpio/v2_0/pg144-axi-gpio.pdf。

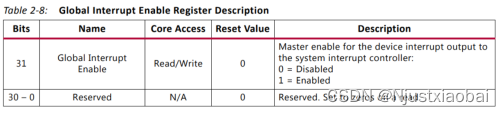

GIER 是全局中断使能寄存器,控制着AXI GPIO IP 的总中断开关,其偏移地址为 0x11c。

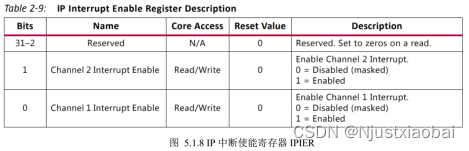

IP 中断使能寄存器 IPIER ( IP Interrupt Enable)用与控制每个通道的中断使能与否,其偏移地址为 0x128。

上位机可以通过读取IPISR 的值,判断中断来源于哪个通道。