- 1navicat对表的字段的定义_navicat字段类型

- 2第6章 使用Feign实现声明式REST调用_loaduserbyusername怎么多传一个参数

- 3手拉手安装Kafka2.13发送和消费消息

- 4【春秋云境】CVE-2023-4450 jeect-boot queryFieldBySql接口RCE漏洞_cve-2023-4450漏洞时间

- 5JMeter组件--配置元件--响应断言

- 6【OTFS与信号处理:论文阅读1】:考虑分数多普勒的OTFS系统有效信道估计(24.01.16更新)_otfs信道估计代码

- 7mysql和Navicat什么关系_navicat和mysql的关系

- 8基于FPGA的一维卷积神经网络CNN的实现(一)框架_fpga cnn

- 9Python使用正则表达式爬取网站图片信息_运用正则表达式爬取jpg图片并下载

- 10博弈论入门(转)_博弈论whythoff

Zynq非VDMA方案实现视频3帧缓存输出,无需SDK配置,提供工程源码和技术支持_三帧缓存

赞

踩

1、前言

对于Zynq和Microblaze的用户而言,要想实现图像缓存输出,多半要使用Xilinx推荐的VDMA方案,该方案目前来说稳定可靠,但并非完美,本文就是要去掉VDMA直接实现于Zynq和Microblaze的图像缓存输出;

2、VDMA的不便之处

就目前而言,VDMA有如下不便之处:

1:需要将视频转为AXI4-Stream流,无论是自己用fifo转还是使用官方的Video In to AXI4-Stream IP转,无疑都增加了资源消耗,对资源紧张的FPGA不宜,再者也加大了FPGA开发难度,对于刚入门的兄弟而言望而却步,最后,Video In to AXI4-Stream这个 IP也是个黑箱,出了问题排查问题太繁琐;

2:需要SDK配置,跑个VDMA还要打开SDK去调用官方库函数进行一大堆配置,无疑是烦,加之有些做硬件的兄弟c语言水平跟我一样菜,根本就搞不定嵌入式C,只想安安心心地干点儿FPGA的活儿就这么难吗?哈哈。。。

3:VDMA输出还要调用Video Time Controller和AXI4-Stream to Video

Out这两个IP才能实现AXI4-Stream视频流到VGA时序的转换,实属费力又不讨好,还是同样的问题,增加资源消耗,黑箱操作,出了问题排查太繁琐;

3、FDMA取代VDMA实现视频缓存输出

前面的文章大量使用过FDMA,但都是讲图像缓存至FPGA的DDR,这次用FDMA将图像缓存至Zynq器件PS端的DDR,FDMA具有以下优势:

1:不需要将输入视频转为AXI4-Stream流;节约资源,开发难度低;

2:不需要SDK配置,不要要会嵌入式C,纯FPGA开发者的福音;

3:看得到的源码,不存在黑箱操作问题;

关于FDMA三帧缓存,请参考我之前写的文章点击查看:FDMA三帧缓存方案

这里,我们将FDMA做了修改,使得输入分辨率由原来的参数类型变为输入类型,这样的好处是方便配置;

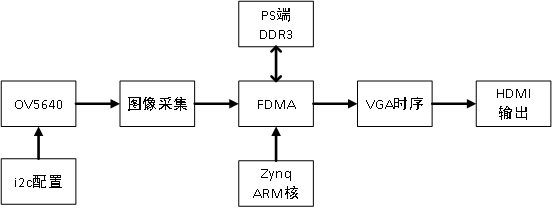

FDMA与Zynq的PS端DDR图像缓存大体架构如下:

就这么简单的实现了Zynq系列PL与PS交互的图像缓存方案;

4、Vivado工程详解

开发板:Xilinx Zynq7100开发板;

开发环境:Vivado2019.1;

输入:Ov5640摄像头,分辨率1280x720;

输出:HDMI,分辨率1920x1080;

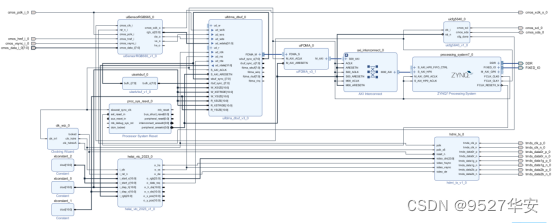

工程架构如下:

整个处理过程Zynq的PS端仅仅提供了一个时钟给到PL端而已,其他任何事儿没干,够简单了吗?正因为PS端除了时钟外啥事儿没干,所以在SDK里只需要跑一个Hello Word死循环就足矣;而且还是官方自己生成的Hello Word,根本不需要写任何c语言代码,玩儿zyqn就这么简单。。。

工程BD如下:

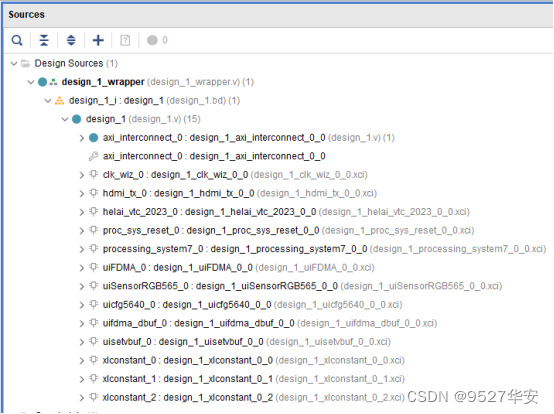

导出硬件后的代码架构如下:

SDK代码如下:真的就只有Hello Word;

int main()

{

init_platform();

print("Hello World\n\r");

cleanup_platform();

return 0;

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

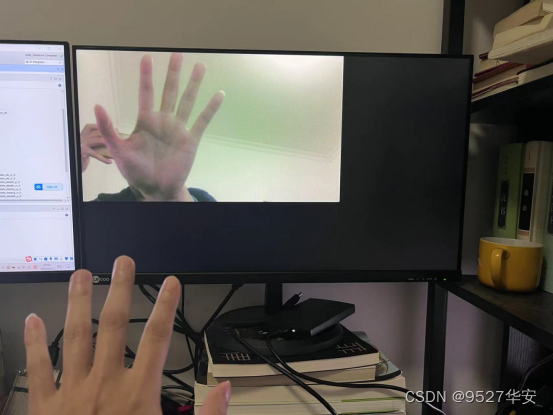

5、上板调试验证并演示

静态演示如下:

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: