- 1Financial Statement Analysis with Large Language Models论文精读

- 2Python机器学习基础教程 鸢尾花分类_鸢尾花分类python算法

- 3hortonworks data platform 安装配置文档

- 4给研究生的一些忠告_研究生工作室不想去

- 5MapReduce知识点一_mapreduce 写入顺序

- 6数据分析学习笔记-用户画像怎么做?

- 7解决Vue 报错error:0308010C:digital envelope routines::unsupported问题_报错digital envelope routines unsupported

- 8三大云平台的数据库方面_关系型数据库 分析型数据库

- 9优维EasyOps,打造新一代运维新方式

- 10编程用什么电脑不卡的:深度解析与推荐

VIVADO在implementation时不满足时序要求_vivado建立时间不满足

赞

踩

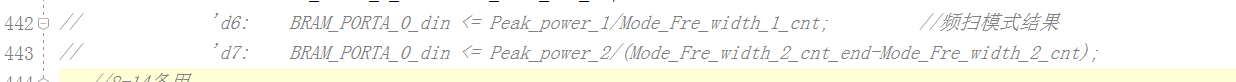

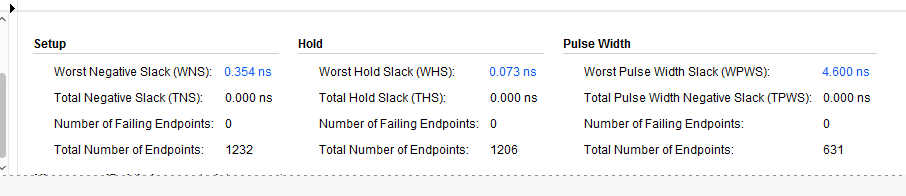

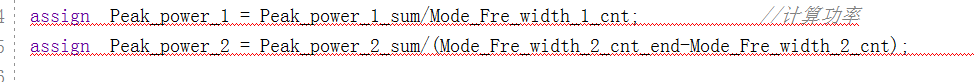

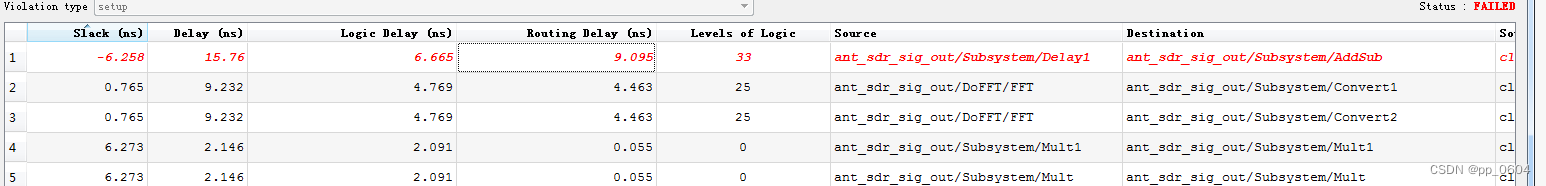

今天一个工程编译时报警说时序不满足要求,如下图

建立时间太长,打开原理图后发现用了很多carry4

将这两句代码屏蔽后

建立时间变成了,少了接近20ns

屏蔽掉

时序满足要求

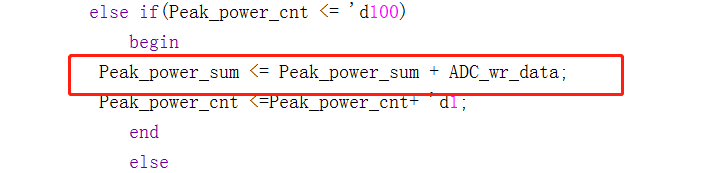

但是将计算程序分成单步运算后,还是不满足要求

同时发现,将Peak_power_reg1-4从32位改成16位后,建立时间也会缩短。

同时发现在时序电路里面用了32位的加法器,延时也比较大。

最后解决办法,1)采用流水线的办法将32位的加法改成4个8位的加法。

2)将计算结果打一拍,在状态机里面判断时就满足时序要求了(原因不知道)

2020.7.30

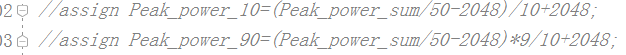

发现根本原因可能是FPGA里面使用除法比较占资源,特别是我这种直接除的。如果必须要用可以使用自带的除法器核。我最后是把这个算平均的没做了,直接把Peak_power_2_sum发送给后端ARM做处理了。

当然,上面说的其它几点也比较占时间,比如说有一个时序不满足的路径是下图这样的,红圈部分全部是用来计算上升沿的10%大小的。

还有流水线加法的问题,对于我这种32位的加法运算本来只用了30ns左右时间,但是时钟是10ns的,所以不满足时序要求。改成4级流水线结构后,实际需要4个周期才能计算出结果,也就是说总的时间反而变长了,但是每一级的计算时间是满足时序要求的。

如果除法是2的整法倍时,最简单的办法就是把除法改为直接右移。

2023.09.21

时序不满足根本原因是看两级时序逻辑之间的总延时(主要由逻辑延时和走线延时两部分构成)是否满足时钟要求,如下图,总延时15.76ns,超过了100M主频的要求,所以报错。

最后查到问题是加法器的位数太高,32位相加,中间逻辑层数33层。通过增加一个时钟加法器的延时,逻辑层数变成了25层,相当于在中间加了一级时序逻辑,把33层的组合逻辑变成了25层和8层(差不多这样),这样就满足时钟要求了。