- 1GO语言学习笔记(与Java的比较学习)(六)

- 2多线程编程:return、pthread_exit()、exit()函数区别_pthread_exit 和 return

- 3Tiled结合Unity实现瓦片地图——Unity实战篇_unity+tiled

- 4如何使用postman做接口测试_postman怎么测接口

- 5git的基本使用_git checkout --track

- 6lua调用c#之lua调用c#中的数组,list,字典_lua传list到c#

- 7按键精灵获取14位纯数字当前时间,时间格式yyyyMMddHHmmss_按键精灵获取当前时间

- 8python(django框架)化妆品淘宝电商销售数据可视化和商品推荐系统设计与实现_基于python淘宝数据可视化

- 9使用 Microsoft SQL Server 2000 的全文搜索功能构建 Web 搜索应用程序_alldata=test.getrows(100000)

- 10Vue3——响应式实现(ref、reactive)_练习掌握选项式api的使用,要求在程序中包含ref响应式、reactive响应式数据定义及

cadence layout 版图绘制技巧_cadence版图设计

赞

踩

cadence操作指南

第一章:cadcence layout 版图绘制技巧

前言

最近在通过cadence仿真工具进行模拟电路的学习,这个系列算是一个学习笔记,使用的版本为cadence618,值得注意的是本文的模拟IC版图绘制流程并不完善,尤其是缺少了dummy管以及guardring,这两个部分以后再专门写一个文章加入到此系列。

一、元件自动生成

- 在原理图界面点击launch ,选择生成layout XL

选择创建新view

其他选项默认即可。

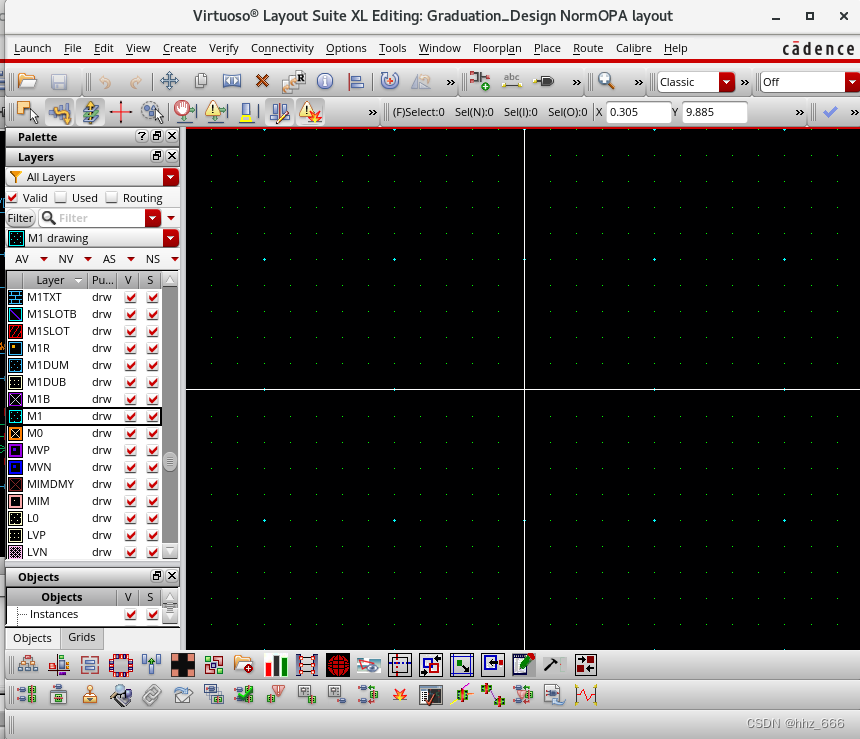

版图窗口创建成功:

Layers界面勾选used可以只显示用到的图层:

2.自动创建元件版图

触碰红框选项,在延伸出的栏目中选择第一个(All From Source)

PR Boundary为版图边界框设置,不需要勾选。

第二页IO Pin设置中可以改变Pin脚的图层,对于工艺库Smic18mmrf,按照默认图层即可。在此页中还可以设置pin的label,可以让后面的连线更方便,如下图

点击options,按图设置即可。

点击OK,完成元件版图的生成。

Shift+f可以观看内部结构,ctrl+f返回宏观视角

二、布局

首先考虑特殊的工艺需求(比如差动放大器MOS匹配),其次考虑布线的方便及面积。

- 移动:m

- 对齐: 点按a,进入对齐模式,此时触碰模块边缘会高亮。

依次点击两个模块的边即可按照边进行对齐,如果点击边中心的圆点,则额外还会中心对齐。

如上图点击Align,上方工具栏会出现对齐按钮。

同时选择多个模块(按住右键框选),再点击对齐选项可以快速对齐。

对齐不仅用于对齐模块,还常用于对齐图层,过孔等。

3.建立group

选择多个模块,点击工具栏 组建group 图标(或在edit中选择),将多个模块进行捆绑,在移动和对齐的时候可以一起。旁边是拆分group

4.旋转与镜像

如下,两种方法

三、布线

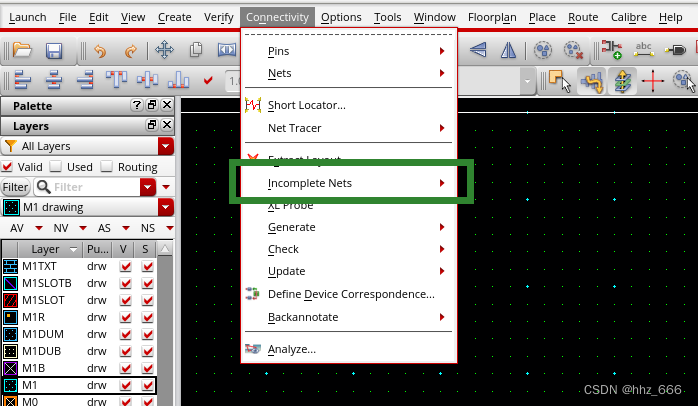

- Connectivity中的incomplete net中可以选择显示(或取消显示)所有连线或者选定某器件所需的连线。

显示全部连线效果图:

此功能可以检查连线是否完成,但是不建议在开启显示的状态下进行连线,一方面画面过于混乱影响精细操作,另一方面自动显示的连线在很多情况下不是最优的连线方法。

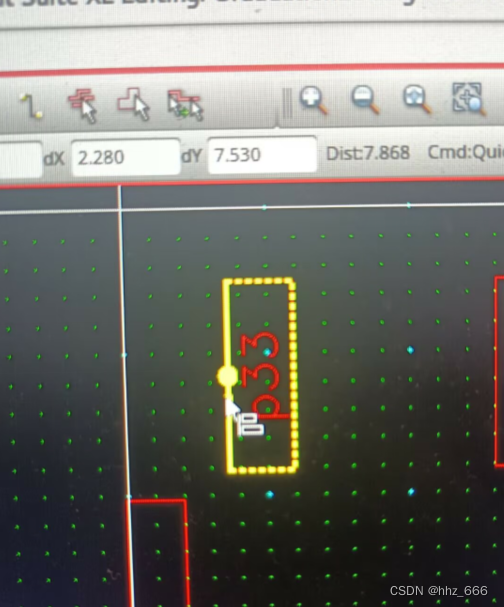

2.在模块内部视角下放大显示,元件的端口会显示电路节点名称,以此为依据,将相同节点的端口连接在一起。

3.连线 :点按p,鼠标靠近图层边缘,会自动提示连线图层以及线宽

(先在layer界面选定图层,可以更容易选中想连的图层边缘)

点击图层边缘,再触碰同节点的图层(同一层),会提示自动对齐,如下图,同为out节点。

点按p,再点击一次图层边缘,可以引出连线,在此状态下,点按F3进入连线编辑,可以调整线宽等。

4.过孔:

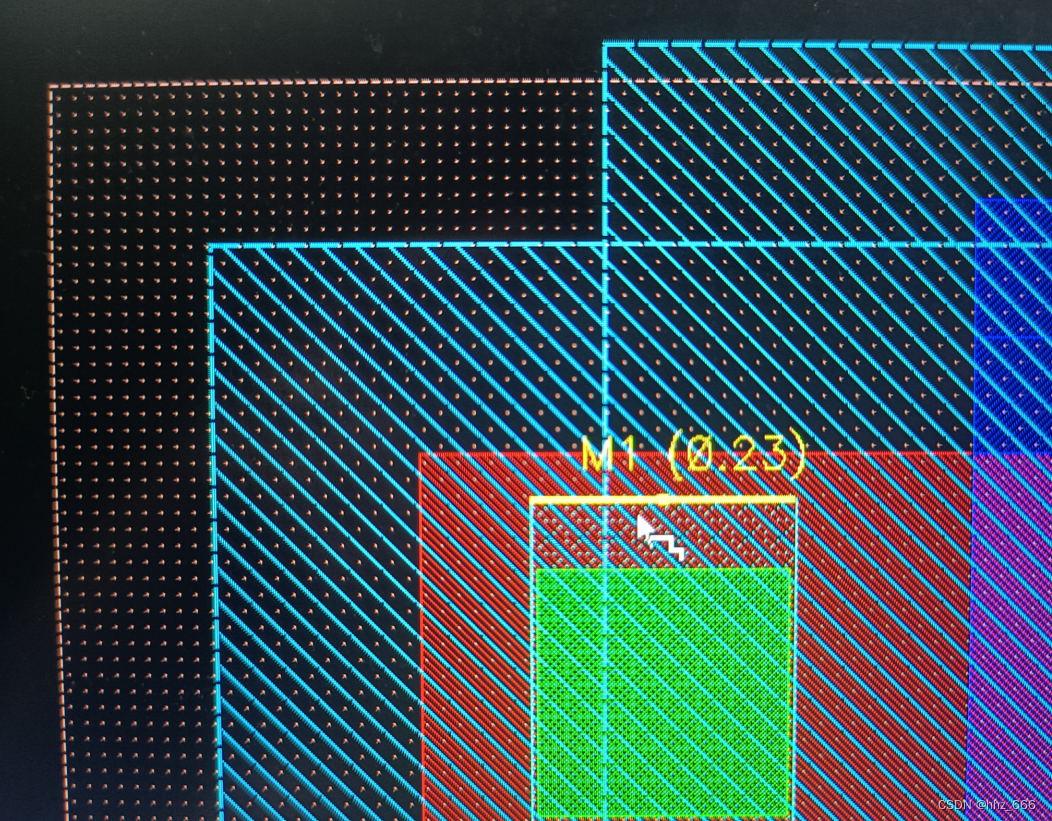

点按o进入过孔设置,如下图,绿色框中可以选择过孔连接的两个图层。ROWs和Columns选项则可以控制过孔规格。选择第二行compute from的Drawn Area则可以自定义过孔大小。

在通常情况下,PMOS的B极连接VDD,NMOS的B极连接VSS(GND),因此应添加VDD到nwell的过孔,VSS(GND)到p_sub的过孔,否则连线不完整,LVS报错。

四、n陷调整

PMOS建立于nwell上,在一般情况下,nwell要接VDD,因此可以将所有PMOS置于同一个nwell上(在不违反特殊工艺要求的情况下)。

- 打散版图

先选中自动生成的器件版图模块,再如下操作

2.在layers界面选择NW图层,点按R绘制矩形,shift+p绘制多边形。

3.添加过孔,连线到VDD。

五、 DRC与LVS设置

1.DRC设置

选择.rule文件

选择一个文件夹存储生成的DRC文件

其余选项保持默认,点击run DRC

2.LVS设置

LVS rule文件路径如下图

如下图,设置网表连接(在进行LVS时,需要打开原理图schematic界面)

设置电源与地

其余保持默认,点击run LVS即可。

总结

以上内容以绘制版图为中心,简要介绍了作者认为比较有价值的一些layout 版图绘制技巧。