热门标签

热门文章

- 1【web3技术】什么是 WEB3?

- 2Ubuntu pycharm配置Conda环境

- 3项目经理必备的5种管理能力

- 4win电脑解析获取微信小程序源码(分包及具体操作)_xiaochengxu.exe

- 5API请求报错 Required request body is missing问题解决

- 6无代码自动化测试工具_applitools

- 7ESP8266安信可及正点原子最新AT固件(2.2.1.0)

- 8mac电脑使用谷歌浏览器,el-upload上传文件点击没反应_el-upload 点击无反应

- 9CSS基础:margin属性4种值类型,4个写法规则详解

- 10完美解决 fatal unable to access ‘httpsgithub.comxxxxxxxxxxx.git’ Recv failure Connection was reset_fatal: unable to access recv failure: connection w

当前位置: article > 正文

【ZYNQ】程序固化到SD卡/FLASH_zynq固化程序到flash

作者:小小林熬夜学编程 | 2024-04-21 22:37:47

赞

踩

zynq固化程序到flash

1-配置PS端IO口

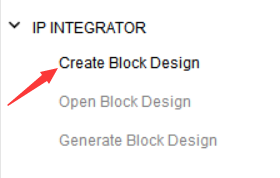

添加ZYNQ IP

2-生成HDL顶层文件

注意将top.v设为顶层

module top ( input wire sys_clk , input wire sys_rst_n, input wire [7:0] ad_data , input wire rx , //触发ram读取发送 output wire ad_clk , output wire tx , //ps ports inout [14:0] DDR_addr, inout [2:0] DDR_ba, inout DDR_cas_n, inout DDR_ck_n, inout DDR_ck_p, inout DDR_cke, inout DDR_cs_n, inout [3:0] DDR_dm, inout [31:0] DDR_dq, inout [3:0] DDR_dqs_n, inout [3:0] DDR_dqs_p, inout DDR_odt, inout DDR_ras_n, inout DDR_reset_n, inout DDR_we_n, inout FIXED_IO_ddr_vrn, inout FIXED_IO_ddr_vrp, inout [53:0] FIXED_IO_mio, inout FIXED_IO_ps_clk, inout FIXED_IO_ps_porb, inout FIXED_IO_ps_srstb ); top_ADC_FFT_USART top_ADC_FFT_USART_inst ( .sys_clk (sys_clk ), .sys_rst_n(sys_rst_n), .ad_data (ad_data ), .rx (rx ), .ad_clk (ad_clk ), .tx (tx ) ); //Instantiate ps block design_1_wrapper ps_block (.DDR_addr (DDR_addr), .DDR_ba (DDR_ba), .DDR_cas_n (DDR_cas_n), .DDR_ck_n (DDR_ck_n), .DDR_ck_p (DDR_ck_p), .DDR_cke (DDR_cke), .DDR_cs_n (DDR_cs_n), .DDR_dm (DDR_dm), .DDR_dq (DDR_dq), .DDR_dqs_n (DDR_dqs_n), .DDR_dqs_p (DDR_dqs_p), .DDR_odt (DDR_odt), .DDR_ras_n (DDR_ras_n), .DDR_reset_n (DDR_reset_n), .DDR_we_n (DDR_we_n), .FIXED_IO_ddr_vrn (FIXED_IO_ddr_vrn), .FIXED_IO_ddr_vrp (FIXED_IO_ddr_vrp), .FIXED_IO_mio (FIXED_IO_mio), .FIXED_IO_ps_clk (FIXED_IO_ps_clk), .FIXED_IO_ps_porb (FIXED_IO_ps_porb), .FIXED_IO_ps_srstb (FIXED_IO_ps_srstb) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

3-生成比特流

4-导出硬件

5-SDK设计

6-创建逻辑应用文件

7-创建FSBL文件

8-创建BOOT.bin文件

fsbl.elf (启动文件)

top.bit (比特流文件)

hello.elf(逻辑应用文件)

顺序不能反

9-SD卡启动

将boot.bit文件复制到SD卡中即可

10-flash启动

注:JTAG模式下烧录

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小小林熬夜学编程/article/detail/465484

推荐阅读

相关标签