热门标签

热门文章

- 1计算机视觉教程(第三版)期末复习笔记 第五章 目标分割(图搜索、主动轮廓模型、基本阈值技术的原理和分类)_计算机视觉微课班第三版

- 2一句话生成数字人,百度智能云曦灵文生3D数字人技术

- 3SourceTree的基础使用【图文详解】_soursetree

- 4课程答疑微信小程序+springboot+vue.js附带文章和源代码设计说明文档ppt_微信小程序 vue spring boot

- 5YOLOv5、YOLOv8改进: GSConv+Slim Neck_vovgscsp

- 6聊聊redis和Elasticsearch_elasticsearch和redis

- 7(5.1)kafka消费者源码——消费者demo及源码解析_kafka poll源码分析

- 8华为OD机试 C++ -围棋的气_本题目只计算气,对于眼也按气计算,如果您不清楚“眼”的概念,可忽略,按照前面描述

- 9【C语言每日一题】08. 字符三角形_给定一个字符,用它构造一个底边长5个字符,高3个字符的等腰字符三角形。

- 10在国内 PMP 有多少含金量?_pmp证书含金量

当前位置: article > 正文

FPGA时序逻辑中,输出为什么会延后于输入一个周期?_fpga什么时候赋值延时一个周期

作者:小小林熬夜学编程 | 2024-06-01 14:47:45

赞

踩

fpga什么时候赋值延时一个周期

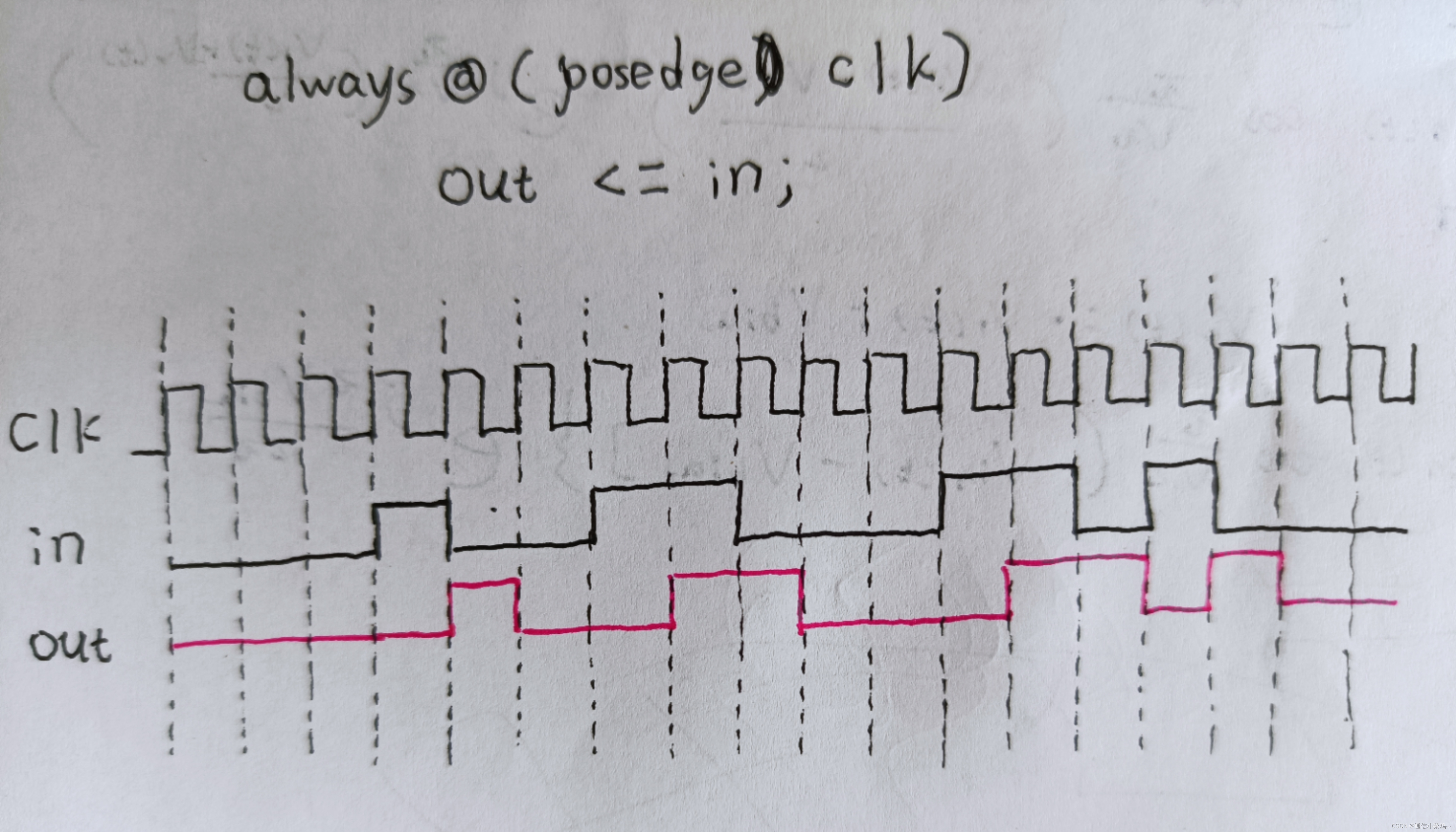

我们先来看下面的这张图,我们的语句是这样写的,在系统时钟上升沿到来的时候,将in的值通过非阻塞赋值的方式赋给输出out,这是的输出将会滞后in一个时钟周期,这是为什么呢?

通过这个输出波形我们也大致可以看出:时序逻辑电路中,每当系统时钟上升沿来临的时候,实际上采集到的是输入信号前一时刻的值。

归根到电路本身,其实可以发现是由于触发器本身的物理延迟所导致的。以D触发器为例:

在系统时钟上升沿到来的时候,这时数据D想立即更新传入到输出Q端,但由于D触发器内部的物理连线以及上一级触发器的Q传到这一级D的时间,此时的Q并不能被直接更新成最新的数据输入,因此此时刻所采集到的数据其实是上一时刻传入的D值 ,这也就造成了在时序逻辑电路中,输出会滞后与输入一个时钟节拍的原因。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小小林熬夜学编程/article/detail/658138

推荐阅读

相关标签