热门标签

热门文章

- 1KeeperErrorCode = NoAuth for /hbase/tokenauth/keys

- 2速拿offer,超全自动化测试面试题+答案汇总,背完还怕拿不到offer?

- 3李阳:京东零售OLAP平台建设和场景实践_olap的使用场景

- 4Hadoop-Apache Hadoop大数据解决方案的整体介绍_hadoop 方案

- 5GitBash: 右键添加 Git Bash Here 菜单

- 6记录一下Centos7 安装mysql8遇到的问题_data dictionary upgrade from mysql 5.7 in progress

- 7QUIC 是如何解决TCP 性能瓶颈的?

- 8V2EX注册_v2ex账号批发零售

- 9Python制作大麦网抢票程序,看喜欢的演唱会再也不怕没票了

- 10IT学习笔记--Kafka

当前位置: article > 正文

基于DSP+FPGA+ADC高速数据采集系统组成及工作原理_fpga控制adc采样硬件原理

作者:小蓝xlanll | 2024-05-29 18:36:07

赞

踩

fpga控制adc采样硬件原理

系统硬件结构

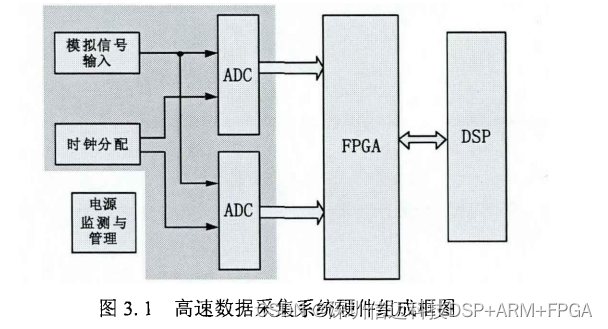

系统采用 的时间交替采样结构的高速数据采集平 台的硬件组成如下所示:

高速数据采集系统主要分作 四个模块

电源监测管理模块

ADC模块

FPGA模块

DSP模块

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/643543

推荐阅读

相关标签