- 1大脑与反向传播

- 2adb工具下载及安装_adb下载

- 3Flutter零基础入门学习资料集合_mk甄选-2024年flutter零基础极速入门到进阶实战[同步更新中]

- 4消息队列基础篇_消息队列cnds

- 5全国青少年信息素养大赛图形化编程复赛·模拟一卷,含答案解析_图形画编程 竞赛

- 6大数据再出发-06Hadoop(优化&特性&HA)_hadoop的数据压缩和编码技术可以帮助减少存储空间和提高数据传输效率。以下哪个选

- 7了解AIGC:让AI创造内容,改变未来

- 8自然语言处理(NLP)原理、用法、案例、注意事项_nlp如何使用

- 9资深老鸟,自动化测试分层模型与落地总结,“我“该如何提升?_性能测试分层模型是什么

- 10ElasticSearch的Update By Query的坑(使用注意事项及其方案)_updatebyquery的坑

ModelSim的使用

赞

踩

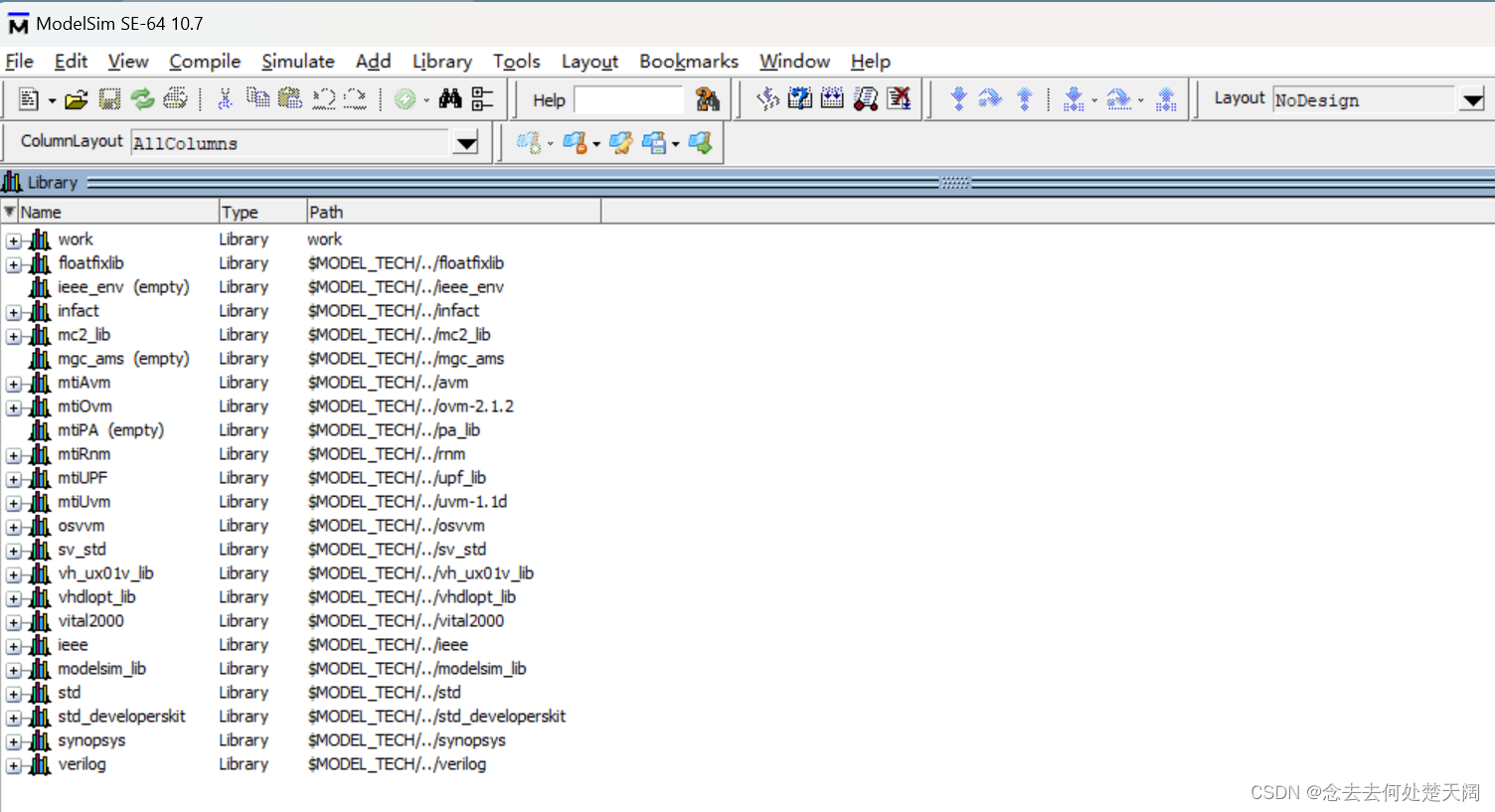

1、打开ModelSim软件

打开ModelSim软件:

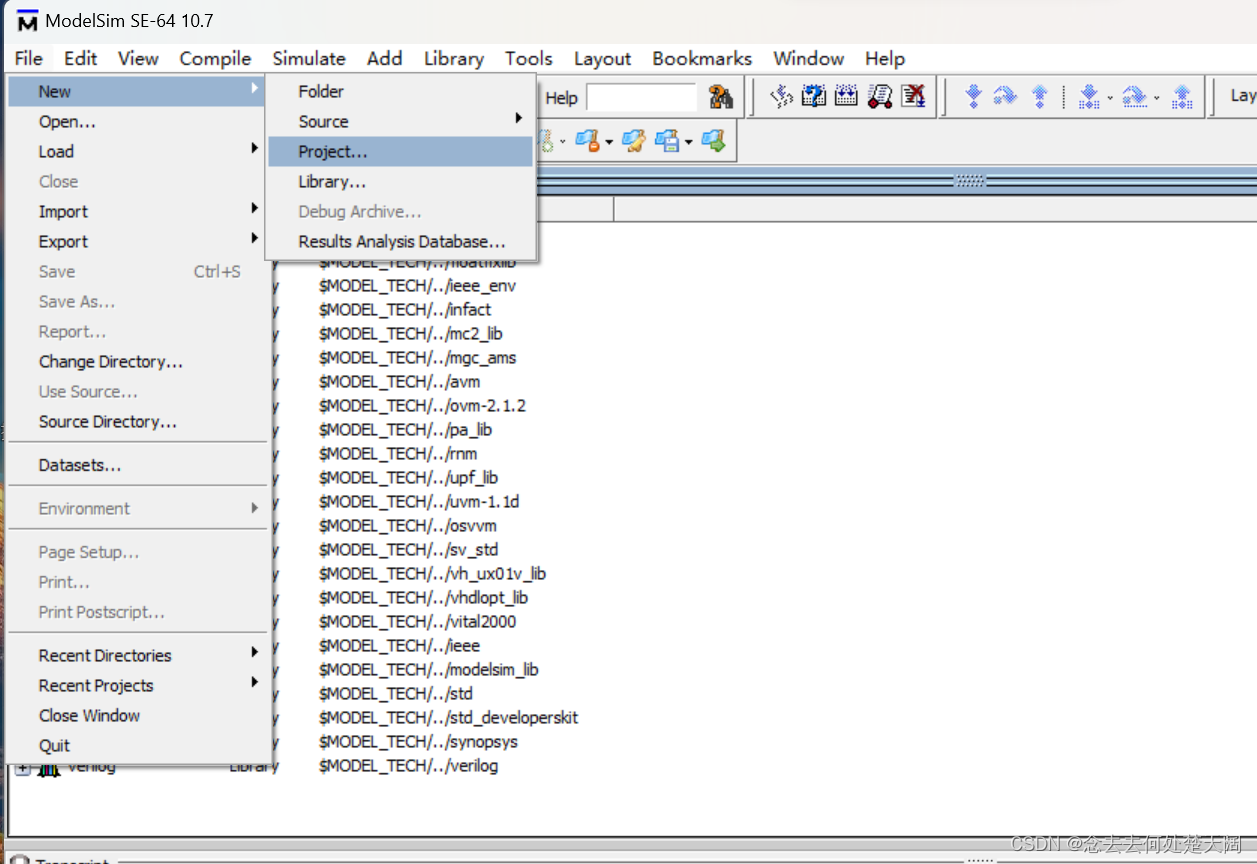

1、建立工程

在modelsim中建立project,选择File->New->Project,如下图所示:

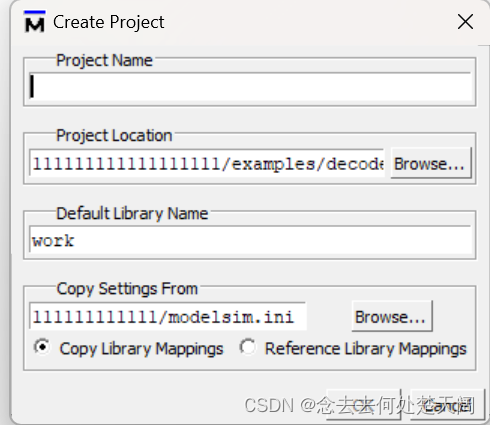

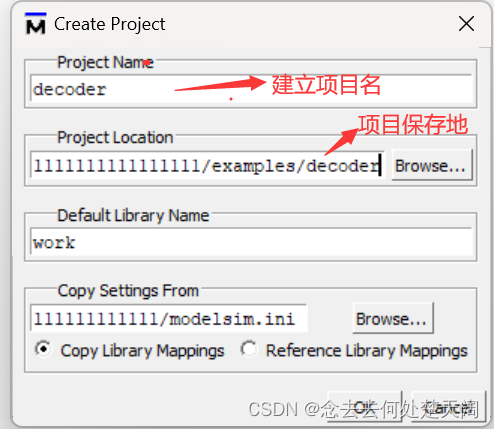

跳出以下弹窗:

在“ Project Name”栏中填写工程名,这里的命名方式,,我们看到这个工程名,就能够知道它是用来做什么的了。这里我们把工程命名为“ decoder”,其中“ Project Location”是工程路径,可以根据需要把工程保存到不同的位置。如我选择在软件安装的新建了一个文件夹,也可以选择默认位置。下面这两部分是用来设置仿真库名称和路径的,这里我们使用默认即可。设置好工程名、工程位置,我们点击【 OK】按钮,弹出如下图所示界面:

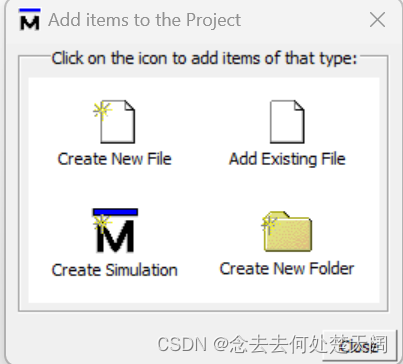

我们可以从该图的选择窗口中看出,它共有四种操作:

Create New File(创建新文件)、Add Existing File(添加已有文件)、

Create Simulation(创建仿真)和 Create New Folder(创建新文件夹)。

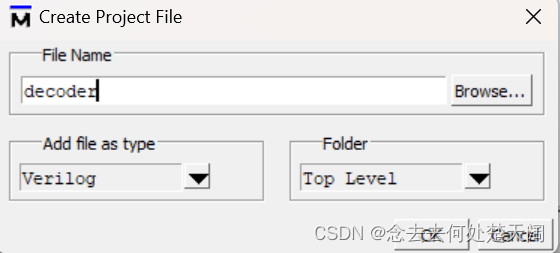

这里我们先选择“ Create New File”(添加已有文件),如下图所示:

默认位VHDL,我们创建的是verilog,选择verilog。

Folder:默认。

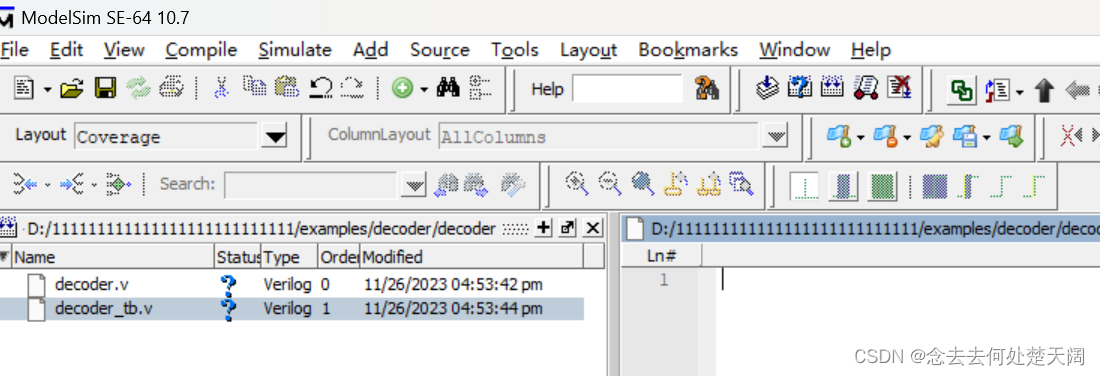

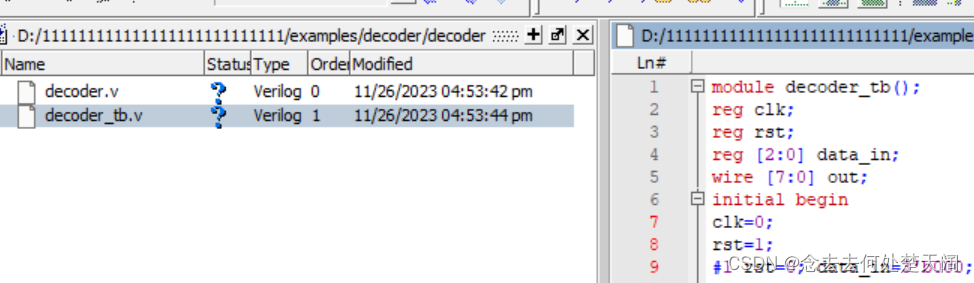

此时可以看到,两个文件“ decoder.v”和“ decoder_tb.v” 添加至我们的ModelSim仿真工程中,如下图所示:

双击后进行代码写入:

2、写入代码

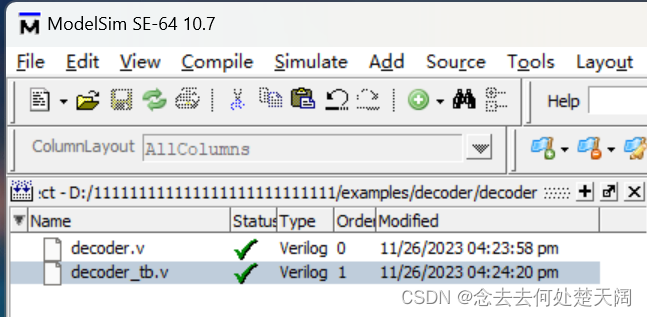

编译完成后结果如下图:

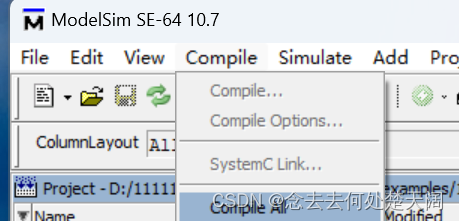

Compile->Compile All

文件编译后“ Status”列可能会有三个不同状态。除了以上的“√”表示的通过状态外,还有两个可能出现的状态:如编译错误(显示红色的“×”)及包含警告的编译通过(有一个黄色的三角符号)。编译错误即Modelsim无法完成文件的编译工作。通常是由于代码中存在语法错误,如需解决问题则在左下角的”Transcrpt“中的红色显示"error"进行双击寻找具体错误

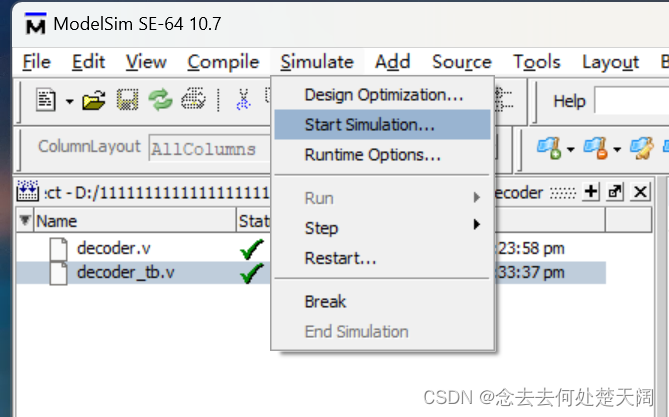

接下来我们在Simulate标签页面中选择Start Simulation ,如下图所示。

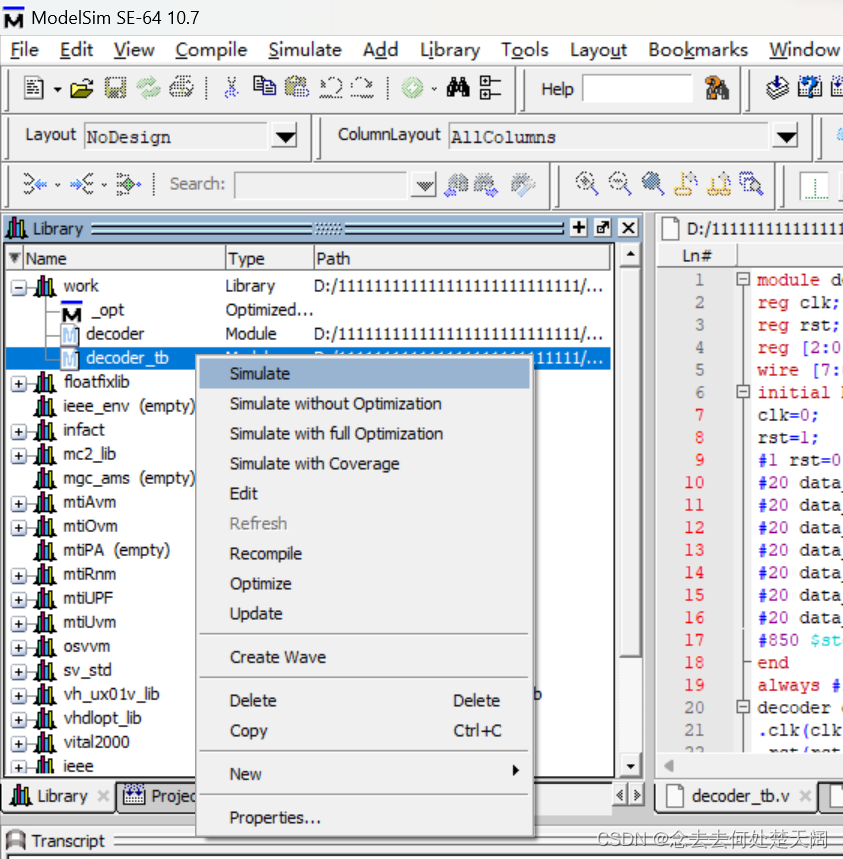

点击Library中的deconder_tb的Simulate

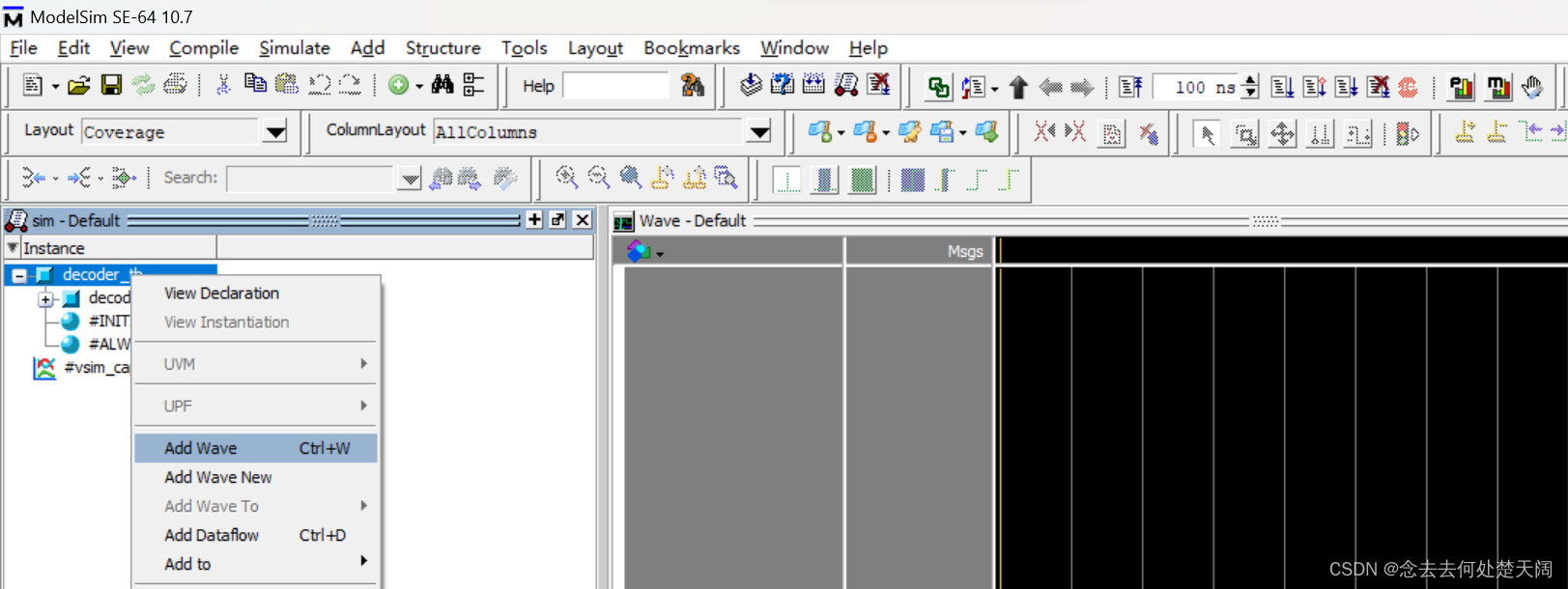

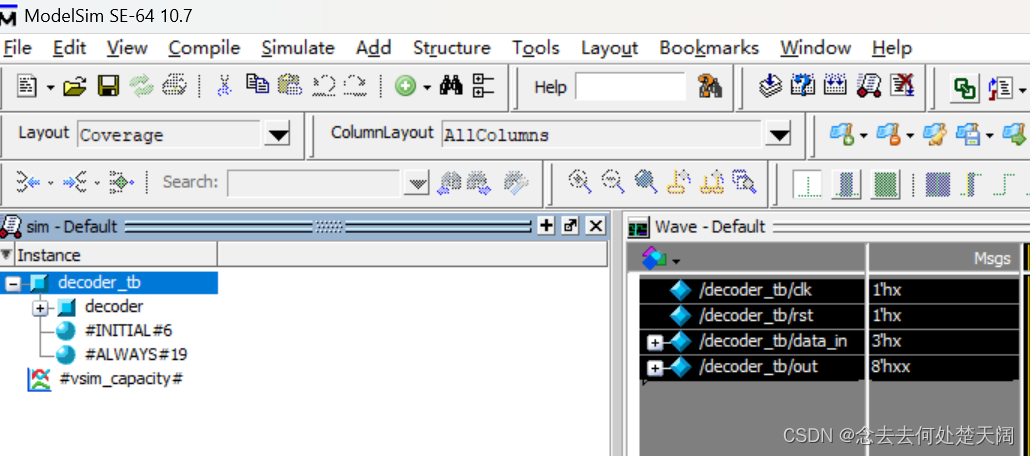

出现下图并添加输入信号:

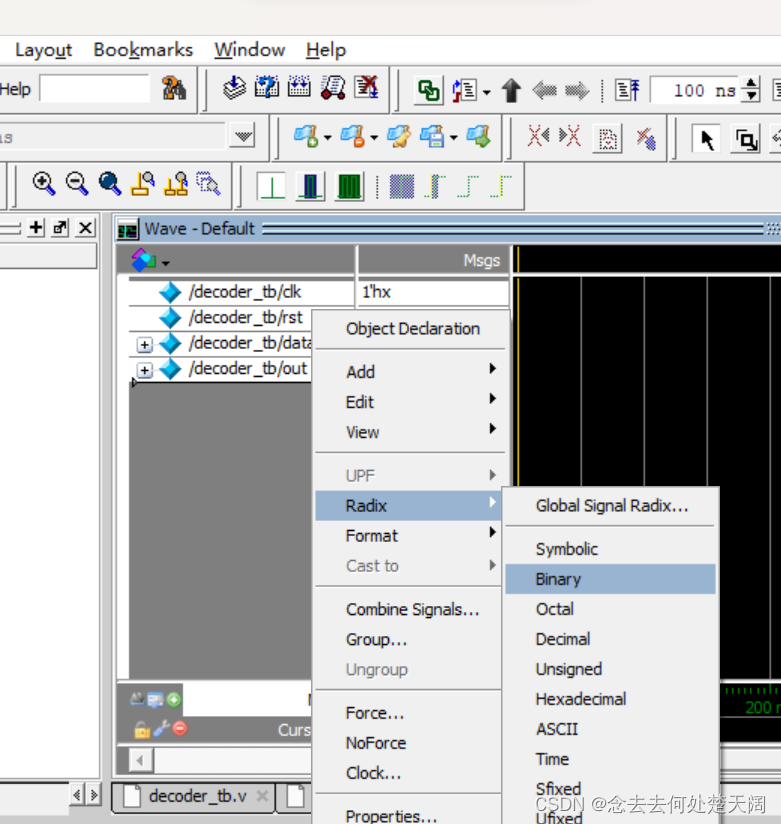

将信号全部改为二进制

点击此处:Run-All

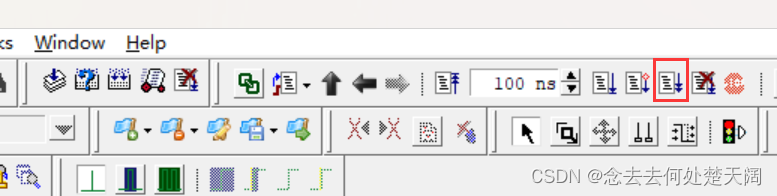

其中的仿真时间调为100ns

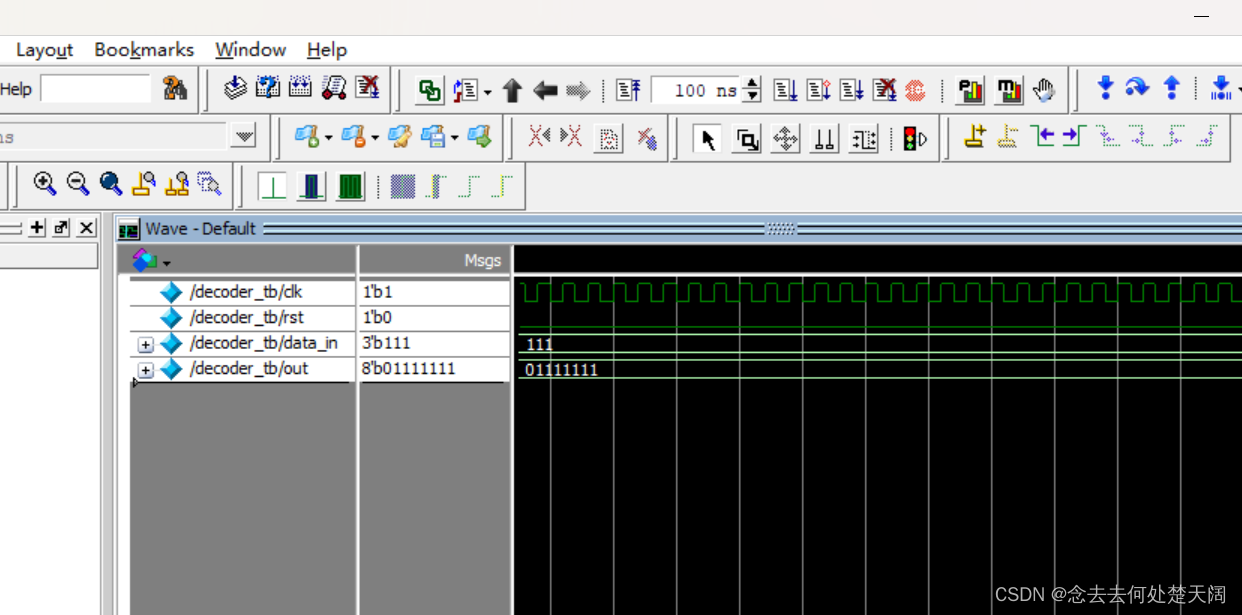

运行后的结果如下图所示: