- 1ShardingSphere 5.0.0 实现按月水平分表_shardingsphere按月分表

- 2【Spark】RDD入门编程实践(完整版)_rddfffffrrrdfffdrdrrrrddrdd4rrrrdrrrrrddrdrdrr4drd

- 3docker安装大数据环境(centos 7)_docker 安装大数据

- 4LeetCode14. 最长公共前缀_leet code 14

- 5Sora背后的技术原理解析(简单易懂版本)_sora技术原理

- 6git撤回已推送远程的提交_git撤回push到远程的

- 7Mac自带apache+php环境配置_mac自带apache开启伪静态

- 8TCP头部详解

- 9中缀表达式转化为后缀表达式 头歌--12关_头歌十二关本关任务:输入一个中缀算术表达式,将其转换为后缀表达式。运算符包括+

- 10JAVA17---安装+配置环境变量 JAVA安装完整教学_java 17安装

Xilinx原语使用方法

赞

踩

目录

简介

原语(Primitive),是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。

Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

1、 时钟组件

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA 全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的 Virtex II器件最多可以提供16个全局时钟输入端口和8个数字时钟管理模块(DCM)。

与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等。

IBUF

单端输入缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。

IBUF #(

.IBUF_LOW_PWR("TRUE"), // Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUF_inst (

.O(O), // Buffer output

.I(I) // Buffer input (connect directly to top-level port)

);

IBUFDS

差分输入缓冲,是IBUF的差分形式。

IBUFDS IBUFDS_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB(IB) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

BUFG

全局缓冲,它的输入是IBUF的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

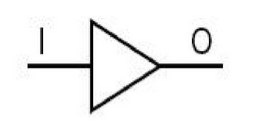

BUFG是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其和同类原语的RTL结构如图所示。全局时钟是具有高扇出驱动能力的缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG组件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。如果要对全局时钟实现PLL或DCM等时钟管理,则需要手动例化该缓冲器。其例化的代码模板如下所示:

// BUFG: 全局时钟缓存(Global Clock Buffer),只能以内部信号驱动

BUFG BUFG_inst (

.O(O), //时钟缓存输出信号

.I(I) // /时钟缓存输入信号

);

BUFGCE

带有时钟使能端的全局时钟缓冲。它有一个输入I、一个使能端CE和一个输出端O。只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出。

BUFGCE #(

.CE_TYPE("SYNC"), // ASYNC, HARDSYNC, SYNC

.IS_CE_INVERTED(1'b0), // Programmable inversion on CE

.IS_I_INVERTED(1'b0) // Programmable on I

)

BUFGCE_inst (inversion

.O(O), // 1-bit output: Buffer

.CE(CE), // 1-bit input: Buffer enable

.I(I) // 1-bit input: Buffer

);

BUFGMUX

全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。当S为低电平时输出时钟为I0,反之为I1。BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系。

BUFGMUX #(

)

BUFGMUX_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

BUFIO

IO端口本地时钟缓冲器。

// BUFIO: Local Clock Buffer for I/O

// Xilinx HDL Language Template, version 2019.1

BUFIO BUFIO_inst (

.O(O), // 1-bit output: Clock output (connect to I/O clock loads).

.I(I) // 1-bit input: Clock input (connect to an IBUF or BUFMR).

);

全局时钟资源的使用方法

Logic + BUFG的使用方法:

BUFG不但可以驱动IBUFG的输出,还可以驱动其它普通信号的输出。当某个信号(时钟、使能、快速路径)的扇出非常大,并且要求抖动延迟最小时,可以使用BUFG驱动该信号,使该信号利用全局时钟资源。但需要注意的是,普通IO的输入或普通片内信号进入全局时钟布线层需要一个固有的延时,一般在 10ns左右,即普通IO和普通片内信号从输入到BUFG输出有一个约10ns左右的固有延时,但是BUFG的输出到片内所有单元(IOB、CLB、选择性块RAM)的延时可以忽略不计为“0”ns。