- 1SeqGAN论文笔记

- 2计算机原理---网络配置4要素_网络配置的组成

- 3入门级 开源SpringBoot+Vue项目_springboot+vue简单博客系统开源项目

- 4开源聚合路由 OpenMPTCProuter 配置使用

- 5ECS磁盘扩容与添加新的硬盘_fdisk 阿里云扩容

- 6freeCAD手册(7)_python 画零件角度freecad

- 7Java中==和equals()的区别_java equals和==区别

- 8数码相册项目_基于s5p6818的数码相册设计的摘要部分

- 9【赠书活动】大数据智能风控:模型、平台与业务实践

- 10云服务器扩容系统盘优点,UCloud云服务器扩容系统盘且不影响已运行数据「还得备份」...

异步FIFO约束set_max_delay_异步fifo max delay

赞

踩

1.最大延迟set_max_delay

set_max_delay [-datapath_only] -from [ node_list] -to [node_list] delay_value

在Set Max Delay约束中使用-datapath_only选项时,它指示综合工具在优化设计时仅考虑数据通路的延迟,而不考虑控制逻辑的延迟。

关于最大最小延迟看了很多文章,最后找到如下这篇文,可以说解释的很明白:

FPGA设计时序约束六、设置最大/最小时延 - 知乎 (zhihu.com)

异步信号之间从某种意义上来说,它们之间是没有确切的时序关系与时序要求的,但为了对从源端到目的端的数据传输延迟有一个基本限制,不至于让其延时不受控,因此采用set_max_delay可以对系统的时序性能做到一个基本的控制。

set_max_delay另一个常用的场景是没有时钟关系的异步信号,但需要设置最大时延。两个异步时钟路径可以使用set_clock_group或set_false_path,从而不会进行时序分析。当异步时钟间的设计合理,如FIFO中的两级同步寄存器,要放宽约束,保证两个时钟间的路径延时符合实际情况,就需要使用set_max_delay。

CDC路径的时序分析可以通过使用set_false或set_clock_groups约束完全忽略,也可以通过使用set_max_delay datapath_only进行部分分析。虽然多bit之间的偏斜可以通过set_bus_skew来约束,但必须确保两个时钟域间的时延不能太大。此时可以通过约束set_max_delay -datapath_only代替set_false_path/set_clock_groups。

2.以格雷码多bit之间存在偏斜举例:

格雷码在正常情况下跨时钟域如下:

若格雷码各bit之间偏斜过大,则会变成下图的情况,导致采样错误:

因此需要对格雷码的最大延时进行约束,延时可设置为读写时钟中最快时钟周期的一半,也可以设置成源端时钟的一半,或者设置成源端时钟的倍数且bit间的skew明显小于一个源端时钟周期,这样的话就能保证采样值和预想值一致。

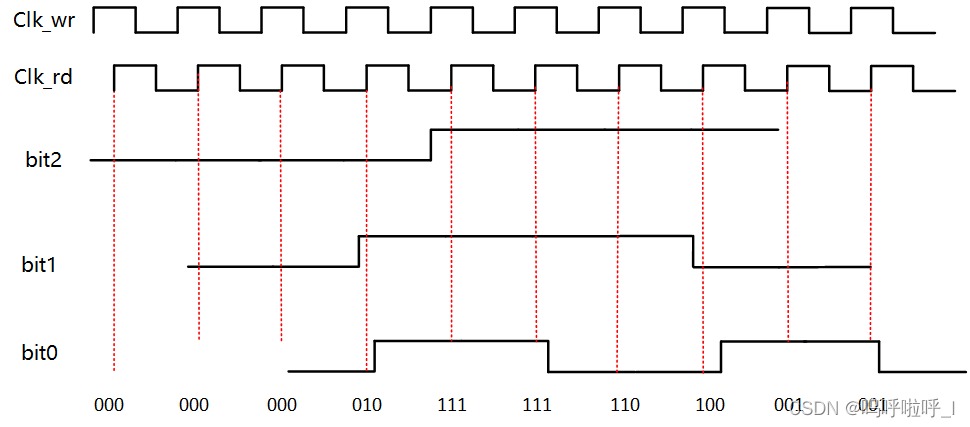

3.拿异步FIFO举例

当读时钟域较慢时,写时钟域的写地址从0000>0001>0011,但是读时钟域之采样到了0000和0011,在相邻两次采样之间发生了两bit变换,这时候不符合异步FIFO采用格雷码的特性,但是可以通过设置set_max_delay约束,值为两个时钟间较块的一个时钟周期内。这样的话就可以保证在第二个时钟沿采样的时候中间的那个数据0001的bit0已经 稳定了。可以看下面的示意图: