嵌入式开发工具介绍与下载_rhapsody 6.0

赞

踩

辅导单片机实验室发现实验室有一个带Altera Cyclone 型号的Nios实验箱,感觉甭爽,赶紧抓住机会学习一下.

原文来自: http://blog.csdn.net/awgn/archive/2006/01/05/571576.aspx

ARM RealView 2.2 (微电子设计)

下载地址:http://www.9iv.com/down/soft/274.htm?eid=217990

http://lib.verycd.com/2005/11/07/0000073497.html

全名:ARM RealView Developer Suite 2.2 最新完整版!

强大的微电子设计、ARM集成开发工具、嵌入式系统设计

ARM,既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。ARM RealView DEVELOPER系列包括RealView开发包,它含有先进的代码生成工具并根据Cortex-A8处理器的特性进行了增进,从而能够提供杰出的性能 和无以伦比的代码密度。这一工具也支持NEON媒体和信号处理扩展集,使得开发者能够通过消除分离的DSP及其关联的开发工具来实现产品和项目的费用降 低。另外,开发包将支持所有新处理器所具有的特性。

ARM RealView开发工具包是一套完整的、高性价比开发调试工具,用于半导体通用32位微控制器(MCU)产品。本工具包以ARM RealView Developer Suite全球领先的16/32位嵌入式RISC微处理器解决方案厂商ARM近日针对采用Intel( XScale(技术的网络基础设施、无线和存储设备,推出ARM(r) RealView(开发工具组。该工具组提供最佳编码生成功能,同时可降低开发成本。作为唯一支持所有顺应ARM结构的Intel Xscale处理器的工具组,RealView能帮助开发人员增强应用功能。

ARM RealView 开发套件是专为中国市场定制的ARM 开发工具包,其强大的集成开发环境包含完整的编辑/编译/调试功能,全面支持ARM7 内核的各种ARM 芯片。该开发套件基于ARM RealView development solution,经过优化/裁剪后以专门适应ARM7 内核的开发,并以完美的性价比适应中国市场的需求。

· 完整的 ISO C/C++优化编译器

· C++ 标准模板库

· 强大的宏编译器

· 复杂内存映像内置代码和数据连接器

· 可选 GUI调试器

· 命令模式的符号调试器(armsd)

· 指令集仿真器

· 制作无格式二进制工具

· 库制作工具

· 全面的在线文档

在这套开发工具组中包括C和C++编译程序、一个专用于Intel Xscale处理器的宏汇编程序和链界程序、支持芯片跟踪功能的AXD调试程序、JTAG调试界面,以及能支持开发底板(developer board)的ARM Firmware Suite(tm)固件套装。

ARM开发系统市场经理Dan Jaskolski说:“我们与英特尔合作得很紧密,以支持顺应ARM结构的Intel XScale t技术的开发。我们对ARM结构的深入理解,使我们能以敏锐洞察力和专业眼光,为基于ARM技术的解决方案提供最高质量的编码生成和调试工具。全新 RealView开发工具组集合了所有必需元素,能保障快速而具成本效益地开发出采用Intel XScale处理器的系统和解决方案。”

英特尔的手持运算部门总经理Peter Green说:“Intel XScale处理器能帮助开发人员在多个方面,如网络基础设施、无线和存储应用等领域大幅削减开发成本,缩短开发周期。类似ARM RealView开发工具组这样的工具提供了重要资源,使开发人员能在他们的平台中加入所需功能和服务。”

ARM为意法半导体定制RealView开发工具

英国ARM公司宣 布:ARM为意法半导体公司STMicro定制ARM® RealView®开发工具包。ARM® RealView®开发工具包是一套完整的、高性价比开发调试工具,用于意法半导体通用32位微控制器(MCU)产品。本工具包以ARM RealView Developer Suite™为基础,其功能可满足意法半导体产品的特殊需求。

ARM公司设计先进的数字产品核心应用技术,应用领域涉及:无线、网络、消费娱乐、影像、汽车电子、安全应用及存储 装置。 ARM提供广泛的产品,包括:16/32位RISC微处理器、数据引擎、三维图形处理器、数字单元库、嵌入式存储器、外设、软件、开发工具以及模拟和高速 连接产品。 ARM公司协同众多技术合作伙伴为业界提供快速、稳定的完整系统解决方案。

ARM Developer Suite v1.2 (电子综合开发)

下载地址:http://www.9iv.com/down/soft/1080.htm?eid=217990

ARM Developer Suite™ ADS 是全套的实时开发软件工具包编译器生成的代码密度和执行速度优异可快速低价地创建ARM 结构应用ADS包括三种调试器ARM eXtended Debugger AXD 向下兼容的ARMDebugger for Windows/ARM Debugger for UNIX 和ARM 符号调试器其中AXD 不仅拥有低版本ARM 调试器的所有功能还新添了图形用户界面更方便的视窗管理数据显示格式化和编辑以及全套的命令行界面该产品还包括RealMonitor™ 可以在前台调试的同时断点续存并且在不中断应用的情况下读写内存跟踪调试工具

ARM 的Real-Time Trace™ 和RealMonitor 均为重要的实时调试解决方案能够缩短开发周期提供特殊软件调试功能可运行于带深度嵌入处理器内核的高集成系统芯片SoC ARM 的Real-Time Trace 产品包括跟踪调试工具MultiTrace 嵌入式跟踪宏单元和Multi-ICE ARM 的RealMonitor包括RMTarget™ RMHost™ 是ARM Developer Suite (ADS) 的补充硬件

Integrator™

Integrator 系列是灵活高效的系统芯片开发平台集成ARM PrimeCell™外设和相关驱动器等软件和硬件能够缩短产品开发周期降低生产总成本固件

ARM Firmware Suite™

ARM 固件组是跟底层硬件相关的应用封装能在ARM 开发平台上迅速建立基于Integrator 或其它ARM内核的应用和操作系统模型工具

ModelGen

ModelGen 是在模拟器上开发和支持复杂半导体器件保留模块的先进建模工具为ARM 独家拥有ARM 的合作伙伴采用ModelGen 在各种仿真器和计算平台上实现信号传输质量和时序模拟

Xilinx ISE 8.2i (强大电子开发)

下载地址:http://www.9iv.com/down/soft/14.htm?eid=217990

http://lib.verycd.com/2005/12/03/0000077793.html forLinux.(X64)

http://lib.verycd.com/2005/04/07/0000045392.html for Windows

http://www.9iv.com/down/soft/19.htm?eid=217990

Xilinx ISE 8.2 终于于2006.6月释放。业界最完整的可编程逻辑设计解决方案,用于实现最优性能、功率管理、降低成本和提高生产率。

Xilinx ISE 8.2i除了具有目前市场上最快的速度,Xilinx ISE v8.2i和新的Virtex-4™ FPGA系列还具有多达200,000个的逻辑单元和高达500 MHz的频率性能,使设计者能够实现完全崭新的设计前景!Xilinx ISE 8.2领略世界上最容易使用的、首屈一指的PLD设计环境,由顶级FPGA工具供应商提供的高级逻辑解决方案Xilinx ISE 8.2

Xilinx ISE 8.2关键特性

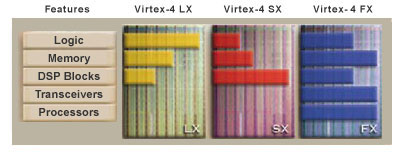

支持Virtex-4系列器件 – 业界第一个多平台FPGA

与最接近的竞争产品相比,Xilinx Fmax技术的平均性能快出10%-37%,最高性能快出70%。

可以节省一个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

可支持多处理器工作站,通过在设计流程中采用超线程技术,使您能够节省项目时间并充分使用工作站设备。

无可比拟的易用性和获得广泛支持的平台

2004与2005年的独立调查显示:ISE是FPGA设计者的首选。

2006 年 6 月,今天宣布推出其深受欢迎的集成软件环境 (ISE) 设计工具套件8.2i 版,新版本增加了新的 ISE Fmax 技术,具有增强的物理综合能力,可提高 Virtex™-4 和 Spartan™-3 架构的性能和时序收敛特性。通过使用 ISE 8.2i 软件,设计者可将性能提升至比以前ISE 版本平均高出10% 到 37%,与相比,并将使用 Virtex-4 FPGA的性能提升至最高可超出竞争解决方案的70%。ISE 8.2i 还对其业界唯一的局部重配置技术进行了增强,可实现更低的成本、更小的尺寸和更低的功耗。

通过以低于上一个ISE 版本的成本来提供相同的平均速度等级,这些新特性旨在进一步加强赛灵思面向高性能系统设计的解决方案,包括具有嵌入式处理、数字信号处理

(DSP) 和高级连接性协议等功能的设计。通过在 ISE 工具中使用高级物理综合功能,设计者可最大程度地提高性能吞吐率,加快上市时间,降低总开发成本。此外,诸如

ChipScope™ Pro 8.2i 片内调试 (in-silicon debug) 集成以及更为强大的局部重配置支持等特性进一步缩短了开发时间,降低了系统成本。

“我们一直在与设计者们合作以解决他们的关键挑战,如时序收敛、成本和系统设计复杂度等。ISE 8.2i 通过高级设计编译优化很好地解决了这些问题,提供了实质性的自动化

Fmax 提升和直观的新界面特性,”赛灵思公司设计软件部副总裁 Bruce Talley 说。“现在设计者可以有更大的把握来满足其最终产品的系统性能、功能性和成本目标。”

ISE Fmax 性能技术可将设计速度提升至最高超出竞争解决方案 70%

新的 ISE Fmax 技术采用高效算法以改善物理综合与逻辑优化的结果,使 Virtex-4 FPGA 的性能优势比竞争器件可最多高出 70%。ISE Fmax 技术包括用于设计重定时、时序驱动包装与布局、性能评估与布局后逻辑优化的一整套功能。最新版本中包含的 ISE Xplorer 工具是一个易于使用的脚本,可帮助设计者评估和优化 Virtex-4 与 Spartan-3FPGA 的性能,对于时序驱动设计可比以前版本平均提高 10% 的性能。ISE 8.2i 提供了一种性能评估模式,可对没有时序约束的设计提供 37% 的直接性能改善。

ISE Fmax 技术与由 Synplicity 和 Mentor Graphics 提供的综合优化技术互为补充。综合优化技术与 ISE Fmax 技术的结合可使用户满足苛刻的时序目标。

“新的 ISE 8.2i 软件与 Synplify Pro 综合技术产品的结合,为赛灵思 FPGA 设计者们提供了推进时序性能的优势,”Synplicity 公司 FPGA 产品营销主管 Jeff Garrison 说。“我们一直与赛灵思保持紧密合作,以确保我们的最新技术,如最近在我们的 Synplify Premier 产品中引入的基于图形的物理综合际醯龋芄挥?ISE 软件实现对接,从而为整个赛灵思 FPGA 产品线提供最快的时序收敛。”

“Mentor Graphics的高级 Precision Synthesis 解决方案在赛灵思 ISE 8.2i 版中的紧密集成,为我们的共同客户同时提供了两种环境的最佳特性,” Mentor Graphics 公司设计创建与综合技术部总经理 Simon Bloch 说。“Precision Synthesis 中经过客户验证的设计分析技术,可实现自动/交互优化与用户控制之间的恰当平衡,现在可为ISE 8.2i 中业界领先的赛灵思Fmax 技术提供有力补充。”

业界唯一的局部重配置解决方案

通过推出 8.2i 版本,赛灵思增加了一种新的方法,以增强其业界首个且唯一的局部重配置解决方案。局部重配置可降低系统成本、尺寸、器件数量及功耗,适用于众多的应用,如 软件无线电 (SDR) 和高性能计算等。设计者现在可以在器件其余部分继续运行的同时将不同的硬件配置动态加载到 FPGA 的同一区域。这种实时可编程特性建立在现场可升级性和多引导方法的基础上。现场可升级性和多引导方法已经使许多赛灵思客户通过实时诊断提升了系统可靠性, 降低了现场服务成本,并延长了市场中已有产品的使用寿命。

易用性提高了生产率

ISE 8.2i 在性能评估模式中提供了快 37% 的按钮,可实现对无需约束的设计进行快速和轻松的评估。ISE 8.2i 还提供了对双核 CPU 工作站的支持,可实现更快的编译时间和在多个 CPU 核上的设计作业并行处理。业界最全面的功耗分析解决方案 Xpower、WebPower Tools 8.2i 中改进的 Web 分析功能以及新的功耗优化布线技术都进一步加强了这些能力。ISE 8.2i Project Navigator(项目浏览器)和集成的 ISE Simulator(仿真器)工具在所有平台上提供了全新直观的 Windows XPTM 外观和感受,使 ISE 8.2i 比以前任何时候都更容易学习和使用。

ChipScope Pro 8.2i

ChipScope Pro 8.2i 的发布提供了业界最完善和易用的调试解决方案,最快可超出仿真50 倍。ChipScope Pro 内核资源估计器可让用户发掘片上调试与验证功能选项,如触发宽度、采样深度,以及高级功能如触发排序和存储资格审查等,以决定片上可视性与 FPGA 资源分配之间的最佳平衡。

Xilinx EDK 8.2i - 嵌入式开发套件

http://www.9iv.com/down/soft/385.htm?eid=217990

Xilinx平台FPGA,例如Virtex-4、Virtex-II Pro 或Spartan-3 器件系列允许工程团队定制他们的硬核/软核设计,以优化其特性集、性能、尺寸和成本. 采用灵活的可编程平台,这些智能的平台工具能够使系统架构、硬件和软件工程师成为可编程系统领域的专家。

XPS 8.1i 支持Virtex-4 FX,并有一系列很有用的改进

我们很高兴地宣布发布 8.1i 版嵌入式开发套件和平台工作室工具包。这些功能强大的处理器开发工具是Xilinx 综合性嵌入式解决方案的关键部分,面向Virtex 和Spartan的FPGA. Xilinx 平台工作室工具包通过提取和自动化处理器系统设计,加速了嵌入式开发。

8.1i 主要的更新是对Virtex-4 FX 平台FPGA器件和其它XPS改进提供新的设计支持,包括软件域轮廓分析、硬件平台开发的改进、易用性和产品的改进。

Xilinx EDK 7.1 (嵌入式编程)

下载地址:http://www.9iv.com/down/soft/824.htm?eid=217990

Xilinx EDK是一个囊括所有用于设计嵌入式编程系统的解决方案。这个预配置的套件包括了Platform Studio工具以及您用嵌入式IBM PowerPC™ 硬件处理器核和/或Xilinx MicroBlaze™软处理器核进行Xilinx平台FPGA设计时所需的技术文档和IP.

Xilinx EDK 7.1i - 嵌入式开发套件

Xilinx平台 FPGA,例如Virtex-4、Virtex-II Pro 或Spartan-3 器件系列允许工程团队定制他们的硬核/软核设计,以优化其特性集、性能、尺寸和成本. 采用灵活的可编程平台,这些智能的平台工具能够使系统架构、硬件和软件工程师成为可编程系统领域的专家。

XPS 7.1i 支持Virtex-4 FX,并有一系列很有用的改进

我们很高兴地宣布发布 7.1i 版嵌入式开发套件和平台工作室工具包。这些功能强大的处理器开发工具是Xilinx 综合性嵌入式解决方案的关键部分,面向Virtex 和Spartan的FPGA. Xilinx 平台工作室工具包通过提取和自动化处理器系统设计,加速了嵌入式开发。

7.1i 主要的更新是对Virtex-4 FX 平台FPGA器件和其它XPS改进提供新的设计支持,包括软件域轮廓分析、硬件平台开发的改进、易用性和产品的改进。7.1i 主要包括以下的创新:

Virtex-4 FX 平台FPGA嵌入式开发支持:

使用协处理器单元 (APU)单元应用,优化了性能,通过将它们移入硬件,强化了软件功能 轮廓/分析关键有助于识别性能瓶颈,使设计功能面向FPGA 硬件 (XPS-SDK)的加速

硬件平台开发的改进:

返回设计资源错误(C, MSS, MHS, etc.)

ISE 和XPS工具相结合- ISE直接调用XPS的程序,如基本系统组建器向导

设计数据表的生成

外设应用测试代码的生成

XPS 仿真环境检查器

为XPS产生定制的板定义文件

易用性和其它产品改进

XMD的改进

支持新的MicroBlaze调试逻辑、面积更小、下载更快

中断和FLASH调试的更精细控制

FLASH书写程序的改进

自动引导下载程序的生成

仿真

XPS仿真环境检查器

自动测试的生成

MicroBlaze ISS支持/改进

FSL高速缓存存储器链接接口

FSL数据链接

模型的改进

OPB Uartlite 支持中断、波特率等

OPB GPIO支持中断

OPB定时器支持多个定时器

系统仿真支持 (MicroBlaze)

为MicroBlaze系统生成虚拟平台模型

概要

升级到 8.4版TCL

运行 GUI 和基本工具的命令行

DRC的改进

升级到新版GCC,用于MB和PPC

LWIP & XMK打包用于插槽: Ethernetlite的LWIP支持

编译器的改进:新CMP指令, MB-gcc优化

数据表生成器

PBDE的改进

允许块上有端口

使端口成为全局或外部端口的能力

将原理图捕捉到JPEG文件中

将FSL向导并入Create IP向导

现在,产生/输入外设向导在Verilog中输出用户核心

改进了库处理-用户库

支持Verilog

Altera Quartus II 6.0 (电子设计):

http://www.9iv.com/down/soft/521.htm?eid=217990

http://lib.verycd.com/2005/12/17/0000080089.html

http://www.9iv.com/down/soft/169.htm?eid=217990 for linux

Quartus II 软件6.0在性能和效率上达到了最高水平。这一版本包括了FPGA供应商提供的第一款时序分析工具——TimeQuest时序分析仪,能够很好的支持业界 标准Synopsys设计约束(SDC)时序格式。该版本还含有扩展团队设计功能,提高了高密度设计协作的效率。

Altera在Quartus II软件6.0高密度设计上实现重大改进

2006年5月9号,香港—Altera公司(NASDAQ: ALTR)今天宣布开始发售6.0版的Quartus® II软件。该版本包括了由FPGA供应商提供的第一款时序分析工具TimeQuest时序分析仪,为业界标准Synopsys设计约束(SDC)时序格式 提供自然、全面的支持。这一最新版本还包括扩展的团队设计功能,能够有效管理高密度设计团队之间的协作。这些改进迎合了当今高密度90nm的设计要求,同 时为满足客户对更高密度FPGA的需求以及Altera发展下一代65nm产品系列打下了基础。

Synopsys战略联盟总监Lonn Fiance评论说:“FPGA设计人员将业界标准SDC时序约束格式直接读取到TimeQuest时序分析仪中,能够更迅速的实现时序逼近。采用SDC 格式可以提高FPGA设计人员的效率,进一步促进标准时序验证方法在半导体业界的应用。”

Quartus II 软件6.0的新增功能包括:

TimeQuest时序分析仪

TimeQuest时序分析仪——新的 ASIC性能时序分析仪,能够自然的支持业界标准SDC时序约束格式。TimeQuest时序分析仪帮助您建立、管理、分析具有复杂时序约束的设计,例如 时钟复用设计和源同步接口,并能够迅速进行高级时序验证。Quartus II 软件6.0订购版含有TimeQuest时序分析仪。

工程管理接口——改进的团队设计

工程管理接口——在顶层设计上 管理资源和时序预算。此外,您还可以利用工程管理接口来管理模块间的时序约束,以达到最佳性能。这一新功能使团队能够协作实现高密度FPGA设计,从而提 高设计性能和效率。这一功能是建立在Quartus II 软件5.0和5.1首次引入的渐进式编译设计基础之上。

其他增强功能

SystemVerilog支持——包括对流行SystemVerilog语法的支持。SystemVerilog提高了寄存器传送级(RTL)设计的抽象等级,更迅速的实现RTL设计。

改进的I/O引脚规划器——直接对Altera®宏功能、知识产权(IP)进行整合,以及对引脚的简单分配。

扩展的板级设计支持——采用Stratix® II FPGA进行设计时,为设计输出提供HSPICE模型,以提高电路板建模的效率。

LogicLock增强——提供LogicLockTM成员资源滤除功能,将某些资源类型(例如,数字信号处理 (DSP)单元、 M4K存储器等)的设计单元从LogicLock区域中自动滤除,从而提高了设计效率。

SignalTap II逻辑分析仪——含有Nios® II CPU SignalTap® II分解插件。插件协助完成对已定义Nios II节点集的“提取”,以及Nios II CPU助记符定义,从而提高了系统级调试效率。

OS支持

Windows XP Professional x64 (32位)——运行Quartus II软件32位应用软件的Windows XP Professional x64操作系统支持Quartus II 软件。64位硬件/软件平台上运行32位应用软件的优势在于能够访问更多的存储器,从而提高了性能。

Red Hat linux Enterprise 4.0——现在提供支持。

Nios.II.Development.Kit.Version.5.0(NiosII嵌入式处理器集成开发环境)

下载地址:http://lib.verycd.com/2005/12/28/0000082073.html

Altera Nios简介

在20 世纪90年代末,可编程逻辑器件(PLD)的复杂度已经能够在单个可编程器件内实现整个系统。完整的单芯片系统(SOC)概念是指在一个芯片中实现用户定 义的系统,它通常暗指包括片内存储器和外设的微处理器。最初宣称真正的SOC――或可编程单芯片系统(SOPC)――能够提供基于PLD的处理器。在 2000年,Altera发布了Nios处理器,这是Altera Excalibur嵌入处理器计划中第一个产品,它成为业界第一款为可编程逻辑优化的可配置处理器。本文阐述开发Nios处理器设计环境的过程和涉及的决 策,以及它如何演化为一种SOPC工具。

Altera清楚地意识到,如果把可编程逻辑的固有的优势集成到嵌入处理器的开发流程中,我们就会拥 有非常成功的产品。基于PLD的处理器恰恰具有应用所需的特性。一旦定义了处理器之后,设计者就“具备”了体系结构,可放心使用。因为PLD和嵌入处理器 随即就生效了,可以马上开始设计软件原型。CPU周边的专用硬件逻辑可以慢慢地集成进去,在每个阶段软件都能够进行测试,解决遇到的问题。另外,软件组可 以对结构方面提出一些建议,改善代码效率和/或处理器性能,这些软件/硬件权衡可以在硬件设计过程中间完成。

处理器体系和开发流程

Altera很早就认为创建基于Nios处理器的系统和处理器本身一样很重要。随着新生产品逐渐成熟,Altera必须让嵌入设计者信服地接受新的处理器 和新的设计流程。我们最无法确定的是嵌入设计者是否接受新的指令集。随着C成为嵌入设计的事实标准,这一问题也迎刃而解。Altera和Cygnus(现 归RedHat所有)密切合作定义指令集体系,这样Cygnus可以很容易地导入和优化他们的GNUPro Toolkit,这是绝大部分设计者非常熟悉的标准GNU环境。

设计流程成为最大的问题。现成的微控制器提供了定义明确的外设组,由制造商集 成处理器和外设。可配置处理器让设计者自行创建总线体系,定义存储器映射和分配中断优先级,非常自由地完成更多的工作。Altera相信SOPC的优势会 吸引嵌入设计者,但是条件是其它的需求最小,风险很低。

Nios II集成开发环境

Nios II集成开发环境(IDE)是Nios II系列嵌入式处理器的基本软件开发工具。所有软件开发任务都可以Nios II IDE下完成,包括编辑、编译和调试程序。Nios II IDE提供了一个统一的开发平台,用于所有Nios II处理器系统。仅仅通过一台PC机、一片Altera的FPGA以及一根JTAG下载电缆,软件开发人员就能够往Nios II 处理器系统写入程序以及和Nios II处理器系统进行通讯。

Nios II IDE基于开放式的、可扩展Eclipse IDE project工程以及Eclipse C/C++ 开发工具(CDT)工程。

Nios II IDE为软件开发提供四个主要的功能:

(1)工程管理器

Nios II IDE提供多个工程管理任务,加快嵌入式应用程序的开发进度。

新工程向导 ——Nios II IDE推出了一个新工程向导,用于自动建立C/C++应用程序工程和系统库工程。采用新工程向导,能够轻松地在Nios II IDE中创建新工程。

软件工程模板——除了工程创建向导,Nios II IDE还以工程模板的形式提供了软件代码实例,帮助软件工程师尽可能快速地推出可运行的系统。

(2)编辑器和编译器

Altera Nios II IDE提供了一个全功能的源代码编辑器和C/C++编译器

文本编辑器——Nios II IDE文本编辑器是一个成熟的全功能源文件编辑器。这些功能包括:语法高亮显示 - C/C++、代码辅助/代码协助完成、全面的搜索工具、文件管理、广泛的在线帮助主题和教程、引入辅助、快速定位自动纠错、内置调试功能。

C/C++编译器——Nios II IDE为GCC编译器提供了一个图形化用户界面,Nios II IDE编译环境使设计Altera的Nios II处理器软件更容易,它提供了一个易用的按钮式流程,同时允许开发人员手工设置高级编译选项。

Nios II IDE编译环境自动地生成一个基于用户特定系统配置(SOPC Builder生成的PTF文件)的makefile。Nios II IDE中编译/链接设置的任何改变都会自动映射到这个自动生成的makefile中。这些设置可包括生成存储器初始化文件(MIF)的选项、闪存内容、仿 真器初始化文件(DAT/HEX)以及profile总结文件的相关选项。

(3)调试器

Nios II IDE包含一个强大的、在GNU调试器基础之上的软件调试器-GDB。该调试器提供了许多基本调试功能,以及一些在低成本处理器开发套件中不会经常用到的高级调试功能。

基本调试功能——Nios II IDE调试器包含如下的基本调试功能:运行控制、调用堆栈查看、软件断点、反汇编代码查看、调试信息查看、指令集仿真器。

高级调试 ——除了上述基本调试功能之外,Nios II IDE调试器还支持以下高级调试功能:硬件断点调试ROM或闪存中的代码、数据触发、指令跟踪。

(4)闪存编程器

使 用Nios II处理器的设计都在单板上采用了闪存,可以用来存储FPGA配置数据和/或Nios II编程数据。Nios II IDE提供了一个方便的闪存编程方法。任何连接到FPGA的兼容通用闪存接口(CFI)的闪存器件都可以通过Nios II IDE闪存编程器来烧结。除CFI闪存之外,Nios II IDE闪存编程器能够对连接到FPGA的任何Altera串行配置器件进行编程。

ModelSim SE 6.1F (电子仿真):

http://www.9iv.com/down/soft/1488.htm?eid=217990

http://lib.verycd.com/2006/06/02/0000105276.html

2006.6月初发行的最新版本:ModelSim SE 6.1f

ModelSim专业版,VHDL、Verilog和Mixed-HDL仿真器

Mentor Graphics ModelSim SE 6.1b是业界最优秀的HDL语言仿真器,它提供最友好的调试环境,是唯一的单内核支持VHDL和Verilog混合仿真的仿真器。是作 FPGA/ASIC设计的RTL级和门级电路仿真的首选,它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码 与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段。全面支持VHDL和Verilog语言的IEEE 标准,支持C/C++功能调用和调试

具有快速的仿真性能和最先进的调试能力,全面支持UNIX(包括64位)、Linux和Windows平台。

主要特点:

RTL和门级优化,本地编译结构,编译仿真速度快;

单内核VHDL和Verilog混合仿真;

源代码模版和助手,项目管理;

集成了性能分析、波形比较、代码覆盖等功能;

数据流ChaseX;

Signal Spy;

C和Tcl/Tk接口,C调试

Synplify Pro 8.1

http://www.9iv.com/down/soft/1489.htm?eid=217990

Synplify Pro 8.1半导体设计及验证软件供应商Synplicity公司近日对其可编程逻辑器件(PLD)综合软件Synplify Pro 8.1进行了改进。Synplify Pro软件支持Verilog-2001标准以及新器件及新操作系统(OS)。最新版本的Synplify Pro软件提高了若干项QoR(最终结果质量),以及增效定时引擎及自动寄存器重新定时功能的增强,能够提高设计人员的产出率,并且性能更佳。

业界领先的基于FPGA的ASIC原型验证综合工具,通过提供诸如团队设计、自动re-timing、快速的编译以 及额外的特性来优化设计结果。除了具有B.E.S.T.引擎外,Synplify pro又加入了D.S.T.(Direct Synthesis Technology),SCOPE(Synthesis Constraint Optimization Environment),STAMP和多点优化等技术来满足设计者的需求。Synplify pro提供了和布局布线工具之间的native-link接口来完成Push-Button的流程,使用户只需要点击就可以完成所有的综合和布局布线的工 作。基于Synplicety公司的B.E.S.T.引擎,Synplify Pro可以轻松综合数百万门的设计而不需要分割。

Synplify Pro详细功能描述

◇ 提供优于传统综合技术的快速的全局编译和综合优化,针对算术模块和数据路径的高性能和高面积利用率的优化;

◇ 提供对设计约束的全面控制,智能化人机界面,提高设计效率,结合具体器件结构,提供最佳性能;

◇ 提供自动的RAM例化过程,提供自动时钟控制和同步/异步清零寄存器结构,自动识别FSM和选择编码方式以达到最佳性能,提供针对FSM的快速的调试和观察工具,自动进行流水处理,以提高电路性能;

◇ 在不改变原代码的情况下,提供内部线网到外部测试管脚的能力,在源代码、RTL视图和Log文件之间的交互标识能力;

◇ 集成化、图形化的分析和调试关键路径的环境;

◇ 支持黑盒子的时序以及管脚信息,支持同时实现多个应用,通过设计划分支持Xilinx模块化设计;

◇ 自动对组合逻辑进行寄存器平衡以提高性能,支持智能化的增量综合。

Synplicity Amplify V3.6.1 (电子物理优化器):

http://www.9iv.com/down/soft/1069.htm?eid=217990

是 第一款为FPGA设计的物理综合产品。 Amplify Physical Optimizer 产品补充了流行的Synplify FPGA综合产品,可通过在综合过程中充分利用物理设计信息来提高性能和生产力。Amplify Physical Optimizer是为那些需要从他们的Xilinx Virtex?系列和Spartan-3 系列器件中获得尽可能的最高的性能的开发人员创建的。 Amplify产品已经被全球100多家企业采用。 Amplify?工具结合了寄存器级(RTL)的图形物理约束以及创新的可同时完成布局和逻辑优化的物理综合算法。其输出不仅是一个逻辑设计的物理布局, 而且是一个新的物理优化的网表。另外,Amplify产品还包括了全部的Optimization Physical Synthesis (TOPS)技术。 TOPS技术进一步提升了性能,同时还通过高度准确的时序估算降低了设计反复次数。

Mentor Graphics LeonardoSpectrum V2005a.82 (HDL逻辑综合软件):

http://www.9iv.com/down/soft/2019.htm?eid=217990

LeonardoSpectrum是Mentor公司出品的一款HDL逻辑综合软件,有了LEONARDO SPECTRUM,您即可利用VHDL或是Verilog语言,LeonardoSpectrum是由Mentor Graphics发展,不但操作非常方便,还具备工作站等级ASIC工具的強大控制能力和最优化功能特色。

LEONARDO SPECTRUM是非常好的逻辑综合软件,有了 LEONARDO SPECTRUM,您即可利用VHDL或是Verilog语言建立PLD、FPGA和ASIC元件。LeonardoSpectrum是由Mentor Graphics发展,不但操作非常方便,还具备工作站等级ASIC工具的強大控制能力和最优化功能特色。LeonardoSpectrum提供 PowerTabs菜单,工程师面对设计挑战时,可使用其中的先进合成控制选项;除此之外,LeonardoSpectrum也包含強大的调试功能和业界 独有的五路相互探测能力(five-way cross-probing),使您更快完成设计的分析与合成。

Mentor Graphics Leonardo Spectrum提供更好的合成能力

Leonardo Spectrum是Mentor Graphics发展的合成工具,它能协助Atmel客户在一个合成环境中使用VHDL或Verilog语言完成FPGA设计,让他们针对工业控制、通 信、宽频、无线与多媒体等应用市场,更轻易的建立和管理FPSLIC设计。LeonardoSpectrum的操作非常简单,又支持各种复杂设计方式,设 计人员可精密控制他们的FPGA设计,并获得最佳设计结果,满足他们的所有设计需求。

LeonardoSpectrum是Mentor Graphics的子公司Exemplar Logic的专业VHDL/Verilog HDL综合软件,简单易用,可控性较强,可以在LeonardoSpectrum中综合优化并产生EDIF文件,作为QuartusII的编译输入。该软 件有三种逻辑综合方式:Synthesis Wizard(综合向导)、Quick Setup(快速完成)、Advanced FlowTabs(详细流程)方式。三种方式完成的功能基本相同。Synthesis Wizard方式最简单,Advanced FlowTabs方式则最全面,该方式有六个选项单,如图所示,分别完成以下功能:器件选择、设计文件输入、约束条件指定、优化选择、输出网表文件设置及 选择调用布局布线工具。

以上每步操作都提供相应的帮助,简单明了。需要注意的是,在输入设计文件时要正确排列文件的次序,将底层文件放在前面,顶 层文件放到后面,这样LeonardoSpectrum软件才能正确地建立数据信息库。综合完成后,可以将输出网表文件 (.EDF)作为MAX+PLUS II或Quartus II的设计输入文件,再完成编译、仿真、定时分析和器件编程等步骤,完成整个系统的设计过程。

Mentor Graphics FPGA Advantage 7.2 (FPGA设计):

http://www.9iv.com/down/soft/2715.htm?eid=217990

Mentor Graphics高端设计工具FPGA Advantage!从设计创建到仿真、综合的高级技术,包括设计的管理、高级仿真调试手段、后仿真、 物理综合等,FPGA 7.2有一个更高的提升!

FPGA Advantage For HDL Design为FPGA设计提供一套集成易用的完整解决方案,涵盖设计的创建、仿真验证、综合、布局布线以及文档和设计的管理。它把Mentor三个强大 的工具紧密结合在一起,HDL Designer Series做设计创建、文档和管理;ModelSim做仿真;Leonardo Spectrum做综合,是业界唯一的FPGA全流程设计工具。FPGA Advantage使您的FPGA设计环境更强大,大幅提高您的总体生产力。

官方网址:http://www.mentor.com/products/fpga_pld/fpga_advantage/index.cfm

Mentor Graphics 公司简介

Mentor Graphics® 是电子设计自动化技术的领导产商,它提供完整的软件和硬件设计解决方案,让客户能在短时间内,以最低的成本,在市场上推出功能强大的电子产品。当今电路板 与半导体元件变得更加复杂,并随着深亚微米工艺技术在系统单芯片设计深入应用,要把一个具有创意的想法转换成市场上的产品,其中的困难度已大幅增加;为此 Mentor提供了技术创新的产品与完整解决方案,让工程师得以克服他们所面临的设计挑战。

Mentor Graphics Precision RTL Synthesis v2005b (EDA综合器):

http://www.9iv.com/down/soft/2018.htm?eid=217990

Mentor Graphics Precision 2005b.91 最新版,简介:

Mentor Graphics Precision RTL Synthesis适应FPGA发展的新一代RTL综合器,具有非常直观的界面、准确的时序分析和先进的优化算法,能同时满足最佳设计结果和最短上市时间 的要求。SDC格式的时序约束加上精确的时序分析引导优化,完成最具挑战性的设计。采用独特的ASE优化算法,自动实现状态机、跨层次和多余组合逻辑的优 化;交互式精确时序分析和约束分析保证完美的结果,集成的原理图清晰地展示综合流程和特殊资源的利用并查询关键路径。

Mentor最新Precision RTL工具实现FPGA与ASIC互转

Actel公司和Mentor Graphics公司近日宣布推出最新版本Mentor Graphics Precision RTL综合工具。据介绍,该工具有助于设计师在使用Actel以Flash为基础上电即行ProASIC Plus系列现场可编程门阵列(FPGA)器件的设计中大幅提升性能。与先前的软件版本相比,使用Precision RTL综合工具的客户预计可提升时钟频率平均达18%。Precision RTL综合工具已完全集成在Actel的Libero 6.0集成设计环境(IDE)中,让设计人员可设定更高的频率,甚至在现有的设计流程中实现更高的ProASIC Plus器件性能提升。

据介绍,此工具经过Actel的测试,涵盖30,000个逻辑单元的多种设计,结果证明这工具可明显提高时钟频率。Precision RTL综合工具是通过配置特定的结构算法,以增强精确的时序驱动综合技术和采用多种优化技术来实现的。

Precision RTL综合工具为复杂的FPGA设计提出了一个崭新方法的定义。该工具基于统一的数据模型,让设计人员进行多角度的交叉探测,以便在分析设计时更好地进行 控制。其直观的调试环境包括增量时序分析工具,可以帮助客户把握下一代FPGA的实施和时序设计挑战,从而缩短设计周期并提高性能。

ProASIC Plus系列器件系统门密度在75,000至100万个系统门之间。ProASIC Plus集精细颗粒和单芯片的类ASIC架构与非易失性Flash配置存储器于一身,是专用集成电路(ASIC)以外的可选方法。这些器件拥有与ASIC 相同的特性,即上电即可运行、低功耗,兼具高度安全性及中子引发固件错误免疫力,并无需额外配置存储器。ProASIC Plus的结构和设计方法支持现有的FPGA及ASIC工具流程,可缩短产品面市时间,让设计人员在FPGA与ASIC方案之间转移。

Mentor Graphics Precision RTL主要特点:

设计界面由流程步骤驱动;

集成对主流布线器的接口;

支持VHDL、Verilog、EDIF的任意组合;

ASE优化,寄存器重定时、跨层次综合;

多时钟、异步时钟分析

What-if时序分析;

未约束分析

Mentor Graphics HDL Designer 2005.2 (电子自动化管理):

http://www.9iv.com/down/soft/1073.htm?eid=217990

设计创建和流程管理系列工具,10月份最新发行!

HDL Designer Series为提高设计效率和设计质量提供了无与伦比的灵活手段和功能。通过图形化、文本或两者的组合,结合IP的引入,快速高效的创建设计,HDL可视 化和统一的HDL风格和文档能力,版本管理为团队设计提供了基础,全面的VHDL、Verilog和mixed-HDL支持适应百万门的FPGA, ASIC和SoC设计。与仿真工具如ModelSim和综合工具如Precision结合提供完整的FPGA/ASIC设计流程。HDL Designer Series包含以下四个系列产品。

HDL Pilot设计管理工具;

HDL Author 设计创建工具;

HDL Detective设计分析、可视化和文档管理工具;

HDL Designer包含以上三个工具的所有功能。

Mentor Graphics HDL Designer 2005.2加快复杂芯片设计的输入与分析

Mentor Graphics HDL Designer 工具套件,为客户带来生产力更高的设计输入、分析与管理功能,包括更强大的联机资料表格,无论设计复杂性如何,都能迅速建立高品质且结构良好的硬件描述语 言。HDL Designer Series可协助工程师迅速输入和分析复杂的ASIC、FPGA和系统单芯片设计,让客户新产品于更短时间内上市。

Mentor Graphics公司HDL Designer Series行销总监Valerie Rachko表示,不管设计工程师采用何种硬描述语言设计方法,HDL Designer Series工具套件都为他们提供一套完整作业环境,使他们能轻易完成硬件描述语言设计、分析和管理。实际应用结果证明,包括Interface- Based Design™在内的多项特色让复杂线路描述更简单;为进一步满足工程师的设计需求,新版本还加强了文件记录、显示、除错与设计管理功能。

以界面为基础的IBD设计方法让复杂设计的线路描述更简单为了让线路设计更简单,以界面为基础的Interface-Based Design(IBD™)设计方法会用观看方便的精简表格来显示线路结构,这个表格编辑环境允许设计工程师迅速指定信号线路,然后产生对应的VHDL或 Verilog结构描述,使用者甚至能以功能方块图的形式来观看IBD描述资料。

为支持IBD设计方法,HDL Designer Series 2004.1提供了多项新功能特色,包括:

◎ 加入和删除电路,并将修改结果传给整个阶层架构

◎ 加入和删除某些阶层,以便调整阶层架构的阶层安排方式

◎ 动态更新IDB与功能方块图窗口的对应内容

◎ 展开或缩合指定的表格行列,让使用者设定自己喜爱的窗口显示格式

◎ 利用鼠标拖曳来调整表格的行列顺序

Debug Detective功能加强

Debug Detective™让HDL Designer Series拥有更强大的硬件描述语言仿真能力,同时还提高ModelSim®设计流程的生产力;Debug Detective会在ModelSim内执行,并以图形或表格来显示硬件描述语言程序代码,进而加强设计除错能力。

Debug Detective的新特色和加强功能包括:

◎ 更强大的状态机器执行结果辨识能力(rendering recognition)

◎ 可规划的探测显示功能

◎ 仿真工具列和ModelSim功能选单提供更多的仿真控制选项

◎ 范围更广的探测变更信息与force控制

关于HDL Designer Series

HDL Designer Series的功能涵盖设计输入与管理程序所有层面:HDL Pilot™提供设计管理;HDL Detective™提供设计分析与文件记录;HDL Author™提供文字与图形编辑以及文件记录;HDL Designer™把单点工具所有功能和更强大文件记录能力结合成单一解决方案;Debug Detective则把除错和设计分析能力提供给ModelSim仿真解决方案。HDL Designer Series同时提供硬件描述语言设计、分析与管理功能,是电子设计自动化产业最完整的工具套件;此外,HDL Designer Series还支持所有常用的仿真与合成工具。

关于 Mentor Graphics

Mentor拥有世界一流的电子软/硬件设计解决方案,为全球最成功的电子与半导体公司提供电子自动设计化的产品与咨询服务;同时,也是今年第五度蝉连美 国的最佳软件技术协助成就奖(STAR Award)的公司。Mentor成立于1981年,去年营收将近6亿美元,全球约雇用 3,100 员工。公司总部位于美国奥勒冈州(Oregon)

Synplicity Certify 6.4 (FPGA原型验证):

http://www.9iv.com/down/soft/1065.htm?eid=217990

Synplicity公司是全球最大的FPGA设计与ASIC验证软件供应商,是全球十大EDA软件公司之一。自1995年在美国硅谷成立 以来,营业额每年以超过80%的增长率提高。公司旗下最著名的FPGA综合软件----Synplify在国内已为广大工程师熟悉和使用。相信其正式进入 中国以后,随着服务与技术支持力度的提高,定将使广大工程师受益

Synplicity目前主要产品有HDL综合工具:Synplify,高级HDL综合工具:Synplify Pro, HDL物理综合工具:Amplify,及ASCI到FPGA转换工具: Certify等

Synplicity公司出品的Certify是RTL级多片分割与综合ASIC原形验证技术解决方案。为了提高复杂芯片一次成功的可能性, Certify为客户提供了利用多片FPGA芯片快速而详细的调试和验证大规模ASIC芯片的解决方案。Certify可以快速地在RTL级创建原型,并 利用FPGA来实现。同时,Certify提供给客户在实时条件下联合调试软硬件的能力。另外,Certify又加入了DW和门控时钟的支持,这样低功耗 设计(手持类芯片)的芯片验证就不存在问题了

I-Logix Rhapsody 6.2 (嵌入式仿真开发)

下载地址:http://www.9iv.com/down/soft/1100.htm?eid=217990

或者http://lib.verycd.com/2006/01/04/0000083110.html

Rhapsody 6.2高端嵌入式开发工具!于2005.12最新发布!增强图形处理能力与程序开发引擎!它为嵌入式软件的开发提供了一个“四化”的支撑平台,即可视化、 工程化、自动化和团队化。它提供了可视化的开发环境,贯穿了工程化的设计思想,使用了自动化的开发模式,并支持团队化的协作开发。

I-Logix Rhapsody在业界享有盛誉。美国国家航空暨太空总署(NASA)的火星探路者航天器就是运用Rhapsody在VxWorks上开发应用程序。

官方网址:http://www.ilogix.com/homepage.aspx

The newest release of Rhapsody 6.1, offers a rich feature set to users with key enabling technologies that empower designers and developers to use SysML,

DoDAF, CORBA and in a natural, easy-to-use tool environment. Loaded with enhancements and new features to make a seamless and efficient environment for

systems, software and testability, the new tool family represents a “best of breed” solution to users.

根据第三方的报告,Rhapsody正在迅速成为国防/航空航天领域首选的MDD(模型驱动开发,Model Driven Development)开发环境,在一系列项目中被作为主要开发工具来使用,如Joint Strike Fighter (JSF), Future Combat Systems (FCS) and F-22等,同时在通讯、医疗、汽车和消费电子等领域赢得快速持续的增长。

I-Logix公司的Rhapsody系列产品将实时嵌入式应用软件的设计和开发带入了革命性的新阶段。Rhapsody 是一种基于统一建模语言UML(Unified Modeling Language? ) 的可视化编程环境。通过特有的把UML各类视图映射为具体目标机程序语言的技术,Rhapsody提供给你一个完整的用于复杂实时嵌入式应用软件从分析、 设计一直到代码实现和软件测试的开发环境。Rhapsody采用基于UML模型的开发方法,通过从设计模型中直接生成高质量的代码,将开发的重心从编码转 移到设计上来,这种自动化的软件开发方法有效的促进了团队合作,极大的提高了软件重用率和代码质量,大大缩短了整体的开发时间,代表了软件开发自动化的发 展方向.

业界领先的Rhapsody是一个模型驱动的开发环境,它以UML2.0为基础,使大小不同的项目都能够通过可视化 建模的方法分析、设计、实现和测试自己的工作,构建和配置实时嵌入式应用。Rhapsody专为嵌入式市场的特殊需求设计和优化,包括实时系统的行为语 义,实时操作系统的支持,无操作系统的实时应用支持,遗产代码的逆向工程、设计级的调试、高效的代码自动生成(C、C++、Ada、Java)和文档自动 生成等。客户报告说,Rhapsody使他们大大缩短了开发周期,哪怕在初次使用该工具的情况下。

Rhapsody6.0与以往版本相比有几个突破性的改进:

不仅支持软件开发的面向对象方法,也支持传统的面向功能分解的结构化方法。 Rhapsody独创地扩充了UML使得面向功能和面向对象的设计技术和谐共存于同一个环境之中。

不仅适合软件开发者的需要,也适合作为系统设计的工具来使用。

对C语言的支持进一步强化。无论32位嵌入式应用还是8位/16位应用,无论是否有实时操作系统,Rhapsody5.0都提供强有力的开发手段。

I- Logix的首席讲师Bruce Powel Douglass博士在近期来华访问的演讲中,介绍了Rhapsody的几个重要特性:完全遵循UML标准、独特的模型/代码相关性技术以及图形化的、设 计级的调试和验证技术。此外,Rhapsody还能支持大项目开发对于信息共享的需要。每个用户在私有工作区维护自己的设计模型,Rhapsody将所有 设计模型以包的形式存储在项目内,并提供管理和划分功能。团队之间可以通过工作区的直接导入以及现有的配置管理工具实现协同开发。

UML的忠实“追星族”

UML(统一建模语言)给软件界带来的震动不亚于六级地震,它与OOAD(面向对象分析和设计)工具的结合,更使软件工程思想的实现往前走了一大步。 Rhapsody是业界第一个遵循UML语言的面向对象设计工具。总部在美国的I-Logix是OMG(对象管理组织)的成员,并且参与了UML标准的制 订。UML在1997年11月成为OMG采纳的标准建模语言,Rhapsody在1998年2月就开始提供对UML的支持。

在Rhapsody中,设计者可以创建UML支持的9种图:顺序图、协作图、类图、对象图、用例图、构件图、状态图、活动图和实施图,其中类图和对象图在 Rhapsody中统称为对象模型图。不同的图侧重于模型的不同方面,简化了设计过程。Rhapsody还提供了一整套UML设计元素,用来构造不同的 UML设计图表,所有的图表共同构成了一个反映设计的模型。

可以从浏览器中检查整个模型,也可以用模型检查器检查模型的一致性以及语法的正确性。

虽然不能提供所有的UML功能,但Douglass博士在介绍Rhapsody的时候强调,I-Logix可以保证只要是Rhapsody提供的功能,都 遵循UML标准,而某些OOAD工具会提供一些UML标准之外的专有功能。I-Logix认为,提供一些专有功能模块虽然丰富了工具的内容,但削弱了 UML的通用优势。完全遵循UML标准可以在统一标准的基础上对嵌入式系统进行完全的和精确的分析。

自动化代码生成

Rhapsody采用基于模型的开发方式,能从设计模型直接生成可运行的应用程序和基于特定平台的、产品级的、高质量代码。将开发的重心从编码转移到了设计,显著地提高了总体开发效率。

其代码生成框架的最大特点在于模型/代码相关性。代码和模型作为同一设计的不同视图而共同存在,当改变其中任意一个时,另外一个也随之自动更新,这使得设计模型总是和实际代码一致。

Rhapsody提供了150多个属性用来定制代码的生成,其中包括生成可运行程序或特定的文件(如源文件、Makefile、库等)、指定参与某个编译 的具体元素、在执行速度和代码尺寸之间进行取舍、指定生成代码的风格、选择实时时钟或模拟时钟等。在Rhapsody中还可以将经常使用的配置属性保存下 来,以简化由于不同需要而生成不同代码的过程。也可以对代码生成框架进行扩充,以满足特定的需求。灵活的代码生成机制在缩短开发周期的同时,提高了代码质 量。

因为Rhapsody专门针对嵌入式开发,所以对实时性能的支持是它的重要组成部分。Rhapsody的实时框架提供了一套为实时嵌入式应用专门优化的设 计模板,该实时框架完全开放,用户可以根据特定的操作系统以及应用环境进行定制。应用程序的编写与自动生成都基于具有统一接口的实时框架,开发出来的应用 软件与具体的平台无关。

边设计边调试

所谓设计级调试能力就是允许在设计的同时对设计进行调试和验证,这样设计者可以在更短的时间内得到被证明是正确的设计方案。通过使用可运行的设计模型, Rhapsody使用户在调试和验证阶段仍然可以将工作重点放在设计上,消除了许多冗长乏味的代码级调试时间。

Rhapsody实时运行框架在生成的代码中提供了调试和平台相关的接口,从而可以在设计环境中监视和控制代码的运行。开发人员只需在代码生成过程中选择 适当的调试方式,就可以使用Rhapsody的代码级调试能力。调试模式可以设置为“动态”和“跟踪”。 在“动态”模式中,可以执行设置单步命令、设置断点、产生事件等操作,被调试的程序既可以在本地运行,也可以在目标系统上运行,运行环境可通过 TCP/IP与开发环境相连。Rhapsody提供了一个可视化的编译信息输出窗口,只需要双击编辑器中的错误信息,即可直接跳到程序中出现错误的地方。

“动态”模式最强大的功能是同时从多种角度展示被调试的程序段的动态信息,如顺序图、状态图、浏览器中的属性值和关系等。通过动态的顺序图显示各个实例之 间的交互,可以使开发者对系统行为有更为深刻的理解和体会。当调试完成后,可以很快地重新生成代码以代替调试代码,或通过宏定义使调试代码无效。

I-Logix Statemate 4.0 (复杂嵌入式自动解决)

下载地址:http://www.9iv.com/down/soft/1257.htm?eid=217990

美国I-Logix公司的Statemate 是其多年在从事众多实际工程的基础上提炼出来的一个工具软件包,它是目前世界上最强大和最完整的面向功能需求的系统级自动设计软件包,它定位于复杂的嵌入 式系统或实时系统,其宽广的工程应用范围和针对系统层设计的专业技术是其他在系统级设计的工具(如Mathworks公司的state flow,simulink,matlab;ISI 公司的Matrixx, BetterState等)所无法比拟的。而飞机的航空电子与飞行控制系统正是这样一个复杂的实时嵌入式系统,利用Statemate MAGNUM从事其设计是非常合适的。

Statemate 软件运用最先进的行为图形建模方法和原型生成技术,使系统设计的工程师能够在规范阶段就可以对整个系统的行为方式、功能要求、控制方式等进行可视化的调 试、验证、发现和纠正规范文档中相应的模糊、冗长、错误的地方,从而避免在产品的物理原形阶段或测试阶段才发现上述问题。

当今嵌入式系统设计者面临着大量复杂性设计的挑战。这类挑战来自于设计内容的增加,多变的新特征,模糊的设计参数以及用户不断增长的需求。这些挑战即使是 对那些装备最精良的设计小组而言也是远远超出了他们的技术能力。更令人惊讶的是,还有大部分复杂系统是用文本形式进行描述的,这种非正规而又不可测试的交 流方法常常导致代价高昂的修改。大量的研究显示在集成期间纠正一个错误的花费将是在规范制定期间的10至1000倍

当然,产生完整、准确的规 范仅仅是整个成功的一半,现在有一种全新的基于模型的迭代式的方法可以解决以上问题,它允许用户创建一个可视化的、图形化的系统规范,清晰、准确地反映指 定系统预期的功能和行为,找到由于需求不明确造成的代价高昂的错误,并尽早地在设计阶段中加以改正。这就是--Statemate MAGNUM。

I-Logix Statemate具有以下几个特点:

采用基于模型的迭代式"V"型开发过程进行系统或分系统总体设计。

运用了最先进的行为图形建模方法、先期验证、快速原型、测试用例自动生成、代码自动生成、文档自动生成、实时分布式系统规划、需求追踪、配置管理等技术。

使设计复杂嵌入式系统的工程师在总体方案阶段就可以对整个系统的行为方式、功能要求、控制方式等进行可视化的调试、验证。

在软件功能上,覆盖了从系统需求分析到产品级自动化代码实现的嵌入式系统设计全过程。

解决了规范系统设计方法、总体方案早期验证、嵌入式软件设计自动化等诸多复杂嵌入式系统开发设计问题。

I-Logix Statemate 的建模语言

在Statemate MAGNUM中,设计者可使用六种可视化建模语言,即人机交互面板(Panel),用例图(Use Case Diagram)、顺序图(Sequence Diagram),连续控制图(Continuous Diagram),离散状态图(State chart)和功能结构图(Activity Diagram),从而有效地捕捉系统需求,实现对包括连续和离散行为的混合系统的描述和设计。

I-Logix Statemate 的模型检查和验证技术

Statemate MAGNUM的ModelChecker和ModelCertifier模块是基于最先进的state of the art格式验证技术设计的,从而可以非常高效的完成在传统测试下十分复杂的测试验证工作。

I-Logix Statemate 测试用例自动生成技术

Statemate MAGNUM是ATG模块可根据设计模型自动生成高覆盖率的测试用例及测试数据,可解决在后期开展测试工作时,测试人员根据系统需求文档人工设计大量繁琐测试用例。

I-Logix Statemate 的仿真技术

仿真时的一个重要工具是人机交互面板,因为它与设计图相绑定,可以非常直观的显示仿真结果。此外,仿真器环境提供了所有传统的调试装置,如波形、监视器和调试窗口等。

I-Logix Statemate 的代码自动生成技术

Statemate MAGNUM的代码生成器能把Statemate中设计的模型自动为软件开发者转换成高质量的C或Ada码,Statemate MAGNUM自动产生的代码实际上就是系统的原型代码,它比传统的手写原型代码的方式快几个量级,并且保证了原型符合设计规范。有了这种代码,即使脱离软 件环境,也能为客户演示系统的虚拟原型(用面板的方式表现)。

I-Logix Statemate 的嵌入式快速原型技术

在一个复杂系统的设计过程中,工程师们往往要在系统集成期间才会发现系统设计上的错误。为此,工程师往往需要花费大量的时间和金钱来修正错误。Statemate MAGNUM嵌入式快速原型技术能帮助避免这种情况。

I-Logix Statemate 的自动文本生成技术

Statemate MAGNUM的文档生成器能自动摘录包括图形和文字在内的所有模型数据,然后输出成为标准的或用户自定义的文档,便于整理和归类。

I -Logix是一家专门从事实时嵌入式系统开发工具与方法研究,并居于世界领先地位的公司。公司总部设在美国Andover, Massachusetts。I-Logix Statemate MAGNUM和Rhapsody支持从概念到代码的整个设计过程,通过一个迭代的方法来联系设计过程所涉及的每个方面,包括需求分析、行为验证、文档生成 和代码生成。I-Logix的产品能使工程师们图形化地仿真嵌入式系统的行为和功能、进行系统分析和验证并自动生成多种语言的代码。I-Logix运用传 统的和基于Web的技术,将从概念到代码的整个设计过程结合起来。I-Logix的解决方案能使用户加速新产品研发、增强竞争力并节省时间和资金。

CodeWarrior

提供统一的图形用户界面来集成各种开发工具,支持多种主机平台、多种编程语言、多种处理器和多种实时操作系统,称为下一代集成开发环境。

CodeWarrior集成环境包括以下几个功能模块:编辑器、源码浏览器、搜索引擎、构造系统、调试器、工程管理 器。编辑器、编译器、连接器和调试器对应开发过程的四个主要阶段,其它模块用以支持代码浏览和构造控制,工程管理器控制整个过程。该集成环境是一个多线程 应用,能在内存中保存状态信息、符号表和对象代码,从而提高操作速度;能跟踪源码变化,进行自动编译和连接。该集成环境的运行需要24M到32M内存。

CodeWarrior集成环境支持多种主机平台,在不同平台上具有相同的图形用户界面,其源文件和工程文件可在不 同平台之间交换。使用CodeWarrior集成环境,开发语言有多种选择,支持C,C++,Object Pascal,Java等高级语言,也支持汇编语言。

CodeWarrior一个重要的特点是其plugin设计:根据不同开发IDE的需要,提供特殊的服务软件。该软 件以一个独立于IDE的文件方式提供,比较典型的有Windows下的DLL文件,Mac OS和UNIX下的共享库文件等。该项功能如同Web浏览器或Adobe Photoshop的plugin功能。这样,只要提供特殊的plugin文件,就可以自动增加IDE的功能。CodeWarrior目前能识别多种 plugin:compiler,linker,pre-linker,post-linker,preference panel,version control,APIs for debugger等。Metrowerks公司已有近200个不同的plugin在应用。

Plugin通过一个中间平台和IDE通信,Metrowerks公司为该设计提供完整的文档和应用编程接口,从而方便其他开发人员开发可完整集成进CodeWarrior的特殊功能组件。

在plugin设计结构下,用户应用Codewarrior时,既可采用Metrowerks公司集成的工具,也可采用第三方工具,和自己设计的工具,以适合不同的开发需要。CodeWarrior支持不同的主机平台、编程语言、处理器和目标操作系统。

对 CodeWarrior* IDE 的详细了解,请见其产品主页。

Windows 95/NT, Mac OS, Solaris

683xx, 80x86, ARM, MC680x0, MIPS, NEC Vxx, Pentium, PowerPC, SuperH :

Metrowerks Inc.

Ti Code Composer Studio v3.1 白金版(强大电子开发):

http://www.9iv.com/down/soft/1398.htm?eid=217990

CCStudio v3.1德州仪器智能化集成开发环境适于多场所、多处理器项目的DSP应用开发Code Composer Studio新版本使DSP应用开发更快速、更容易、更可靠:Code Composer Studio v3.1 Platinum (For All Ti DSP支持所有版本)最新版2005.6月中旬发行。功能相当强大。经过广大用户使用,Code Composer Studio v3被证实是用于DSP应用开发的最佳软件,其性能处业界领先的地位,是DSP开发者必备的一款软件!价格: $3,595.00.

TI Code Composer Studio (CCStudio)是TI eXpressDSPTM实时软件技术的重要组成部分,它可以使开发人员充分应用DSP的强大功能。随着TI的TMS320C5000(C5K)和 TMS320C6000(C6K)DSP平台的应用范围不断扩大,已经由其应用于下载视频流的手持因特网接入产品扩展到蜂窝通信网络和光网络的通信基础设 施,eXpressDSPTM也便获得了越来越多软件工程师的青睐。

eXpressDSP还包含了DSP/BIOS可伸缩内核,TMS320TMDSP标准算法的应用互操作性和可重复使用性以及400多家第三方厂商支持。大部分厂商提供eXpressDSP兼容算法、即插式应用以及种类繁多的硬件配件和咨询服务。

TI Code Composer Studio 3.1 Platinum Edition For All Ti DSP

(加快优化DSP软件的速度)

TI Code Composer Studio 3.1 Platinum Edition For All Ti DSP包括以下平台:

Ti code composer studio for c6K (TMS320C6000 系列)

Ti code composer studio for c5K (TMS320C5000 系列)

Ti code composer studio for c2K (TMS320C2000 系列)

Ti code composer studio for TMS470(TMS470 Series(ARM))

Ti code composer studio for OMAP(OMAP Processor)等。。。

嵌入式编程人员现可利用TI的Code Composer Studio加快优化DSP软件的速度,前瞻性的综合建议及易于使用的调整工具能够帮助开发人员简化并加速代码优化进程。这些强大但易于使用的功能不仅能 够缩短开发时间,而且能够帮助编程人员充分发挥 TI TMS320C6000 DSP 平台器件的全部潜能。

Code Composer Studio 3.1实现了多场所的连通性,极大地改进了基于TI业界领先的TMS320C5000TM和TMS320C6000TM DSP平台单处理器或多处理器代码的开发、优化及其调试工具的性能。先进的应用,如图像与视频、宽带接入、3G无线通信及其它一些融合高性能的技术将得益 于Code Composer Studio v3.1的可靠性及其快捷的开发时间。

智能化使软件开发更加轻松快捷

Code Composer Studio 3.1能够使开发人员编制出更多面向高级DSP应用的、紧凑的高性能代码。通过实时接入的DSP开发者之家网站,内置的Update Advisor对最新的工具、驱动程序及其技术进行自动的流线式管理。只要确保代码和功能调用的正确输入,凭借编辑器程序中的Dynamic CodeMaestro技术即可快速生成C和C++编码。

TI 的 eXpressDSP™ 产品市场营销经理 Mike Trujillo 说:"通过充分利用 CCStudio 的工具与功能,编程人员能够大大缩短应用开发的时间。使用 CCStudio 生成的高度优化代码,工程师能够最大限度地发挥高性能 DSP 的全部功能,或者,在其它情况下能够以成本更低的器件来满足其应用需求。"

无缝管理大型的多场所、多处理器项目

---- Code Composer Studio v3.1使开发人员能够无缝管理任何复杂程度的项目,其项目管理器通过一个集成版本的控制接口与通用资源控制器连接,管理着成千上万的文件。同时支持外部 "文件制作"功能,使项目能够在PC和UNIX平台上交叉运行。工作于同一项目的开发团队,不再需要集中到一个地方,而可分散在不同的场所。他们可以通过 采用一个改进的产品开发流程,就可实现同一组项目文件的共享。于是可以使他们的开发周期缩短数周,并获得时间上提前于竞争对手推向市场的优势。

---- 对于那些希望把业界领先的C6000TM DSP平台的高性能与C5000TM DSP平台的低功耗相结合的系统开发者来说,Code Composer Studio v3.1为使其同时调试混合多处理器成为了可能。Code Composer Studio v3.1还增加了实时数据交换(RTDXTM)仿真功能,可支持来自任何地方的2至50个C5000和C6000 DSP器件同时运行。此外,支持RTDX的仿真器还实现了实时DSP/BIOSTM仿真调试,该高级调试功能可以使开发人员更深入地了解DSP代码在硬件 或仿真状态中的运行情况。

关于TI:

德州仪器 (TI) 是全球领先的数字信号处理与模拟技术半导体供应商,亦是推动因特网时代不断发展的半导体引擎。

----作为实时技术的领导者,TI正在快速发展,在无线与宽带接入等大型市场及数码相机和数字音频等新兴市场方面,TI凭借性能卓越的半导体解决方案不断推动着因特网时代前进的步伐!

----TI预想未来世界的方方面面都渗透着 TI 产品的点点滴滴,您的每个电话、每次上网、拍的每张照片、听的每首歌都来自 TI 数字信号处理器 (DSP) 及模拟技术的神奇力量。

----德州仪器(Texas Instruments),简称TI,是全球领先的半导体公司,为现实世界的信号处理提供创新的数字信号处理(DSP)及模拟器件技术。除半导体业务外, 还提供包括传感与控制、教育产品和数字光源处理解决方案。TI总部位于美国得克萨斯州的达拉斯,并在25多个国家设有制造、设计或销售机构。

TI为全球众多的最终用户提供完整的解决方案

TI在DSP市场排名第一

TI在混合信号/模拟产品市场排名第一

1999年售出的数字蜂窝电话中,超过半数使用的是TI的DSP解决方案。其中,诺基亚、爱立信、摩托罗拉、索尼等世界主要手机生产厂商均采用TI的DSP芯片

全球每年投入使用的调制解调器中,有三分之一使用TI的DSP。TI是世界上发展最快的调制解调器芯片组供应商

全球超过70%的DSP软件是为TI的DSP解决方案而编写

TI占有北美图形计算器市场80%以上的份额

TI在世界范围内拥有6000项专利