- 1设计模式-组合模式_组合设计模式菜鸟

- 2Windows系统安装onlyoffice_windows安装only office

- 3Flask项目快速部署_flask部署到服务器

- 4深入理解Linux内核-磁盘IO-I/0体系结构和设备驱动程序

- 5Win10内置Ubuntu重启Docker服务_win10重启docker服务

- 6拜占庭容错共识(PBFT)

- 7数智赋能内涝治理,四信城市排水防涝解决方案保障城市安全运行

- 8Github authenticator登录问题_github-recovery-codes

- 9深入学习Java:关于List下标越界源码分析_removeall 避免数组下标越界

- 10编写测试用例标准_测试用例设计要求连贯性

沧小海的《xilinx的A7系列芯片资源学习笔记》之第一部分:I/O BANK(二)_idelay2 cinvctrl

赞

踩

2.2.2 IDELAYE2

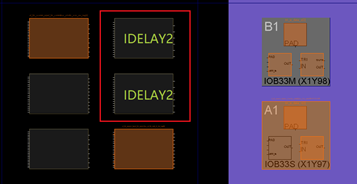

每个引脚都有对应的IDELAY2模块,如下图所示,它的作用就是对输入数据进行延迟指定时间。

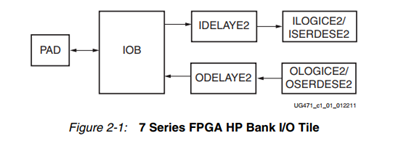

这个“IDLEAYE2”是可旁路的,可以直接从IOB到LOGICE2,也可以经IDELAYE2。

如下图是IDLEAYE2的原语,简单介绍下各个参数和接口信号

一、参数部分

1、CINVCTRL_SEL:

调整输入时钟“C”的极性。

2、DELAY_SRC

数据源的选择,是内部数据还是来自IO的数据。也就是“DATAIN”和“IDATAIN”选择

3、HIGH_PERFORMANCE_MODE

减少输出抖动,默认~

4、IDELAY_TYPE

用来设置延时类型,有FIXED、VARIABLE、VAR_LOAD和VAR_LOAD_PIPE四种。主要分为三类,一是FIXED是设置抽头延迟值固定为IDELAY_VALUE属性设置确定的抽头数,配置后无法更改。二是VARIABLE是将其设置为可变抽头,可以通过设置CE = 1和INC = 1来增加,也可以通过CE = 1和INC = 0来减少,递增/递减操作与C同步。三是VAR_LOAD和VAR_LOAD_PIPE,当IDELAY_TYPE属性设置为VAR_LOAD或VAR_LOAD_PIPE时,可变抽头延迟可以更改并动态加载。可以通过设置CE = 1和INC = 1来增加抽头延迟,或者通过CE = 1和INC = 0来减小抽头延迟,递增/递减操作与C同步。在此模式下,LD引脚加载CNTVALUEIN中显示的值。VAR_LOAD模式或先前在VAR_LOAD_PIPE模式下写入管道寄存器的值。 这样可以动态设置抽头值。

5、PIPE_SEL

通道模式选择。 仅当使用VAR_LOAD_PIPE操作模式时,才应将此属性设置为TRUE。

6、REFCLK_FREQUENCY

设置时序分析器用于静态时序分析的抽头值,可以为 190到210、290 到310,390到410这几种,但不同系列不一定都能设置,例如A7就不能设置390到410MHZ。

7、SIGNAL_PATTERN

时钟和数据信号具有不同的电气特性,因此在IDELAY链中累积了不同的抖动量。 通过设置SIGNAL_PATTERN属性,用户可以使时序分析器在计算时序时适当考虑抖动。 时钟信号本质上是周期性的,没有连续的1或0的长序列,而数据本质上是随机的,并且可以具有1和0的长序列和短序列。

8、IDELAY_VALUE

IDELAY_VALUE属性指定抽头延迟的初始数量。可能的值为0到31之间的任何整数。默认值为零。 重置抽头延迟时(通过置位LD引脚),抽头延迟的值将恢复为IDELAY_VALUE。 在可变模式下,此属性确定延迟线的初始设置。 在VAR_LOAD或VAR_LOAD_PIPE模式下,不使用此属性,因此延迟线的初始值始终为零。

二、接口信号部分

1、CNTVALUEOUT

用于报告已加载的抽头值。

2、DATAOUT

经过延迟的数据输出

3、C

IDELAYE2原语的所有控制输入(REGRST,LD,CE和INC)都与时钟输入(C)同步。当以VARIABLE,VAR_LOAD或VAR_LOAD_PIPE模式配置IDELAY时,必须将时钟连接到该端口。 C可以在本地取反,并且必须由全局或区域时钟缓冲器提供。 如果ODELAYE2原语与IDELAYE2原语在同一I / O库中使用,则C必须对两个原语使用相同的时钟网络。

4、CE和INC

可参考参数设置的“IDELAY_TYPE”部分说明

5、CINVCTRL

CINVCTRL引脚用于动态切换C引脚的极性。 这是在毛刺不是问题的应用中使用的。 切换极性时,请勿在两个时钟周期内使用IDELAY控制引脚。

6、CNTVALUEIN

CNTVALUEIN引脚用于动态切换可加载抽头值

7、DATAIN和IDATAIN

是输入信号,DATAIN是来自IOB,IDATAINDATAIN输入由FPGA逻辑直接驱动,提供逻辑可访问的延迟线。

8、LD

在VARIABLE模式下,LD加载由IDELAY_VALUE属性设置的值。IDELAY_VALUE属性的默认值为零。

在VAR_LOAD模式下,LD加载由CNTVALUEIN设置的值。

在VAR_LOAD_PIPE模式,IDELAY加载端口LD加载当前在管道寄存器中的值。 流水线寄存器中存在的值将是新的抽头值。

使用默认值时,LD端口充当ILDELAY的异步复位。LD信号为高电平有效信号,并与输入时钟信号(C)同步。

9、LDPIPEEN

使能加载pipeline register

10、REGRST

在VAR_LOAD_PIPE模式下,复位pipeline register。

例如使用IDLEAY2的“FIXED”模式

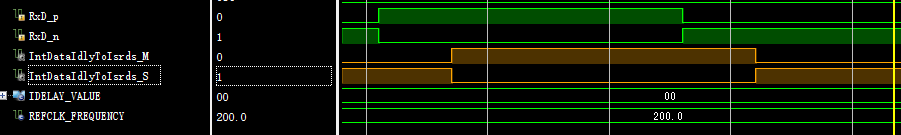

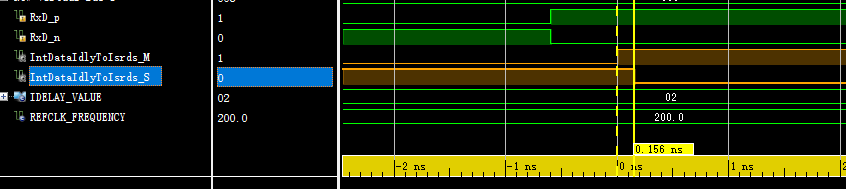

REFCLK_FREQUENCY设为200M,IDELAY_VALUE这为0,可看下时序图如下,无相位差

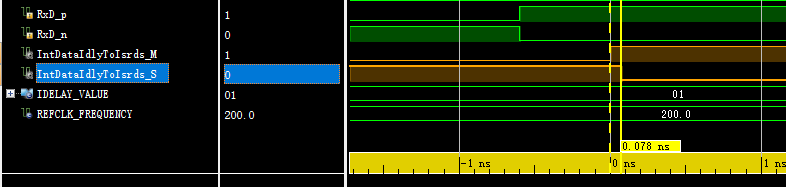

DELAY_VALUE=1,相差78ps

DELAY_VALUE=2,相差156ps

DELAY_VALUE=31,相差2418ps

故延时公式为(以PS为单位)((1000/(REFCLK_FREQUENCY*2))/32)* IDELAY_VALUE

2.2.3 IDELAYCTRL

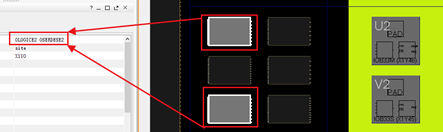

每一个BANK都有一个IDELAYCTRL,如下图所示,用来对该BANK的所有IDLEAYE2和ODLEAYE2的校准。

时序图如下所示,高电平复位,时钟即为延时所用的时钟。

2.2.4 OLOGIC

如下图所示,每个IOB都有一个OLOGICE2,对于HP则是OLOGICE3。

如下图可以看出OLOGIC的两条输出路径,一是经过触发器,另一是逻辑输出。

主要阐述下输出的DDR模式,这个与IOGICE2类似。原语如下:

DDR_CLK_EDGE:

可以选择"OPPOSITE_EDGE" 和"SAME_EDGE"