热门标签

热门文章

- 1Linux环境下搭建 Jmeter+Ant+Jenkins 接口自动化持续集成平台_linux系统jdk+jmeter+ant+jenkins+git接口持续自动化平台搭建

- 2jenkins修改国内镜像_修改jenkins默认更新镜像

- 3Git更新远端分支到本地_git 更新远程分支

- 4DS18B20温度传感器代码(stm32)_stm32ds18b20完整代码

- 5git 报错:git@github.com: Permission denied (publickey).fatal: 无法读取远程仓库。

- 6大学生php实训总结_php实训报告.doc

- 74.网络爬虫—Post请求(实战演示)_爬虫post

- 8线性神经网络-线性回归_神经网络线性回归

- 9应用安全系列之二十八:随机数_那些属于不安全的随机数接口

- 10openstack云计算平台(6)--Dashboard(提供web图形化管理界面)

当前位置: article > 正文

ZYNQ 最小系统搭建并测试_zynq dram test

作者:很楠不爱3 | 2024-04-24 10:31:16

赞

踩

zynq dram test

zynq最小系统包括DDR3,ARM ,UART,主要是PS部分

主要步骤:

第一步:选芯片类型

第二步:添加ZYNQ ip核,进行必要的的配置

1.时钟频率:PS频率为33.333MHz,PL一般配置为100MHz,PS为666.66666MHZ,DDR频率为533.333MHZ;

2.DDR内存型号,必须配置正确,否则SDK运行可能会崩溃;

3.bank1 电压为1.8V,

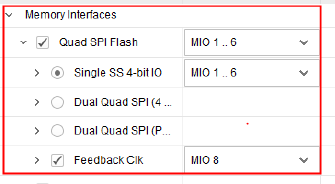

4.QFLASH配置,便于烧写程序。

5.以太网配置,勾选上MDIO;SD0卡配置,勾选上CD信号;UART1勾选上,上述几个都是连接在PS的mio引脚上。

第三步:生成output文件,生成top文件,编译生成bit文件,导出SDK。

第四步:测试,分别生成helloworld应用文件,lwip Echo server;Memory Tests;zynq DRAM tests文件进行测试。

ZYNQ的一些小技术:

1.添加已有IP核目录。

2.ip核的引脚引出去采用,CTRL+T,可修改引脚名字。

3.chipscope 分析可用的几种方式:

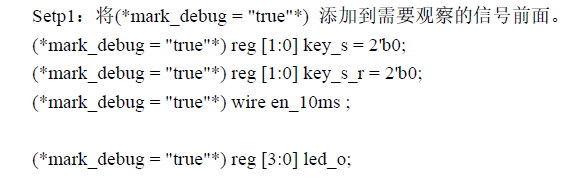

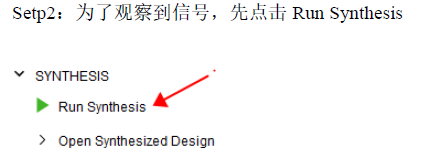

(1)(*make_debug="ture"*)

(2)用ILA逻辑分析IP核

选择native,设置观察信号个数,深度,数据宽度。在block里面直接连线或者top程序中例化ip核。

(3)用虚拟VIO ip核。

设置输入,输出信号个数,数据位宽,初始化值。

(4)直接在AXI 线上debug,自动配置会产生ILA核。

个人习惯喜欢用ILA方式。这几种都是要生成bit 文件,加载SDK应用文件之后,才可调试分析信号。

4.SDK调试工具栏

5.查看内存

6.SDK设置字体

代码编号显示:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/很楠不爱3/article/detail/478938

推荐阅读

相关标签