- 1ESP Multi-Room Music 方案:支持音频实时同步播放 实现音乐互联共享_多音箱音频同步

- 2运行代码提示could not find function “gwasvcf_to_TwoSampleMR“

- 3基于人工噪声的无线通信物理层安全研究_人工噪声增强物理层安全

- 4langchain实战-hello world

- 5工作笔记01.ROS环境安装并编译cartographer_failed to process package 'cartographer': command

- 6mysql的表导出er关系图_使用PowerDesigner导出MySql数据库的表结构生成ER图-Go语言中文社区...

- 7Github Benefits 学生认证/学生包 新版申请指南_guthub学生会员

- 8玄子Share-网络层协议介绍

- 9AI新宠Arc浏览器真可以取代Chrome吗?_cat chrome ai浏览器 谷歌

- 10通过pycharm使用git和github的步骤(图文详解)_pycharm 菜单如何展示git

TQ15EG开发板教程:开发板Vivado硬件设置_vivado ddr4 频率设置

赞

踩

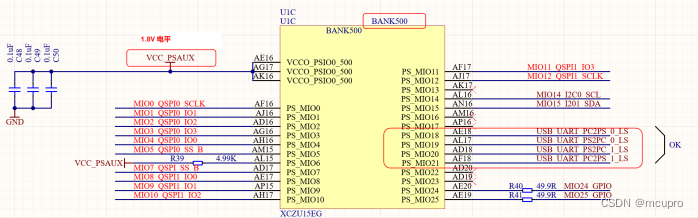

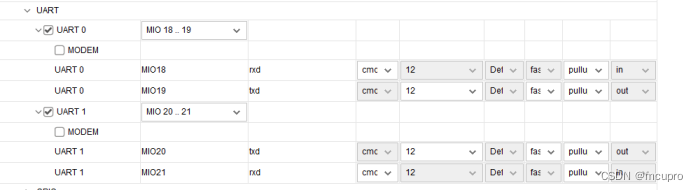

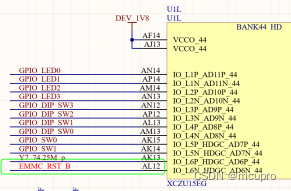

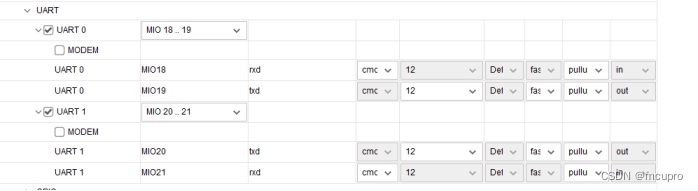

1,串口的配置

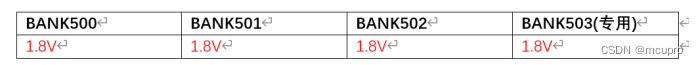

PS端有2个串口,在BANK500, 1.8V IO电平

| 管脚名称 | 电平 | 说明 | ||

| UART0 | RX | MIO18 | +1.8V | MPSOC方向看 |

| TX | MIO19 | +1.8V | ||

| UART1 | RX | MIO21 | +1.8V | |

| TX | MIO20 | +1.8V |

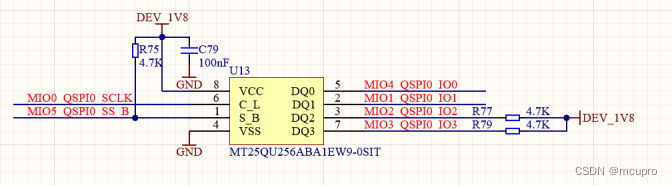

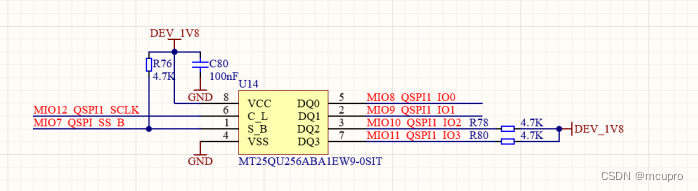

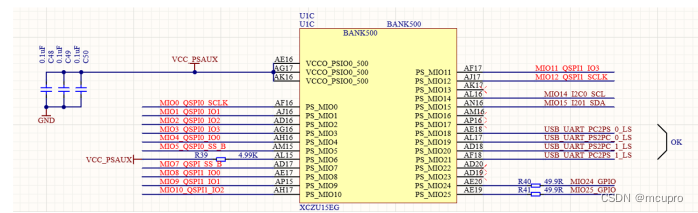

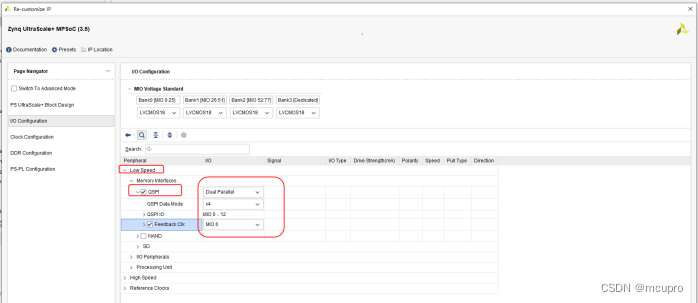

2,QSPI的配置

采用2片MT25QU256 拼接成8bit的QSPI存储系统。采用1.8V供电

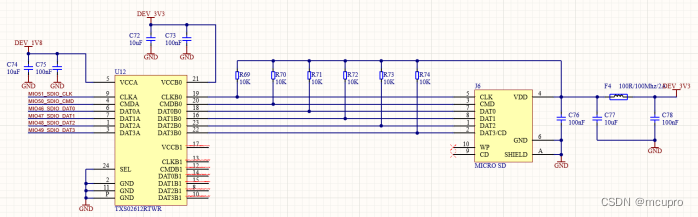

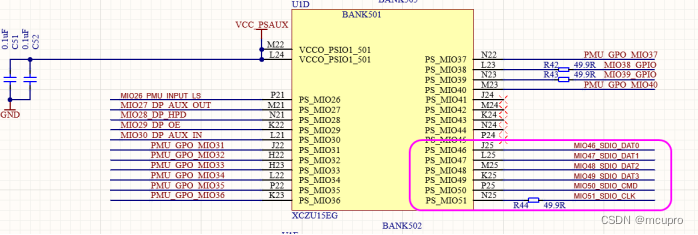

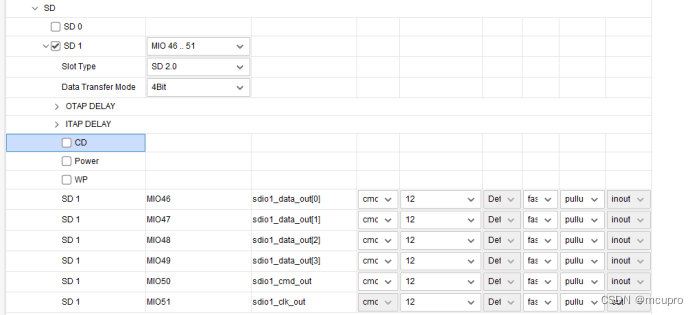

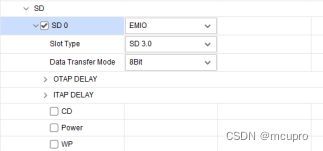

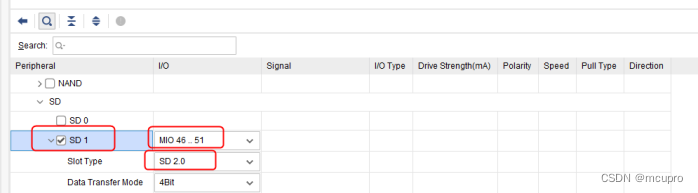

3,SD卡的配置

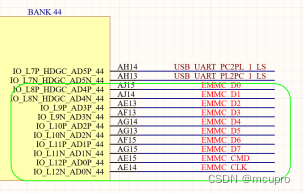

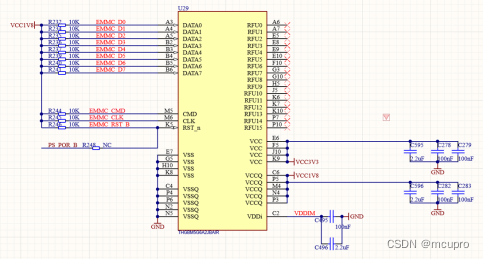

4,EMMC的配置

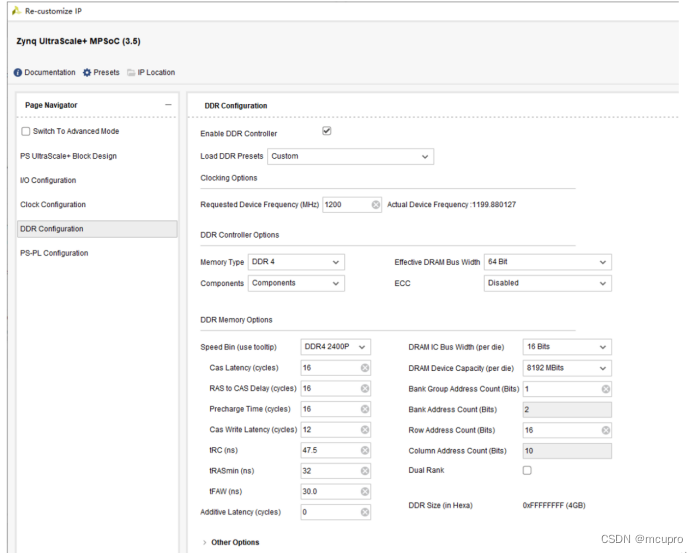

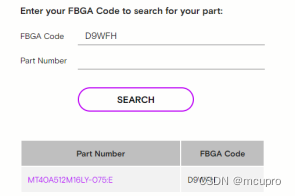

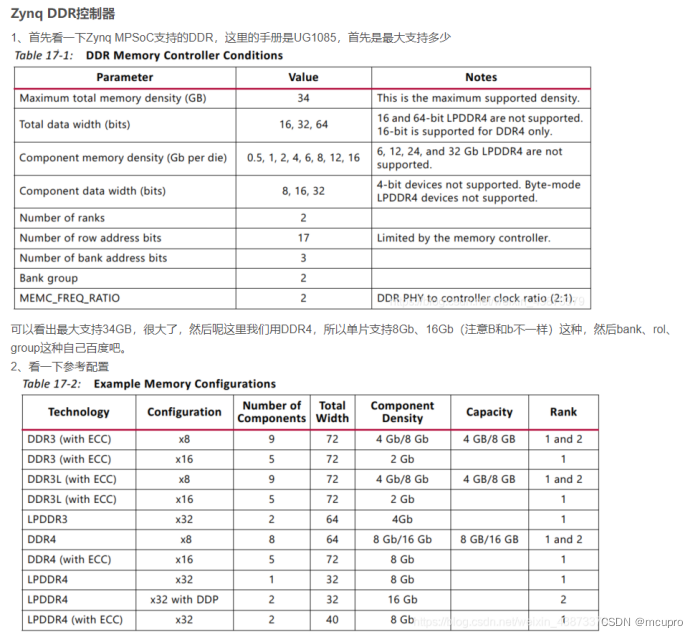

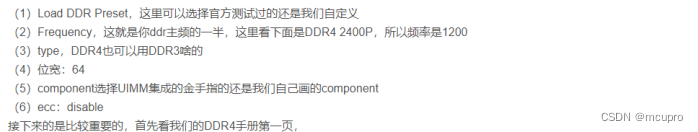

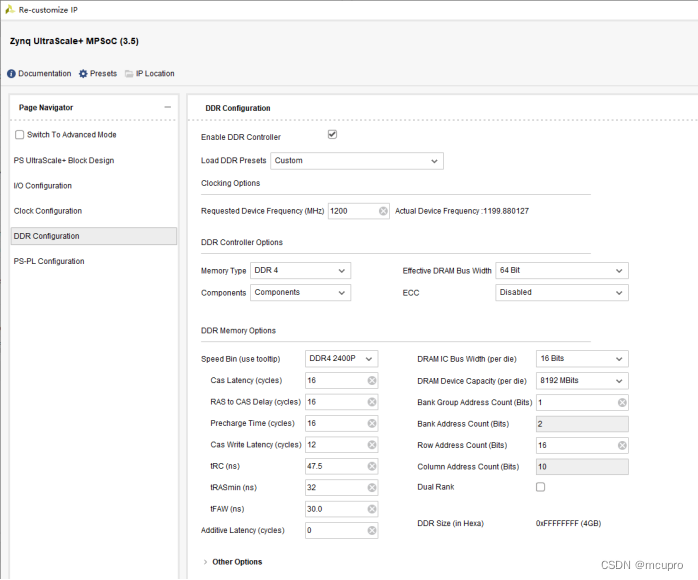

5,DDR4的配置

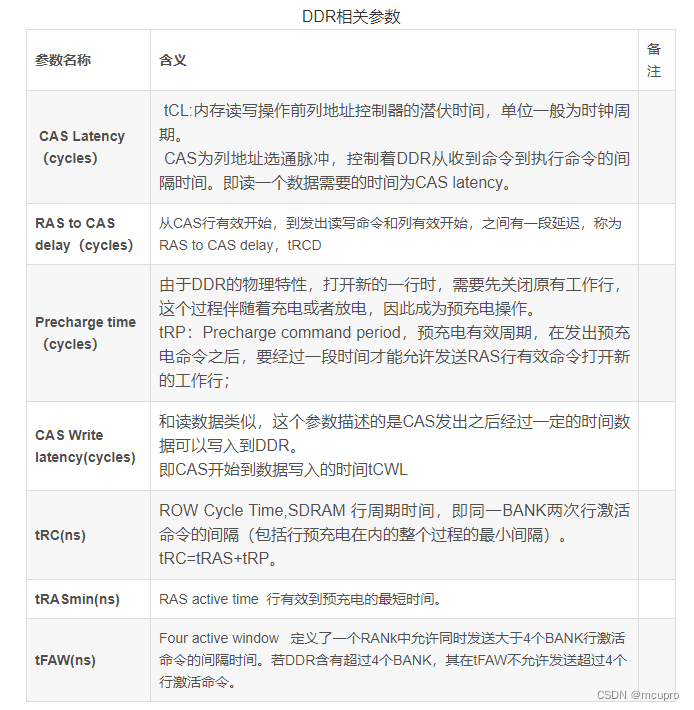

本开发板采用4片8Gbit的DDR4颗粒,具体型号如上图所示.

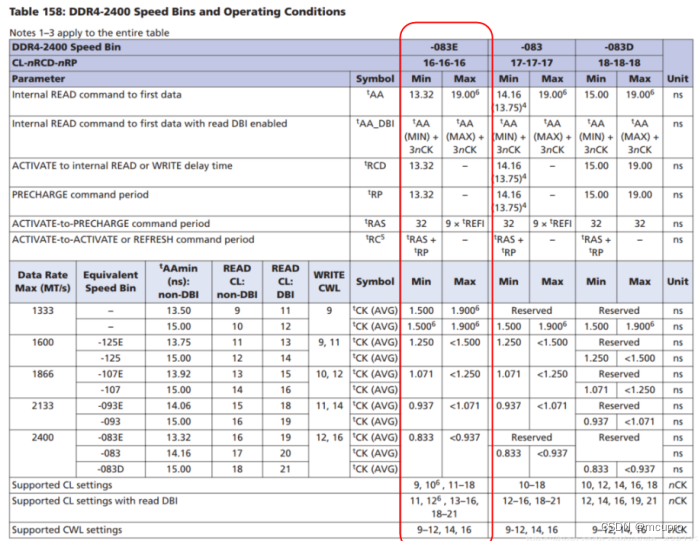

我们按照2400的频率来配置; 也就是-083E的时序来,因为我们设定DDR4跑到2400M的频率.

(1)三个关键时间:16 16 16,直接写入Cas Lateny和RAs to Cas delay以及Precharge time

(2)位宽看你选择的是512x16还是1Gx8,这里我们选择是前者,所以16

(3)容量8Gb

(4)bank Group Count:看手册,只有一个BG0,所以是1

(5)BanK address count:BA[1:0]两位,所以是2

(6)Row addr count:这里是A[15:0],所以16

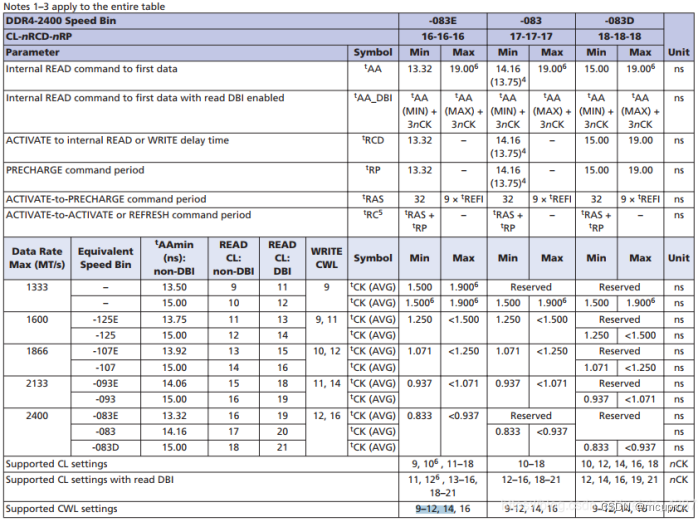

下面是几个比较重要的时间,然后其实都是在手册里面,然后还是先找到对应的83E,然后找到你要的时间

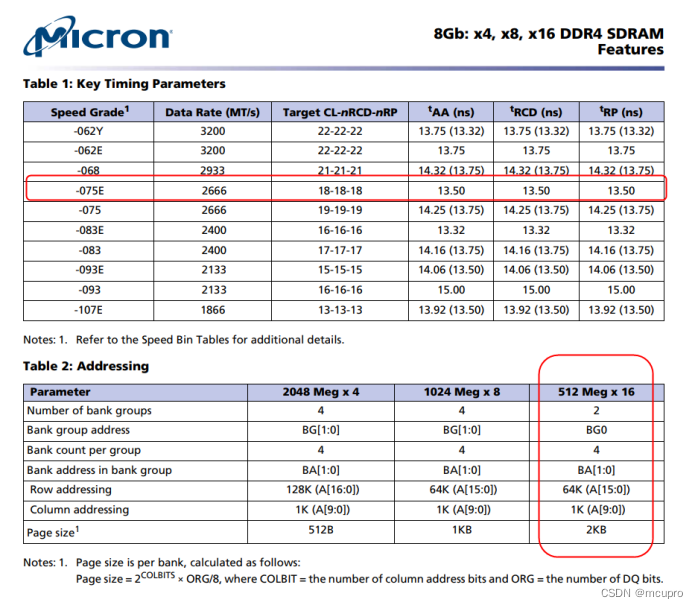

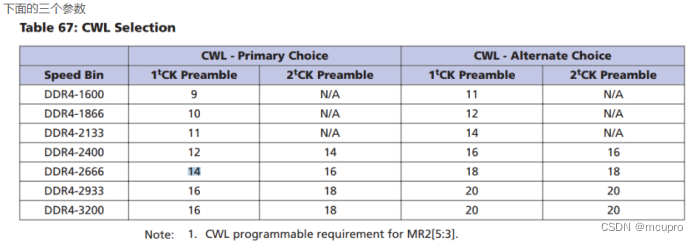

(0)Cas Wirte xx: 这里是设置的12就可以,从上图看出DDR2400,这里要看他支持那些,这里选择常用的12

(1)tRC:手册说了是tRAS+tRP所以是32+23.32=45.32

(2)tRAS:32

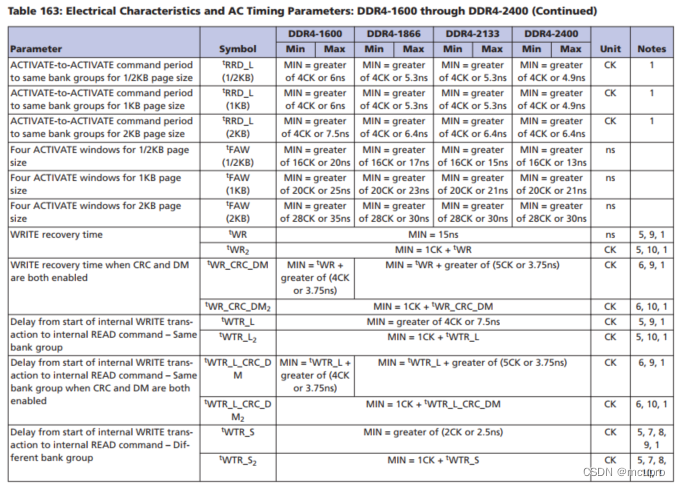

(3)tFAW:下图30ns

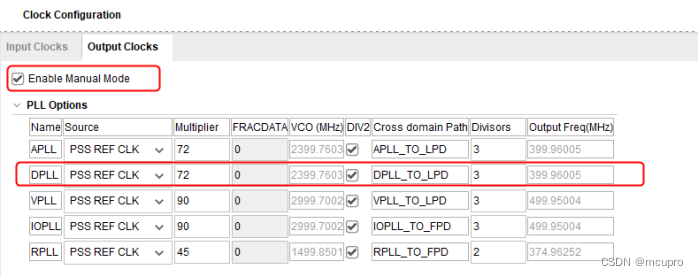

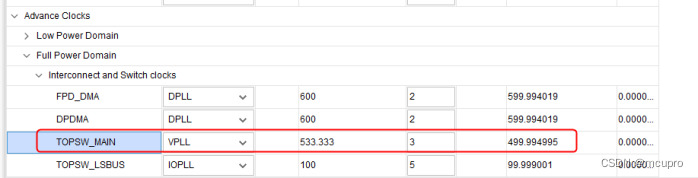

,6,注意要修改PLL

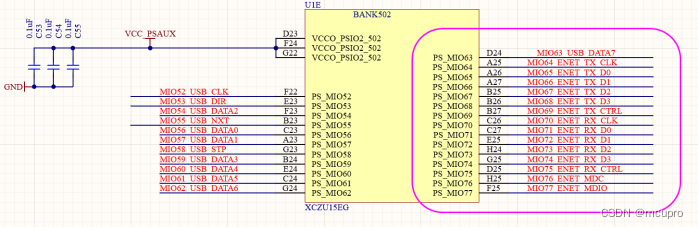

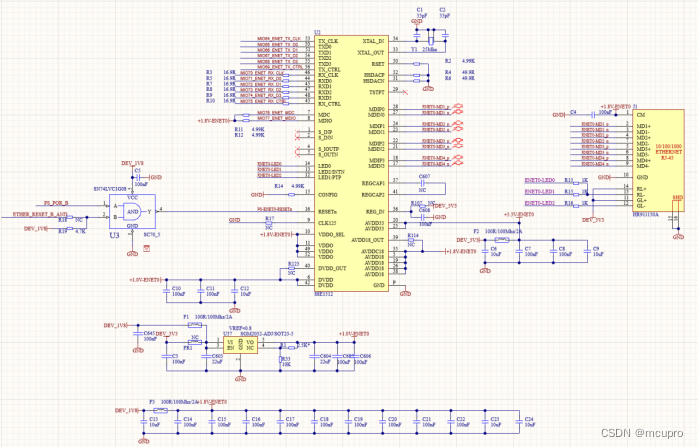

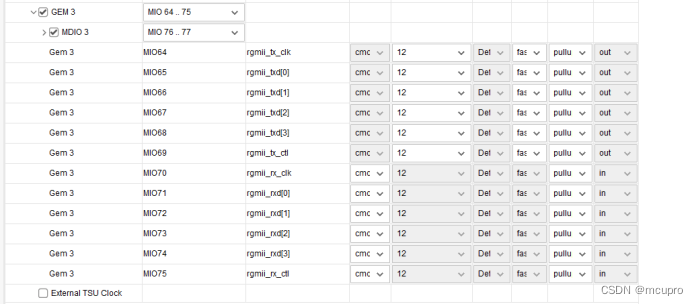

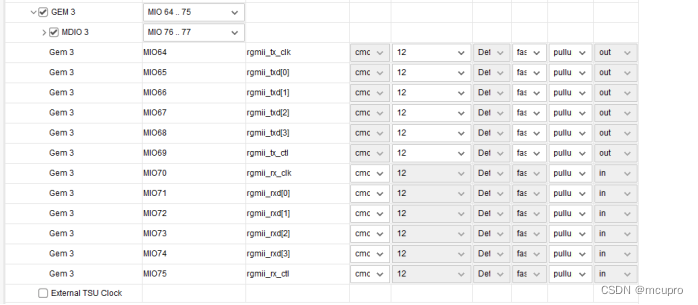

7,PS端以太网的配置

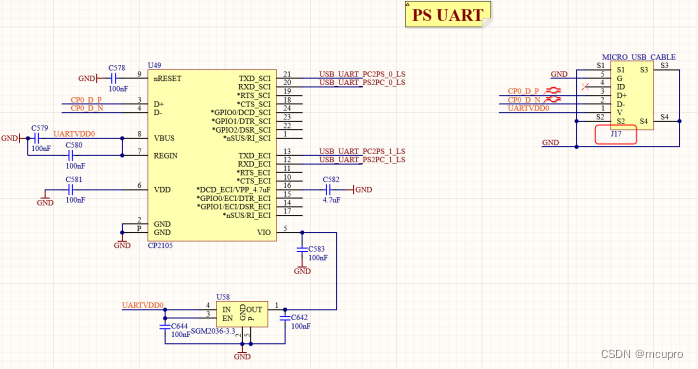

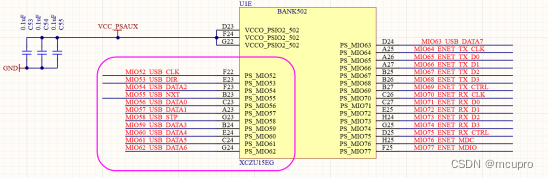

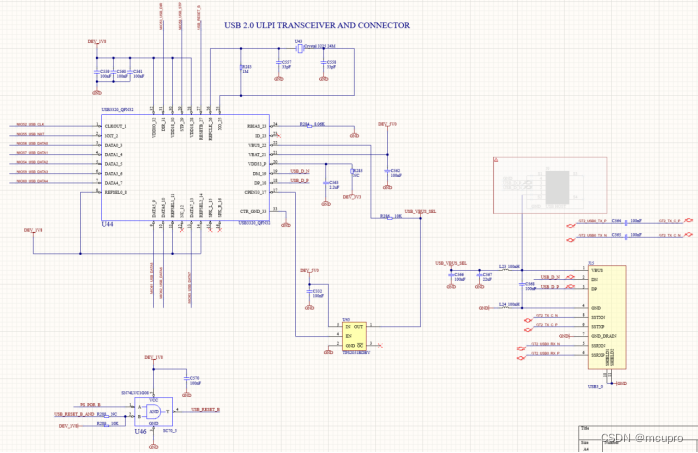

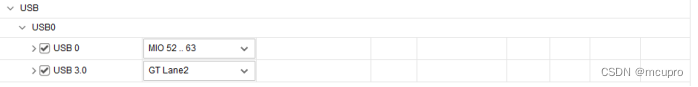

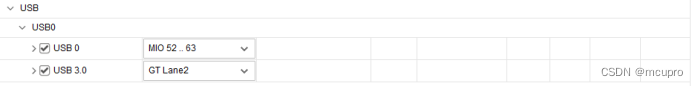

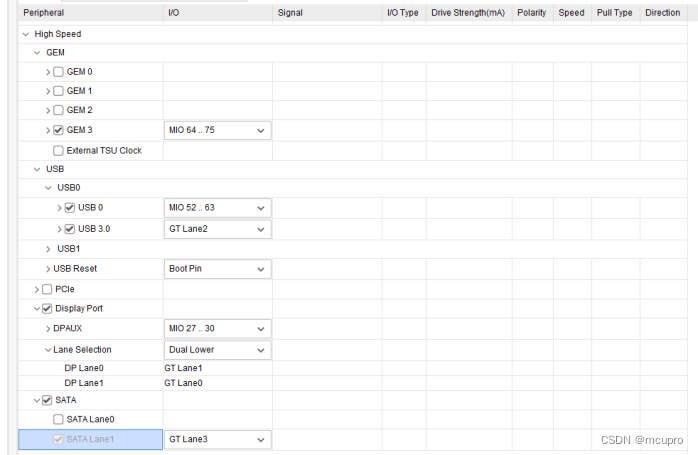

8,USB接口的配置

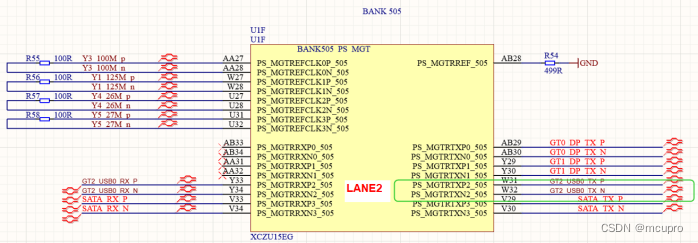

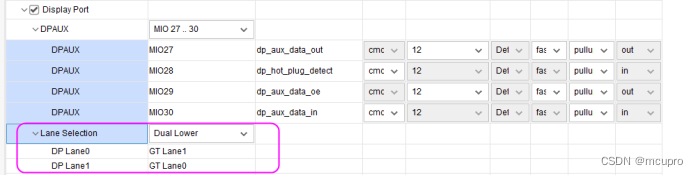

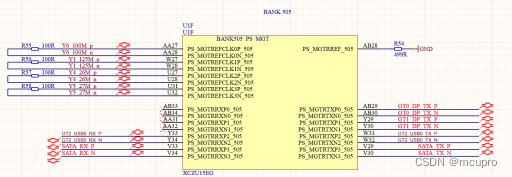

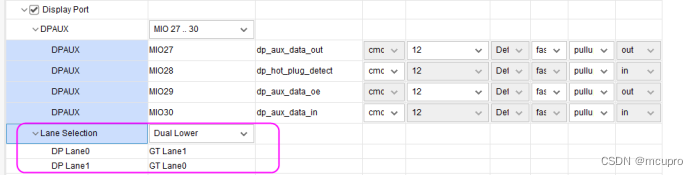

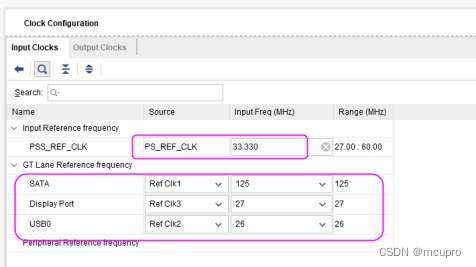

9,可以看到, PS端的收发器

LANE0/1 : DP显示器

LANE2 : USB接口

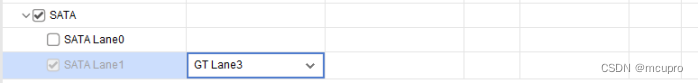

LANE3 : SATA接口

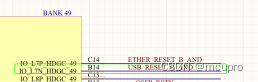

Usb复位先disable掉

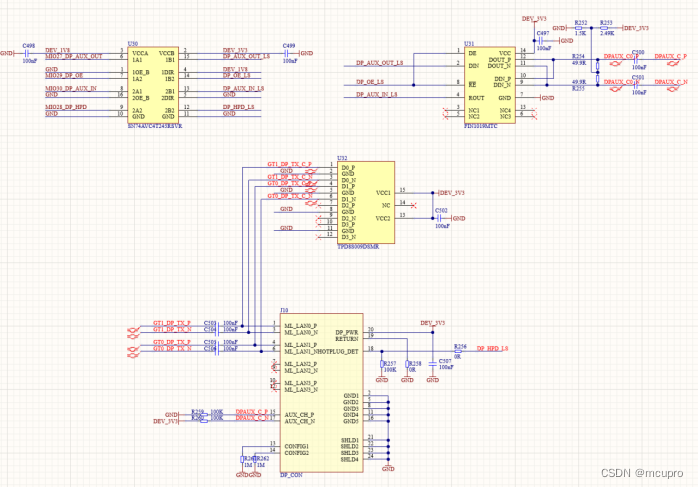

10,DP接口的配置

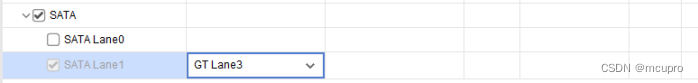

11,Sata接口的配置

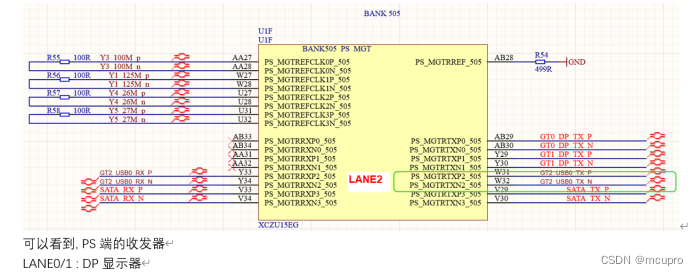

12,可以看到, PS端的收发器

LANE0/1 : DP显示器

LANE2 : USB接口

LANE3 : SATA接口

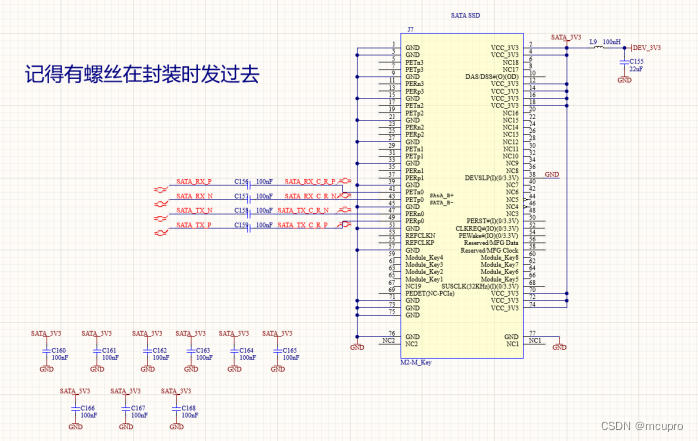

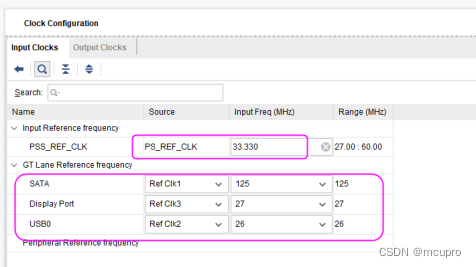

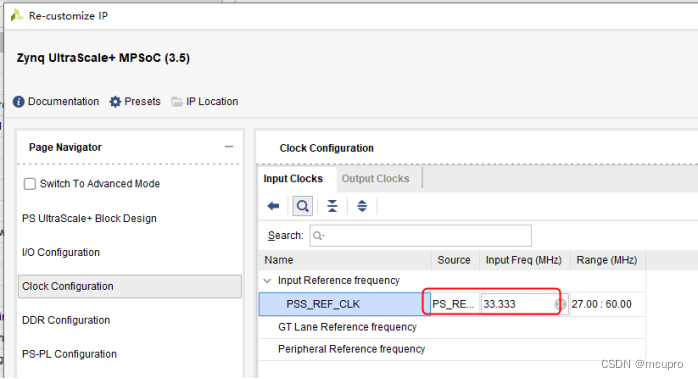

13,Ps端的时钟配置

和原理图一一对应;

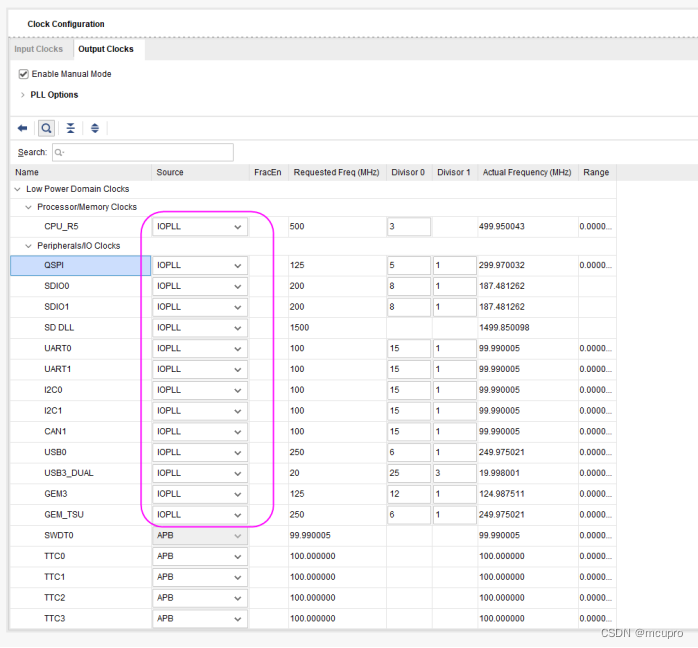

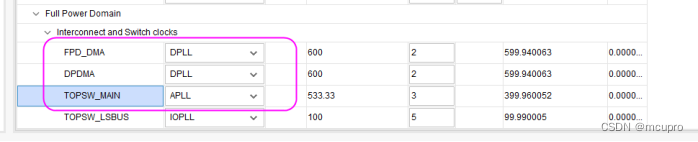

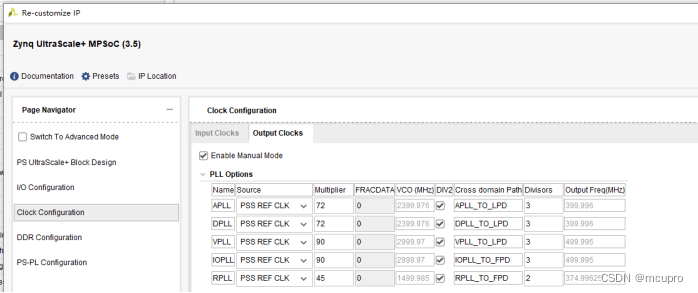

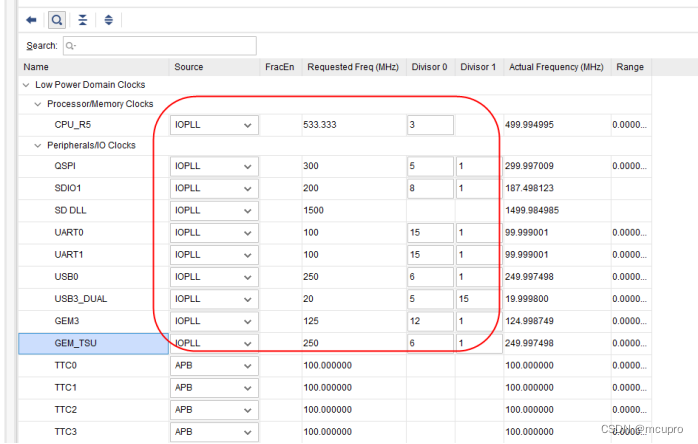

在 Output Clocks 窗口,如果不是 IOPLL,改成 IOPLL,保持一致,用同样的 PLL

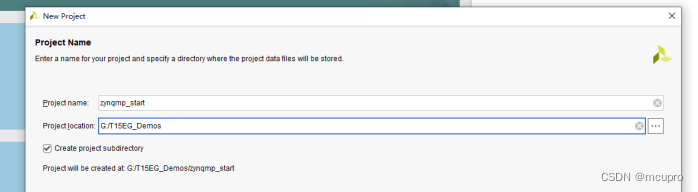

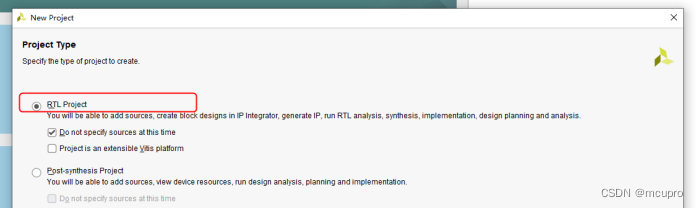

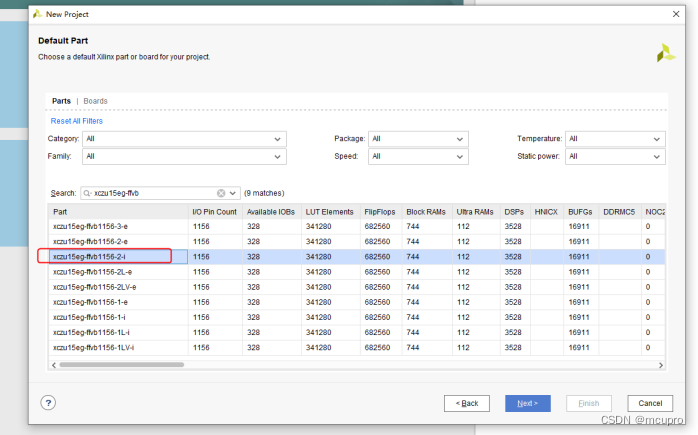

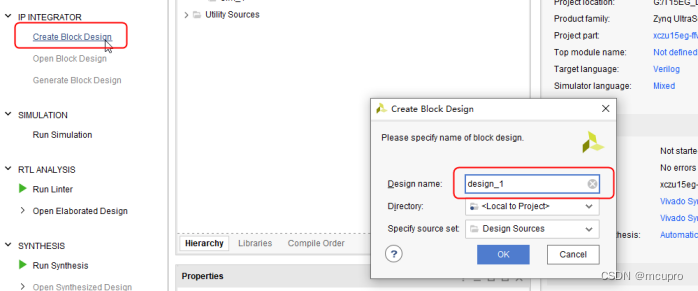

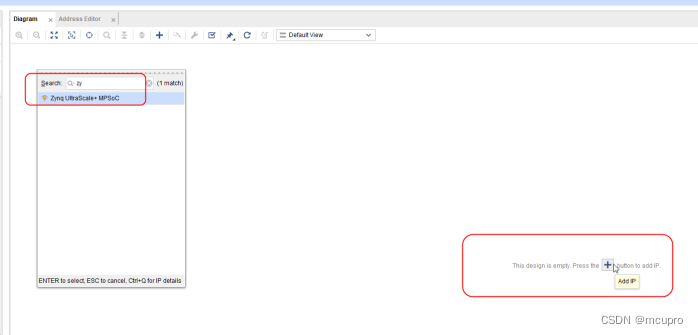

14,创建新的模板工程

选择对应的型号

添加zynq MPSOC 硬核,双击打开配置zynq

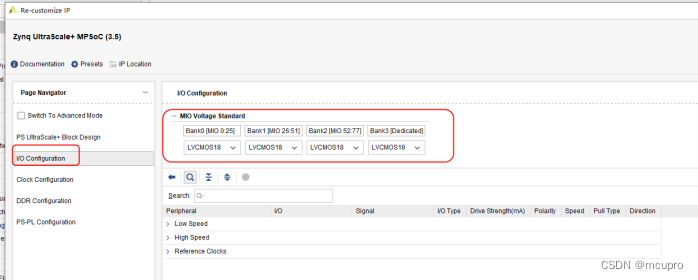

第一步先配置PS的bank的电平标准

根据硬件手册,我们都配置为1.8V的IO电平

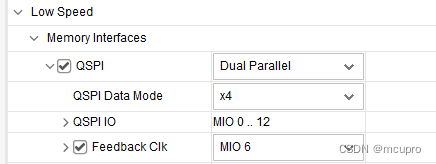

第二步,配置QSPI存储系统

开发板采用2片MT25QU256 拼接成8bit的QSPI存储系统。采用1.8V供电.

第三步,配置SD卡

勾选SD卡,配置如下

第四步,配置PS端的2个串口

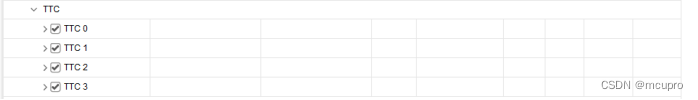

第五步,开启MPSOC的定时器

第六步,配置PS端的高速外设以太网,usb,dp,sata接口

以太网的配置如下

USB的配置如下

Usb复位先disable掉

DP的显示配置如下

Sata的配置如下

第七步,配置时钟系统

Zynq系统PS用33.333M时钟输入, 99%的zynq开发板都是这个频率

配置PS端的高速接口的时钟,和实际的原理图一致

接下来配置输出时钟为如下, 勾选手动模式,配置如下

第五步,配置PS的DDR4内存系统