热门标签

热门文章

- 1项目经理所应具备的八项素质:_项目经理基本安全素养八个必须

- 2传统行业的it程序员_传统行业 程序员

- 3最长子字符串的长度(一)【华为OD机试JAVA&Python&C++&JS题解】_华为od机试 - 最长子字符串的长度(一)(java & js & python & c & c++

- 4数据挖掘算法与现实生活中的应用案例

- 5【一次性看懂fastqc和multiqc的运行代码】输出成功的结果判定、常见报错大赏_multiqc报错了如何解决

- 600 【哈工大_操作系统】Bochs 汇编级调试方法及指令

- 7在mac上安装好python开发环境(pyenv、pyenv-virtualenv、docker-desktop、mysql5.7),一文解决环境问题

- 8unity基础(五)地形详解_unity创建地形山草树水房子

- 9Android视频开发进阶-关于视频的那些术语,美团架构师深入讲解Android开发

- 10调用大模型api返回输出结果--LLM

当前位置: article > 正文

(五)vivado 创建时序约束_vivado时序约束

作者:小小林熬夜学编程 | 2024-04-21 20:44:01

赞

踩

vivado时序约束

一、时序约束是什么?

时序约束(Timing Constraints):用来描述设计人员对时序的要求,比如时钟频率,.输入输出的延时等。比如,对时钟频率的约束最简单的理解就是,设计者需要告诉EDA工具设计中所使用的时钟的频率是多少;然后工具才能按照所要求的时钟频率去优化布局布线,使设计能够在要求的时钟频率下正常工作。

二、为什么需要做时序约束?

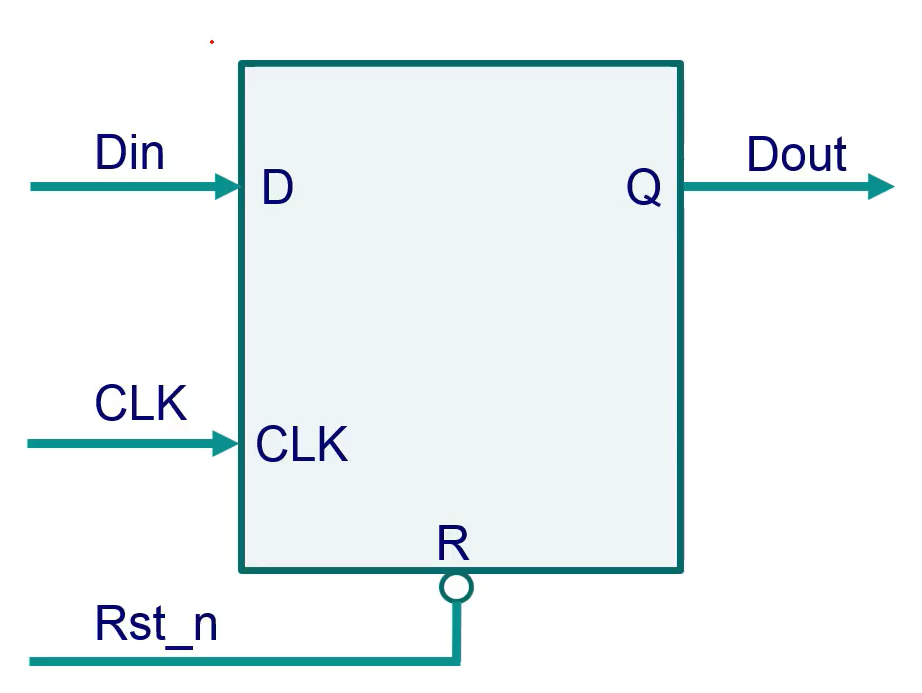

触发器:

建立时间(Tsu:setup time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Th:hold time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th 就是指这个最小的保持时间。

Tco:触发器响应时间,根据不同FPGA 不同工艺决定的。

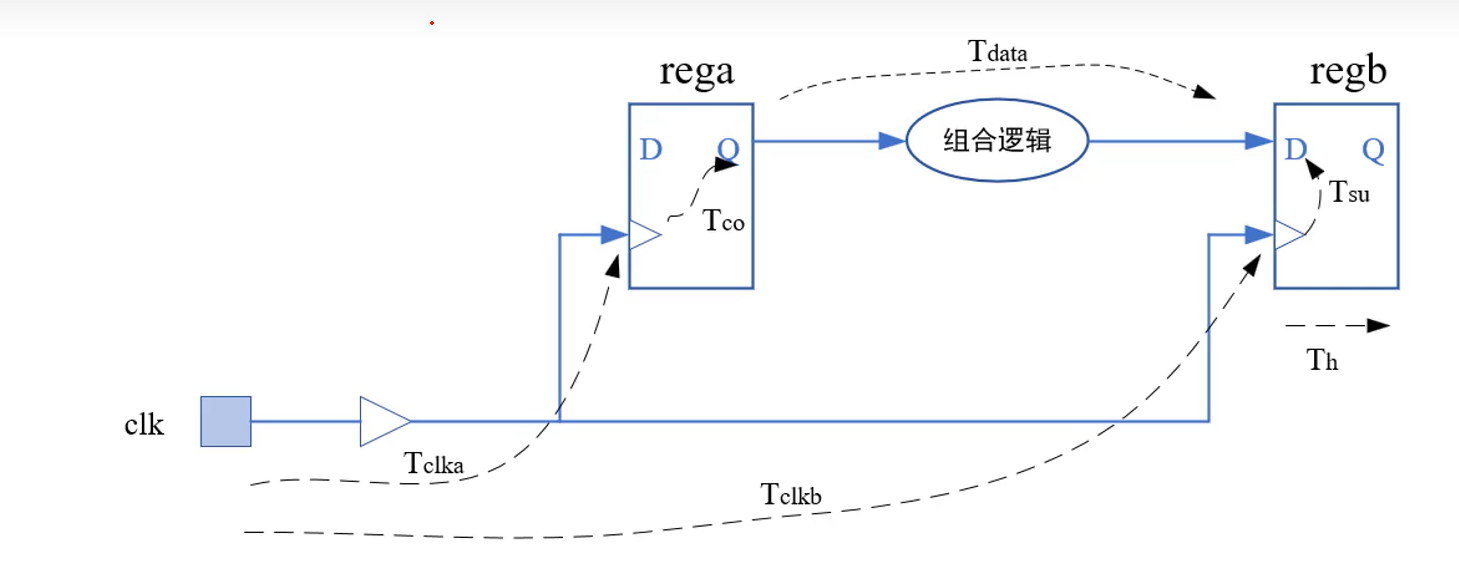

时序模型:

为什么需要做时序约束:通俗的说,就是因为代码写出来的时候,各功能块资源、寄存器资源、布线资源等资源是随机分布的,而布线不同路径导致延时时间不同,这样的话就会导致竞争冒险的出现,因此,为了避免这种情况,必须对fpga资源布局布线进行时序约柬以满足设计要求。

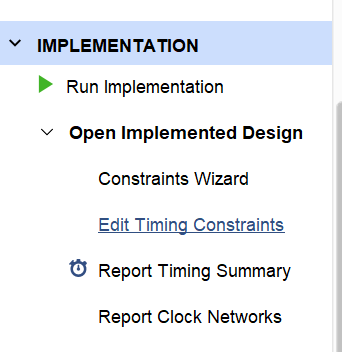

三、创建时序约束

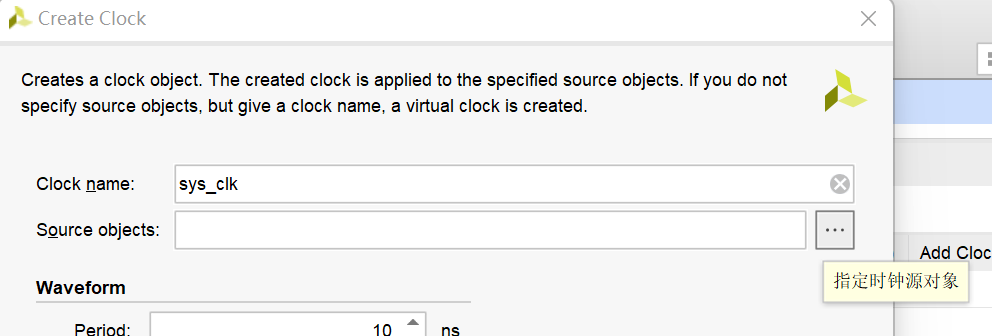

- 打开下图

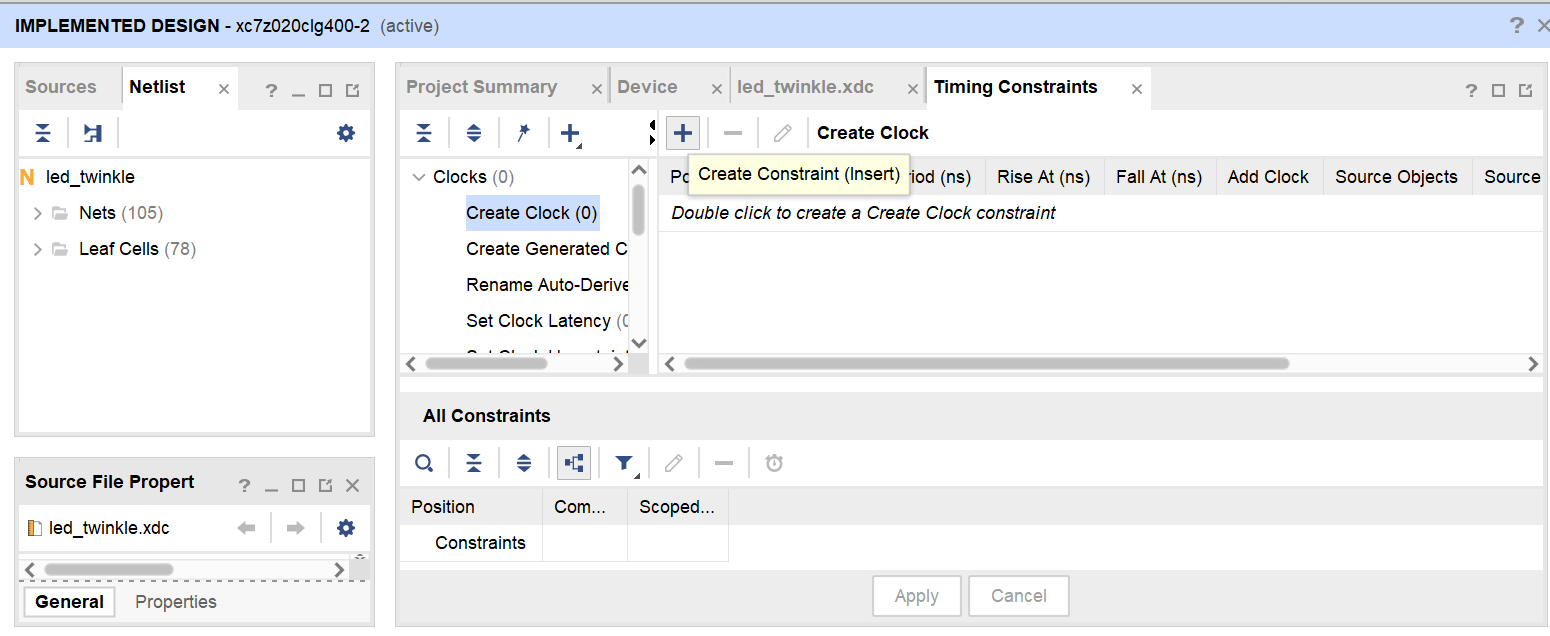

- 点击 编辑时钟约束

- 点击+号 添加一个时钟约束

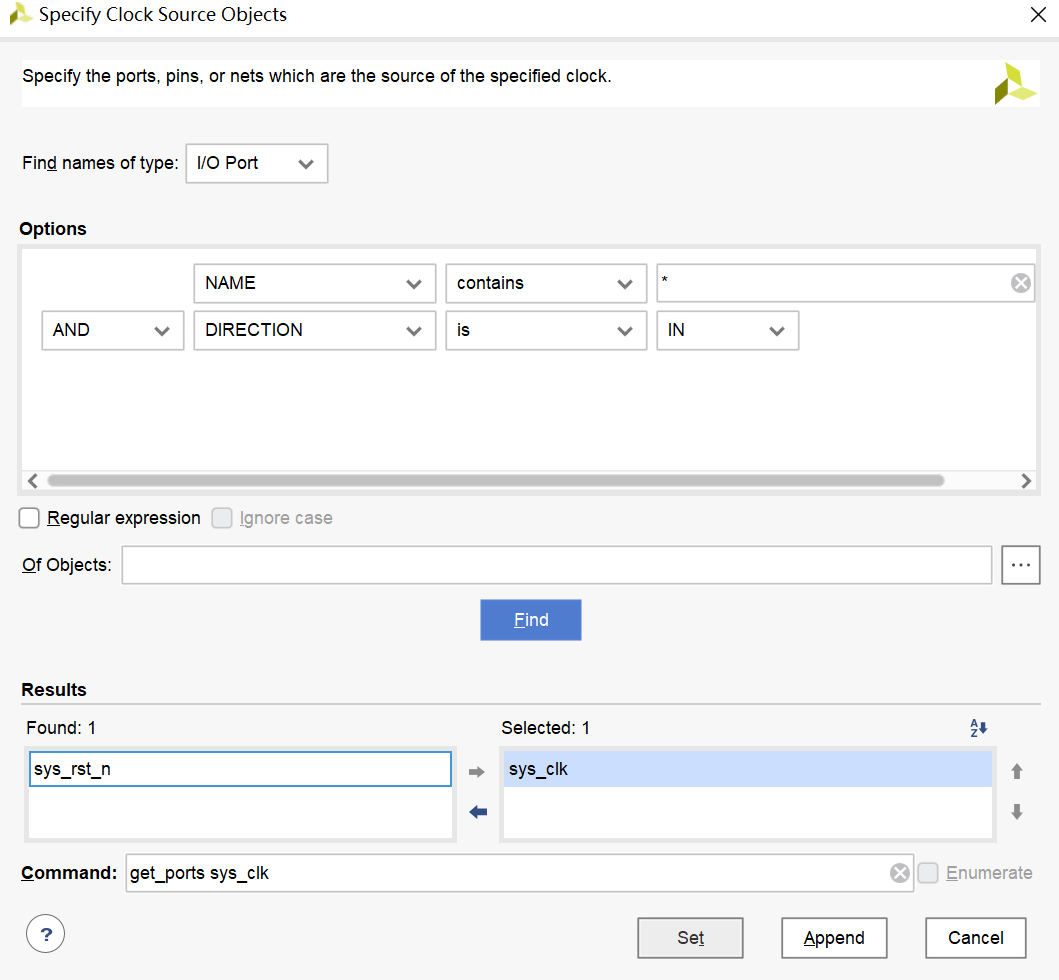

- 点击指定时钟的源 >> 查找find >> 添加所需要的

- 选择I/O端口

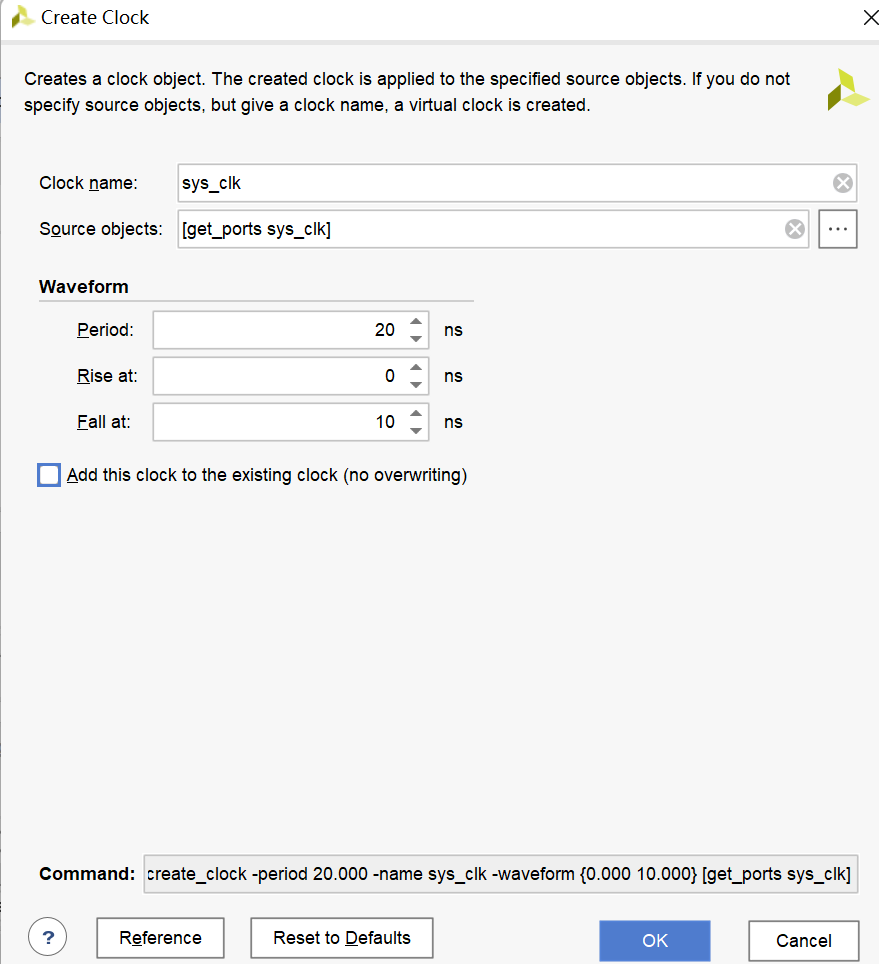

- 选择ok

- 保存后关闭。然后重新生成比特流 可以看到timing如下图所示

- 也可以在xdc文件直接改

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

本文内容由网友自发贡献,转载请注明出处:【wpsshop博客】

推荐阅读

相关标签