热门标签

热门文章

- 1日积一步3(求解点到平面二次曲线的最近距离)_求一条曲线上的点到另一条曲线最近

- 2【STM32笔记】STM32的定时器开发基础(二)(基于STM32CubeMX实现定时器中断)_stm32 tim2

- 3OpenTSDB的设计之道

- 4HIve 在指定位置添加字段_hive 表 新增字段在指定字段后

- 513. django中的cookies和session_django 获取请求头cookie 里的内容

- 6macOS 老版本系统恢复中出现“MacBook Pro无法与恢复服务器取得联系”_未能与恢复服务器取得联系 mac

- 7mysql数据库链接报错error:10060 “Unknown error“_mysql10060错误

- 8AMD优化策略

- 9初探前端世界:网页基本结构入门指南

- 10使用spark mllib训练中文文本分类器的_mlib 中文 处理

当前位置: article > 正文

Actel FPGA——RAM-two port入门操作_actel如何导入mif文件

作者:Monodyee | 2024-04-29 21:10:57

赞

踩

actel如何导入mif文件

软件版本:Libero SOC V11.8;

实验测试目的:只读操作——读取RAM初始化时的数据;

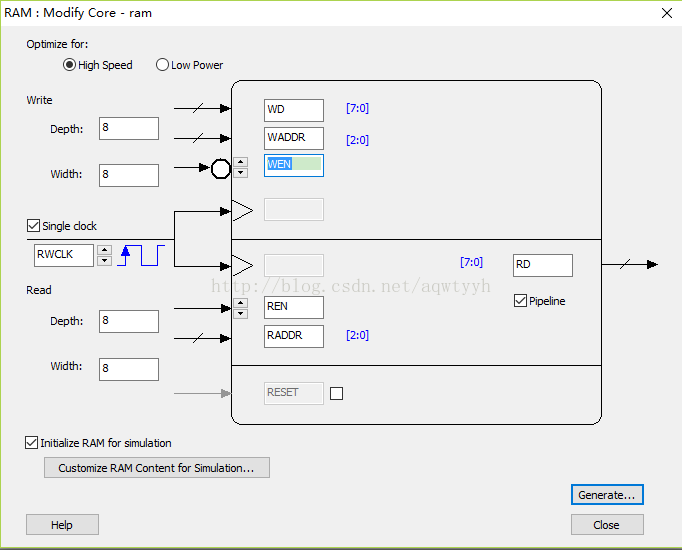

Two port RAM界面如上。

RWCLK:读写共用时钟,也可以选择独立时钟;

REN :读使能,高有效。也可以选择触发极性;

RADDR:读地址,需要自己写Verilog控制;

RD :读数据输出;

虽然只用到读功能,但是写部分的Width和Depth也要写,并且和读部分的Width和Depth相等;

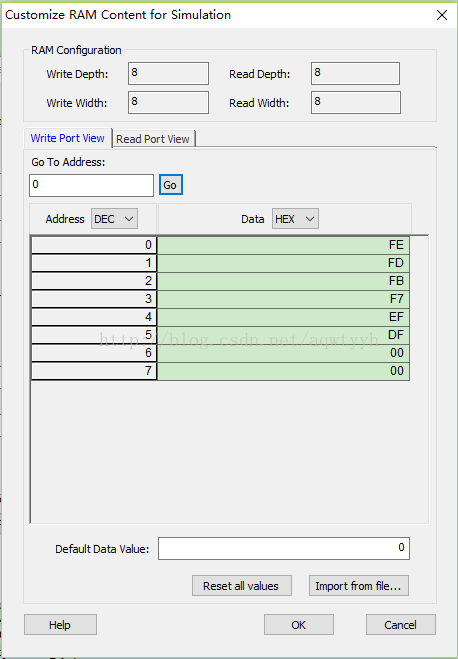

初始化数据在“Customize RAM Content for Simulaion”中写入,支持HEX等文件导入,但不支持.mif文件。

初始化框中的“Write port view”和“Read for view”,在初始化时数据写入任何一个view都行,你会发现当写入read for view时,write port view也会出现一样的数据。

Two port RAM的操作极其简单,一开始我想复杂了。只要给个时钟,给个恒定的REN就行了(除非你不想一直可以读数据,那就不要给REN恒定的高电平),再写一下简单的产生地址RADDR模块就行了。

Tips:1、RAM中不用的脚一定要接地;2、RESET脚只复位输出,并不复位初始化数据;

我的RAM例化代码:

顺便说一下:Actel的Libero SOC中的identify Debug不能实时反映板级调试数据,这一点很不好。

(Identify Debug类似于quartus的Signaltap)

声明:本文内容由网友自发贡献,转载请注明出处:【wpsshop】

推荐阅读

相关标签