热门标签

热门文章

- 1【深度学习】一次性分割一切,比SAM更强,华人团队的通用分割模型SEEM来了

- 2手把手教你如何用python进行数据分析!(附四个案例)_python数据分析案例_python数据分析实战

- 3数据库内核杂谈(一):一小时实现一个基本功能的数据库

- 4Latex模板elsevier爱思唯尔KBS投稿步骤_kbs投稿流程

- 5【FPGA】賽灵思GTH/GTX内核使用---------------------2_gth传误码

- 6埋葬了我曾经的执着与思恋题记不过是所谓的世界末日_cc472.cc

- 7Verilog中reg和wire的区别_verilog reg

- 8一个老程序员的下场_35岁程序员做家教

- 9开源物联网平台Thingsboard安装部署详细教程(适用于windows、linux平台)_thingsboard部署

- 10Hadoop大数据从入门到实战(三)ZooKeeper入门-初体验_第3关:client连接及状态

当前位置: article > 正文

FPGA在校学习记录系列---实验2八线三线编码器并仿真(Verilog HDL)_83线优先编码器仿真

作者:我家小花儿 | 2024-05-24 10:07:12

赞

踩

83线优先编码器仿真

此系列记录FPGA在学校的学习过程。

FPGA系列

需要用到的软硬件:

软件:Quartus II 15.0 (64-bit)

硬件:

5CEBA4F23C7芯片

创建工程在上一个文章

链接:

FPGA在校学习记录系列—新建一个FPGA工程编写程序并仿真(Verilog HDL)

创建工程名:coder8_3

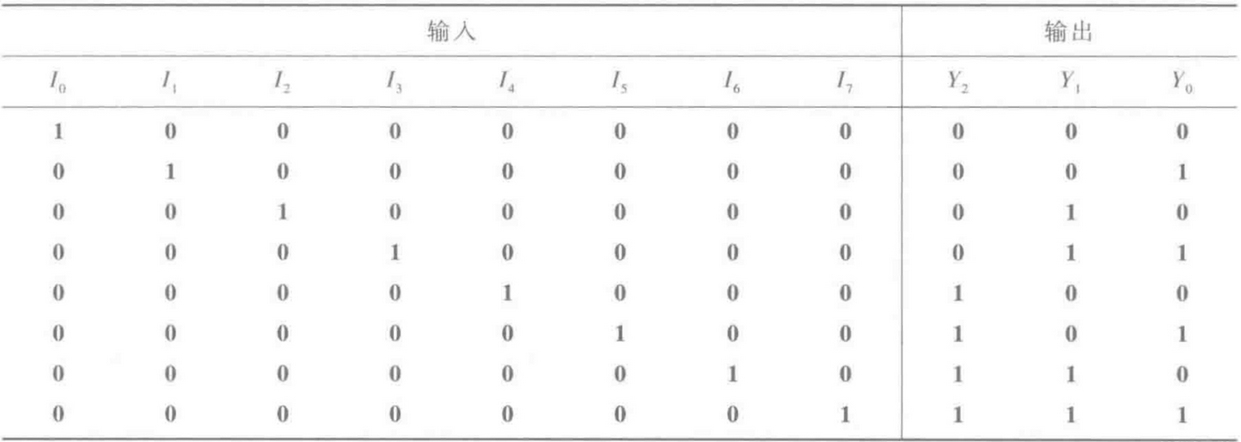

8线3线编码器真值表

打开好创建的工程

在.v文件中添加需要实现的代码

//code8_3.v文件 module coder8_3(a,b); input a; output b; wire [7:0] a; reg [2:0] b; always@(a or b) begin:coder8_3 case (a) 8'b10000000:b=3'b000; 8'b01000000:b=3'b001; 8'b00100000:b=3'b010; 8'b00010000:b=3'b011; 8'b00001000:b=3'b100; 8'b00000100:b=3'b101; 8'b00000010:b=3'b110; 8'b00000001:b=3'b111; endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

根据上面的链接文章步骤生成.vt文件,并在启动项里添加初始值

//code8_3.vt文件(写在启动里面) initial begin // code that executes only once // insert code here --> begin a=8'b10000000; #100 a=8'b01000000; #100 a=8'b00100000; #100 a=8'b00010000; #100 a=8'b00001000; #100 a=8'b00000100; #100 a=8'b00000010; #100 a=8'b00000001; // --> end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

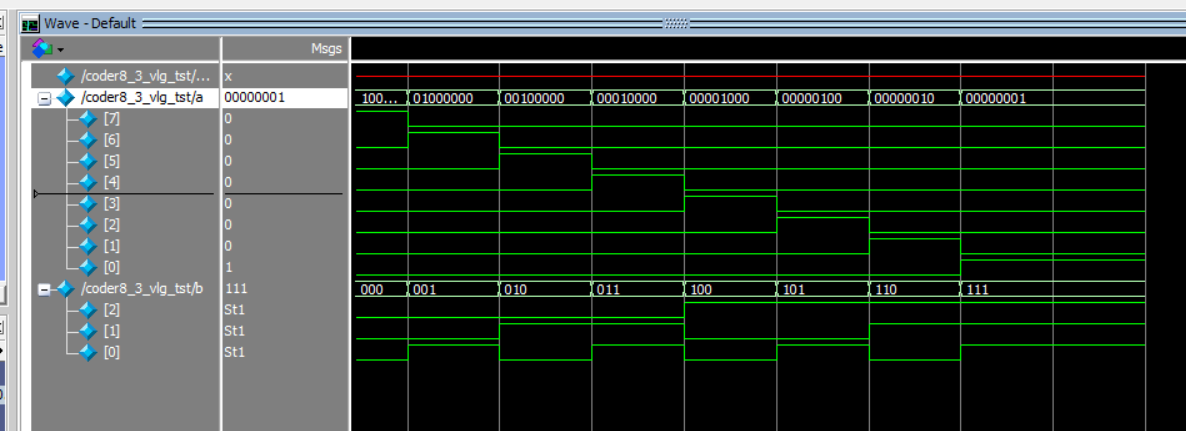

实验仿真结果

(仿真步骤在第一篇文章)

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家小花儿/article/detail/616959

推荐阅读

相关标签