热门标签

热门文章

- 1汽车无人驾驶相应专业词汇_自动驾驶ttc

- 2AndroidStudio Gradle Plugin 下载失败_无法下载aapt2-windows jar(com android.tools.build:aapt

- 3Git 『流程 | 基本命令 | 分支 | 推送与拉取』_git拉取和推送

- 4docker基础知识

- 5AFNetworking实现文件下载

- 6基于7系列V7 690T PCIe的Tandem PROM功能开发测试_tandem pcie

- 7flink中split与select操作_flink split select

- 8Dockerfile构建镜像详解与案例_docker制作镜像经典案例

- 9关于vscode 上安装leetcode:流程+无法登录等问题_为社么vscode安装aws没有登陆选项

- 10java后台实现小程序登录功能_小程序后台扫码登录 java vue3

当前位置: article > 正文

GPU-IO板FPGA(V7)_fpga实现gpu

作者:我家小花儿 | 2024-05-30 07:52:36

赞

踩

fpga实现gpu

主要记录V7中原有模块与架构的更改。

目录

2024.2.23

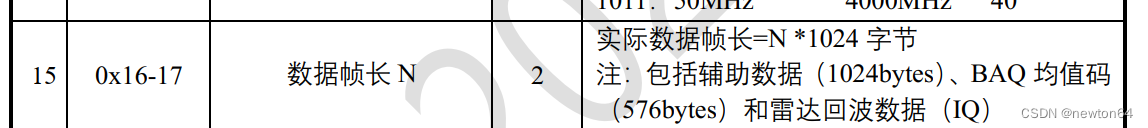

1.包大小如下:

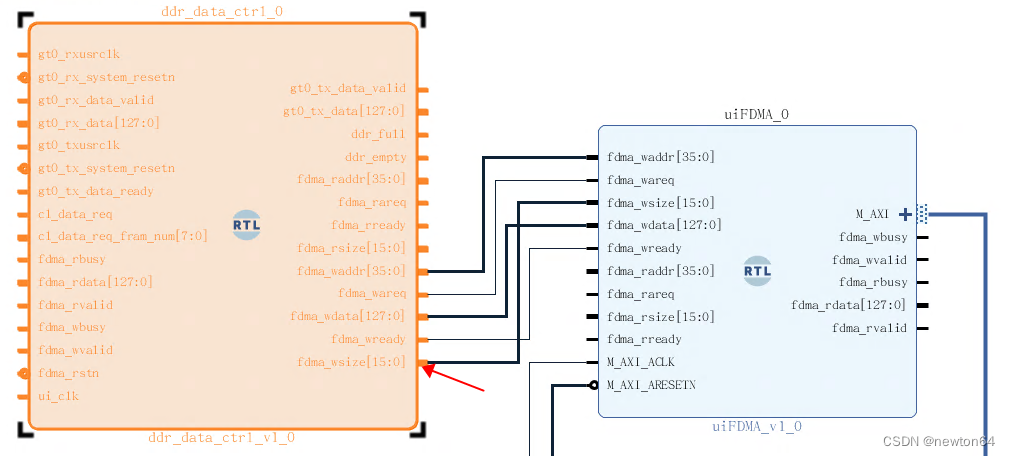

最大65535*1024Byte,当前的FDMA size位宽不够,相应的增加DMA和控制器的wsize/rsize:

2024.2.27

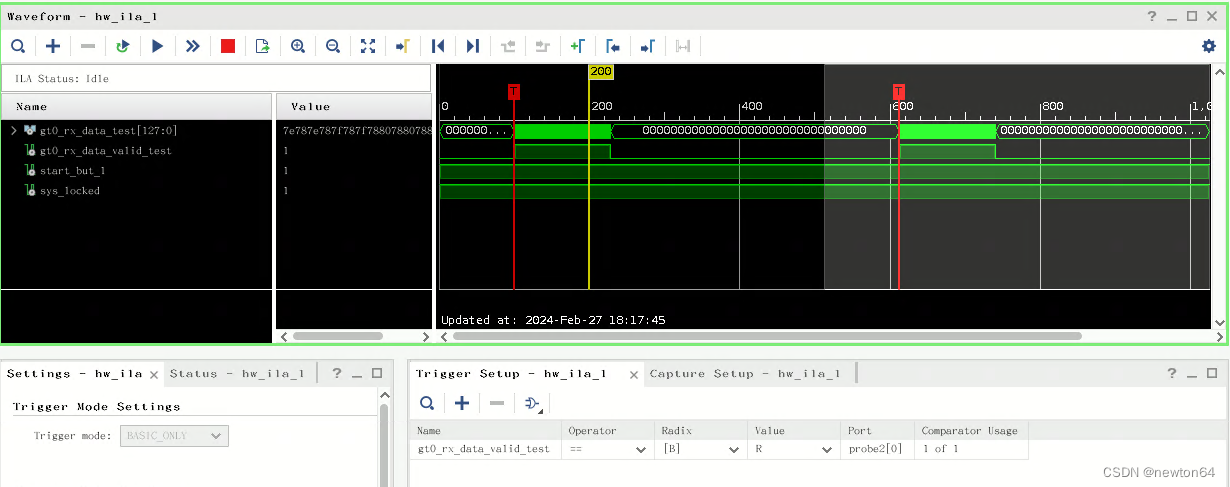

1. 测试环境

测试环境见:gpu_manager模块设计-CSDN博客

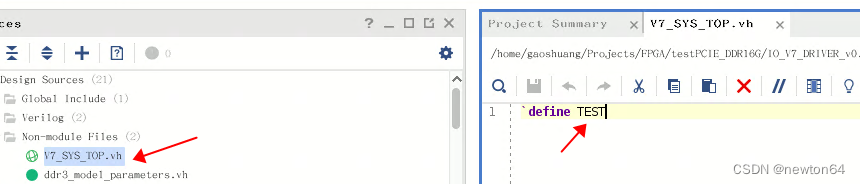

另外为方便测试进行了define:

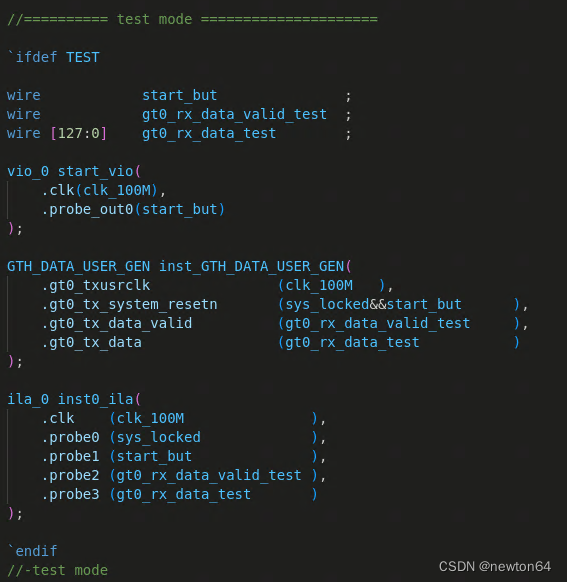

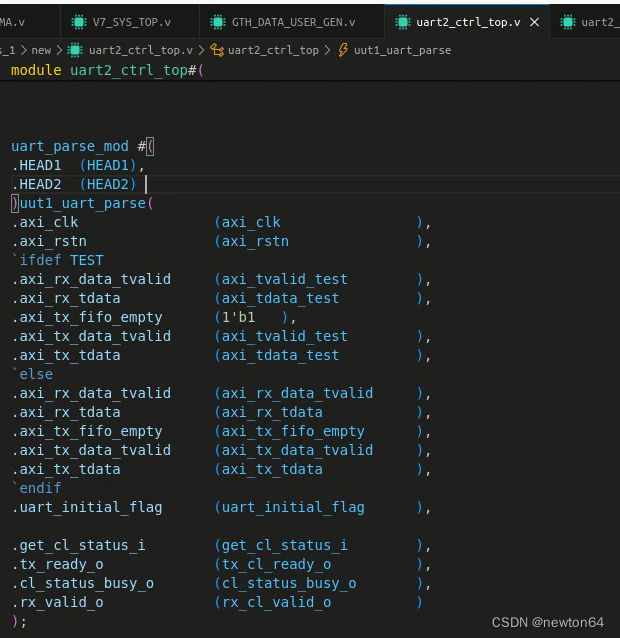

在TEST模式下采用数据发生器代替V5过来的数据:

同时uart环回,代替K7应答:

2.ddr_ctrl调试

工程位置:Y7000P /home/gaoshuang/Projects/FPGA/testPCIE_DDR16G

该模块改变了位宽,起初里面fifo更改位宽没有生效,可能因为是global的需要reset后重新生成。

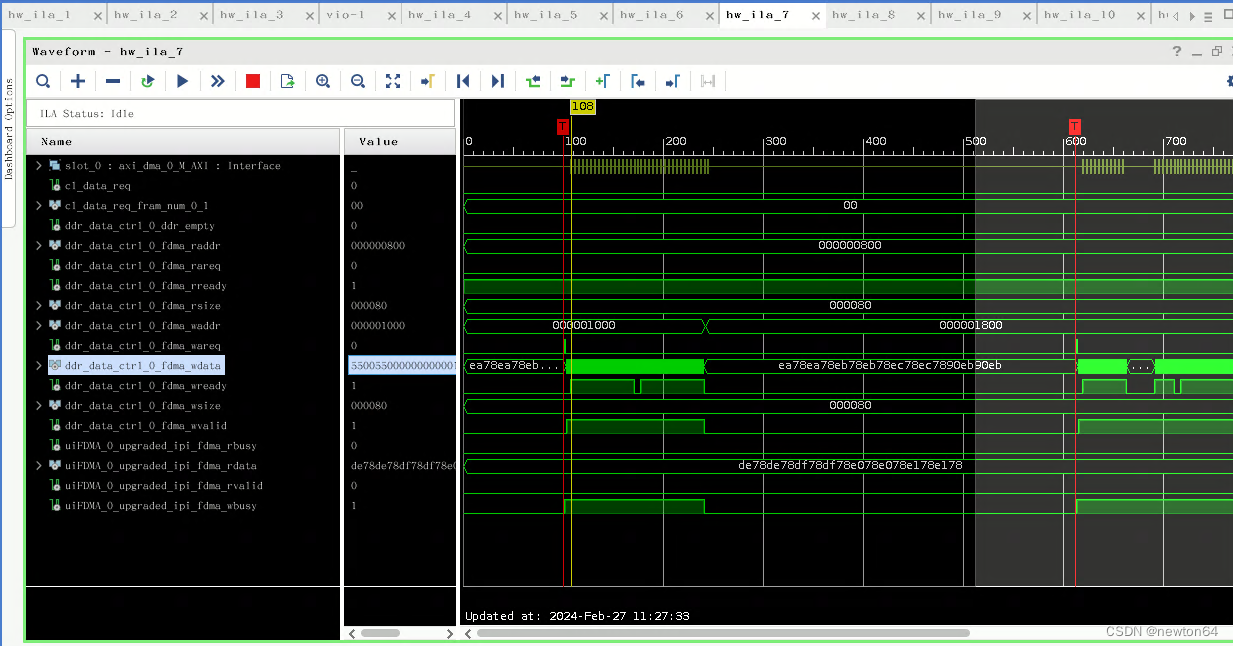

最终,产生wareq后,开始写入DDR:

数据正常:

由于ddr_empty比rcomplete晚3个周期变化,为了当rcomplete产生时根据正确的DDR状态进行下一次数据传输发起,这里做了延迟:

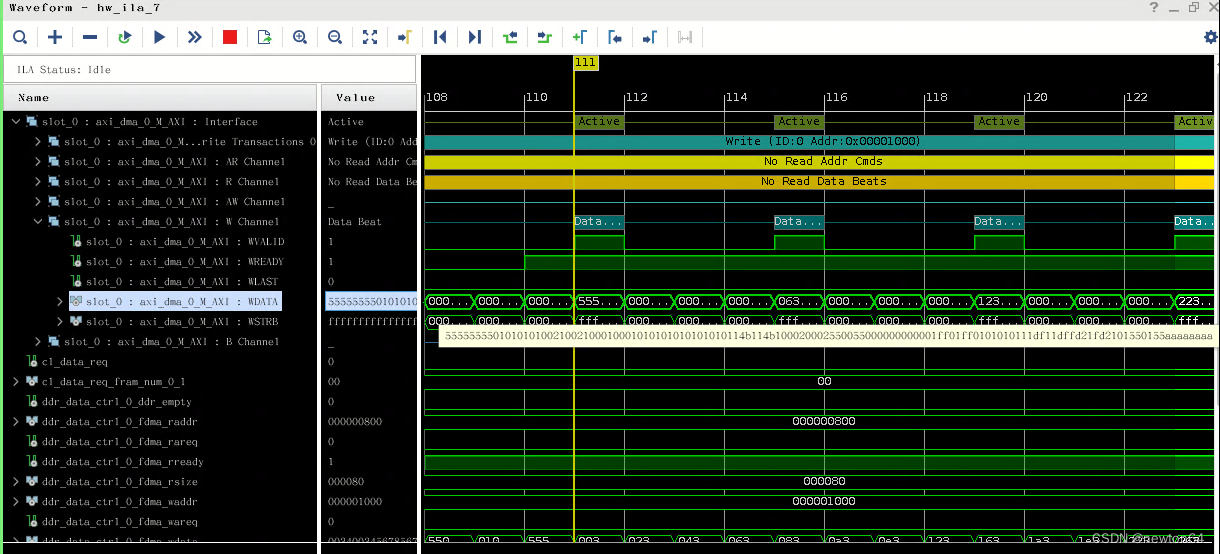

最终数据发生源头产生两笔各2048Byte数据:

之后自动发起了两次传输:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家小花儿/article/detail/645955

推荐阅读

相关标签