- 1语音模块LD3320控制小车运动_ld3320和stm32语音小车

- 2Spark3.x入门到精通-阶段五(SparkStreaming详解原理&java&scala双语实战)_spark3 支持java语法嘛

- 3IO 流超级详细讲解_io流

- 4Hbase建表、删表慢的实例优化_hadoop创建表太慢

- 5【移动端开发】鸿蒙系统开发入门:代码示例与详解

- 6编译原理:短语、直接短语、句柄、素短语、最左素短语案例零基础解析

- 7【极数系列】Flink环境搭建&Docker版本(04)_docker部署flink

- 8MacOS安装反编译工具JD-GUI以及解决无法打开的问题_mac jd-gui

- 9代码的两种命名方法:驼峰命名、匈牙利命名(优缺点)

- 10LLM - 读取 Lora 模型进行文本生成_automodelforcausallm

基于FPGA的数字信号处理(16)--定点数的舍入模式(7)6种舍入模式的总结

赞

踩

前言

在前面的6篇文章中,分别对6中舍入模式做了详细的介绍,本文在前文的基础上,再对这6种舍入模式做一个对比和总结。

6种舍入模式

在数据处理过程中,为了防止数据溢出而增加位宽是一种很常见的处理方式,但是随着算法链的深入,如果任由位宽无限度地增长的话,就是导致使用资源爆炸。所以为了防止这种情况的出现,我们需要对数据的位宽做一定的截位处理,即舍入。

四舍五入就是一种最常见的舍入方式,除次之外,还有以下几种:

-

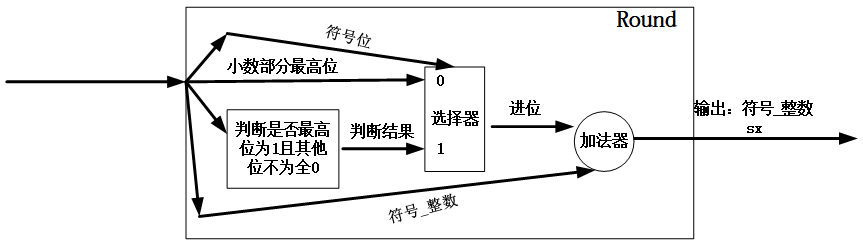

round:即四舍五入,它的舍入方式是舍入到最近的整数,在0.5这类往两边距离都一致的情况时,正数向上取整,而负数则向下取整。例如round(0.5) =1;round(-0.5) =-1

-

nearest:另一种形式的“四舍五入”,与round一样,也是舍入到最近的整数,但在对0.5这类情况时,它是不管正负,都是向上取整,例如nearest(0.5) =1;nearest(-0.5) = 0

-

convergent:另一种形式的“四舍五入”,与round一样,也是舍入到最近的整数,但在对0.5这类情况时,它是不管正负,都舍入到最近的偶数,例如convergent(0.5) =0;convergent(1.5) = 2;convergent(-0.5) =0;convergent(-1.5)=-2 ;

-

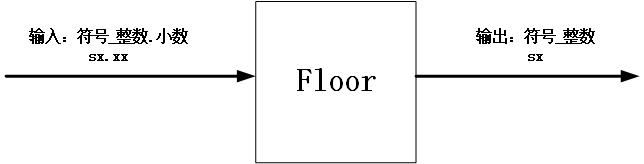

floor:向下取整,即所有数都向着负无穷的方向,就近舍入到最近的整数,例如floor(0.25)=0;floor(1.5)=1;floor(-0.75)= -1;floor(-1.25)= -2;

-

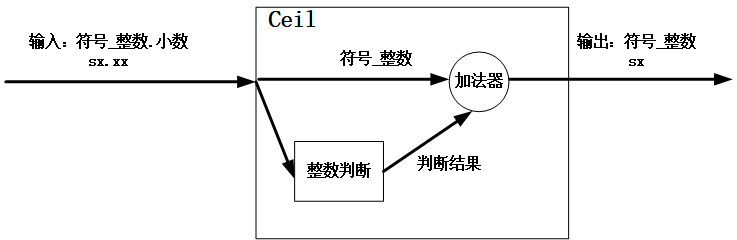

ceil:向上取整,即所有数都向着正无穷的方向,就近舍入到最近的整数,例如ceil(0.25)= 1;ceil(1.5)=2;ceil(-0.75)= 0;ceil(-1.25)= -1;

-

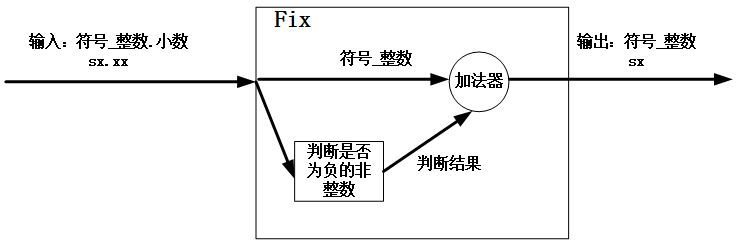

fix:向0取整,所有数都向着0的方向,即正数向着负无穷的方向(floor),负数向着正无穷的方向(ceil),就近舍入到最近的整数。例如fix(0.25)= 0;fix(1.5)=1;fix(-0.75)= 0;fix(-1.25)= -1;

偏置与误差

以上6种模式可以分为2类:

-

round、nearest、convergent:都是舍入到最近的整数,只是对中间数的处理方式不同。

-

floor、ceil、fix:都是向某一个方向取整。

由于舍入方式的不同,所以带来的偏置和误差也不相同:

-

round:都是舍入的最近的整数,所以误差最多只有分辨率的一半。例如舍入到小数点后1bit,那么分辨率为0.5,误差最大的情况就是0.75到1这类情况。因为对于正的中间数而言相当于向上取整,对于负的中间数相当于向下取整。所以当数据是负样本时,由于round的处理,会带来一部分的负偏置;当数据是正样本时,由于round的处理,会带来一部分的正偏置;对于数据分布均匀的正值和负值样本时,则无偏置。

-

nearest:同上,误差最多也只有分辨率的一半。因为中间数都是向上取整,所以不管是正值样本还是负值样本,它都是有正的偏置。

-

convergent:同上,误差最多也只有分辨率的一半。因为中间数是舍入到最近的偶数,相当于一般向上取整,一半向下取整,所以它没有偏置。

-

floor:向下取整,正数相当于舍弃小数位;负数相当于舍弃小数位后再减1。误差最大为接近分辨率的值。例如保留1位小数,x.111111111····11(假设它位宽非常长),向下取整就是x.1,舍弃的部分为0.0111111111····11,这个数是无限接近分辨率的,即0.1(0.5)。向下取整相当于全部添加1个负方向的偏置。

-

ceil:向上取整,正数相当于舍弃小数位+1;负数相当于舍弃小数位。误差最大为接近分辨率的值。例如保留1位小数,x.00000000·····1(假设它位宽非常长),向上取整就是x+0.1,舍弃的部分为x+0.1-x.00000000····1=0.0111111111····11,这个数是无限接近分辨率的,即0.1(0.5)。向上取整相当于全部添加1个正方向的偏置。

-

fix:向0取整。正数相当于向下取整,即舍弃小数位;负数相当于向上取整,也相当于舍弃小数位。误差同上,为一个接近分辨率的值。它的偏置和round的情况恰恰相反,正数是具有负方向的偏置,而负数则是具有正方向的偏置,当样本是在正值和负值之间均匀分别是,它没有偏置。

溢出情况

由于不同舍入模式可以存在进位的情况,所以可能会发生溢出。首先需要说明的,在定点数的舍入中,由于定点数表示的负数范围要比正数的范围大,所以只会产生正方向的溢出而不会产生负方向的溢出。

例如Q4.2格式范围是-2~1.75,存在1.5/1.75舍入到2的情况,因为Q4.2格式无法表示2,所以发生了溢出;而负数方向的舍入最多就是到-2,所以都可以被正确表示,不会发生溢出。

据此可以推断,上述6种舍入模式中,只要存在向上舍入情况的都有可能发生溢出,它们是:

-

round:大于等于一半时会向上舍入,所以可能会发生溢出

-

nearest:同上

-

convergent:同上

-

ceil:自身就是向上取整,所以会有可能发生溢出

剩下的floor和fix它们的正数都是向下取整,所以不会发生溢出现象。

硬件开销

不同的舍入方式对误差的影响是不一样的,有些的误差大,有些的误差小,是不是误差小的舍入方法就一定很好呢?不是,还是要综合考量硬件开销等因素。比如向下取整floor,只需要丢掉小数部分(或者约定的精度外部分)就可以了,这在硬件上就只需要重新连一下线就可以了,逻辑资源的开销就是0。而round这些方式虽然带来的误差小,但是要做的逻辑判断也多,所以硬件资源消耗也高。

floor:只要丢掉小数部分(或者约定的精度外部分),相当于重连线,硬件开销很小(可以说是0开销)

ceil:向上取整,因为丢掉小数部分相当于向下取整,所以向上取整只需要丢掉小数部分,然后加1。特殊情况是整数的情况,此时的向上取整值就是其自身,所以丢掉小数部分后加的不是1而是0。所以硬件开销需要1个加法器来做加法,还需要一个电路来判断是否为整数(即小数部分是否为全0),该电路的输出可以直接用作加法器的一个输入

fix:向0取整,相当于正数floor,负数ceil。因为正数丢掉小数部分相当于向下取整,负数丢掉小数部分是向上取整,所以正数是丢掉小数部分然后加0;负数则是丢掉小数部分然后+1。特殊情况是整数的情况,此时的取整值就是其自身,所以丢掉小数部分后加的不是1而是0。综合起来就是负的非整数是丢掉小数部分然后加1;其他情况则是丢掉小数部分然后加0。所以硬件开销需要1个加法器来做加法,还需要一个电路来判断是否为负的非整数(即小数部分是否为全0以及符号位为1),该电路的输出可以直接用作加法器的一个输入。

round:在前面文章我们分析过了,是一个正数时,相当于舍弃小数部分然后加上小数部分的最高位;是一个负数,且小数部分的最高位为1和其他位不为全0时,相当于舍弃小数部分然后加上1,否则是于舍弃小数部分然后加上0。所以硬件开销是一个判断是否最高位为1和其他位不为全0的电路,一个MUX来选择进位值,一个加法电路实现整数部分加上进位值。

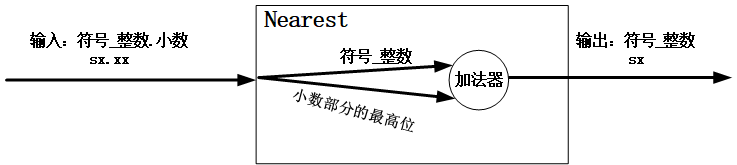

nearest:在前面文章我们分析过了,当小数部分的最高位为0时,相当于整数部分 + 进位值,进位值等于0,即小数部分的最高位;当小数部分的最高位为1时,相当于整数部分 + 进位值,进位值等于1,即小数部分的最高位。综合起来就是,直接用整数部分+小数部分的最高位。所以硬件开销只需要一个加法器。

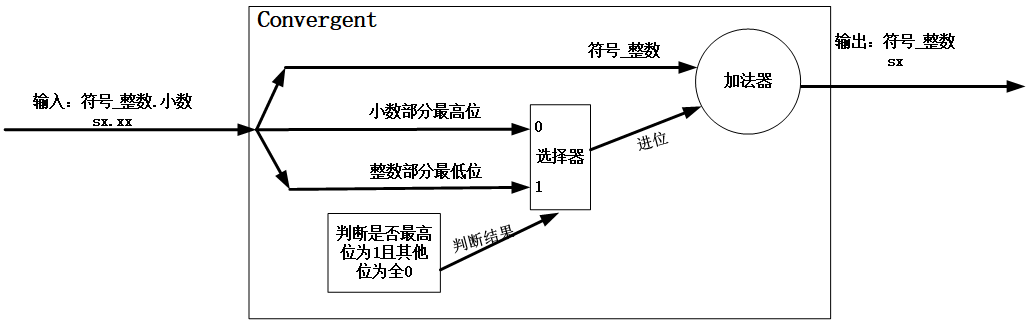

convergent:在前面文章我们分析过了,当小数部分的最高位为1且其他位为全0时,相当于整数部分 + 进位值,进位值等于整数部分的最低位;情况情况相当于整数部分 + 进位值,进位值等于小数部分的最高位。所以硬件开销是一个判断是否最高位为1和其他位为全0的电路,一个MUX来选择进位值,一个加法电路实现整数部分加上进位值。

当然了,以上电路开销仅仅是简单情况下的示意图,随着位宽的增加,不同模式的硬件开销是可能存在区别的,但是大趋势应该不会变。

总结

综合以上舍入模式的方法、偏置、误差、溢出、电路开销等,总结如下: