- 1CTF从入门到提升_ctf实战从入门到提升 pdf

- 2Elasticsearch零基础实战_elasticsearch 指定启动空间

- 3charles的map remote不生效,你的连接不是专用连接 攻击者可能试图从窃取你的信息_你的链接不是专用链接,攻击者试图从baidu

- 4iOS编译时常见报错解决方案_ios pod和代码文件重复报错

- 5【决策状态机FSM(finite state machine)梳理】_有限状态机决策

- 6刷吉米多维奇系列小结(一)

- 7代码随想录C++ Day3 | 203.移除链表元素 707.设计链表 206.反转链表

- 8RabbitMQ和Kafka的比较_kafka与rabbitmq对比

- 92024最新AI大模型产品汇总_当前人工智能产品汇总

- 10用于图像曝光校正的解耦和聚合_lolv1数据集

Zynq7000系列FPGA中的DMA控制器简介(一)_axi dma 控制器

赞

踩

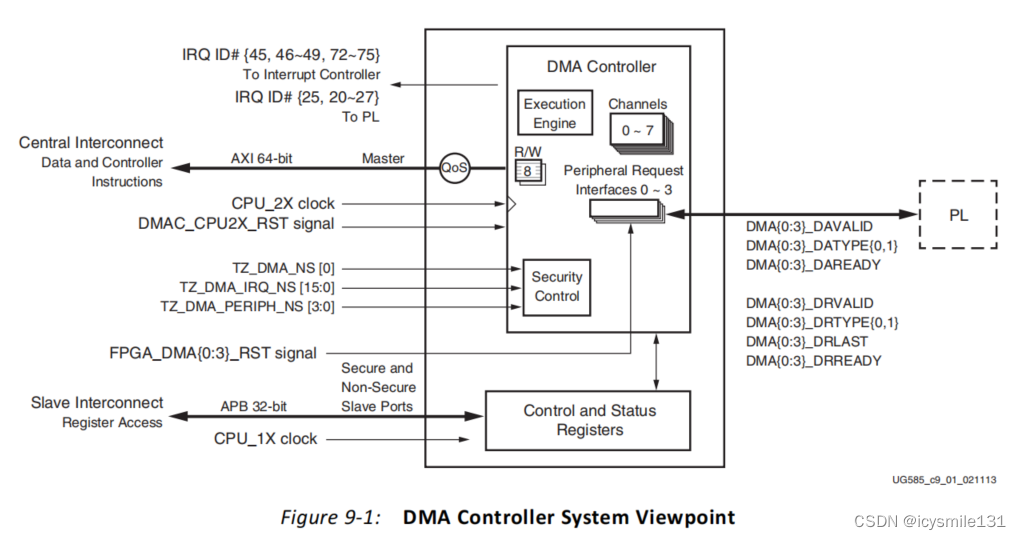

DMA控制器(DMAC)使用64位AXI主接口来执行与系统存储器和PL外围设备之间的DMA数据传输,操作频率同CPU_2x的时钟速率。传输由DMA指令执行引擎控制。DMA引擎运行在一个小指令集上,该指令集提供了一种灵活的指定DMA传输的方法。这种方法提供了比DMA控制器方法的能力更大的灵活性。

DMA引擎的程序代码由软件写入系统存储器的一个区域,该区域由控制器使用其AXI主接口访问。DMA引擎指令集包括用于DMA传输的指令和用于控制系统的管理指令。

控制器最多可配置八个DMA通道。每个通道对应于DMA引擎的处理器上运行的一个线程。当DMA线程执行加载或存储指令时,DMA引擎将内存请求推送到相关的读或写队列。DMA控制器使用这些队列来缓冲AXI读/写事务。控制器包含一个多通道FIFO(MFIFO),用于在DMA传输期间存储数据。

DMA引擎处理器上运行的程序代码将MFIFO视为包含一组用于DMA读写事务的可变深度并行FIFO。程序代码必须管理MFIFO,以便所有DMA FIFO的总深度不超过1024字节的MFIFO。

DMAC能够在没有处理器干预的情况下移动大量数据。源存储器和目标存储器可以位于系统中的任何位置(PS或PL)。DMAC的内存映射包括DDR、OCM、线性寻址Quad SPI读取内存、SMC内存和PL外围设备或连接到M_GP_AXI接口的内存。

用于与PS存储器进行传输的流控制方法使用AXI互连。使用PL外设的访问可以使用AXI流控制或DMAC的PL外设请求接口。没有指向PS I/O外设(IOP)的外设请求接口。对于PL外围AXI事务,在使用中断或状态轮询的编程IO方法中使用在CPU上运行的软件。

控制器有两组控制寄存器和状态寄存器。一组在安全模式下可访问,另一组在非安全模式下可以访问。软件通过控制器的32位APB从接口访问这些寄存器。整个控制器要么以安全模式操作,要么以非安全模式操作;不存在基于信道的模式混合。安全配置更改由slcr寄存器控制,需要重置控制器才能生效。

特征

DMA控制器提供:

- DMA引擎处理器,具有用于DMA传输的灵活指令集:

- 灵活的分散-聚集内存传输

- 完全控制源和目的地的寻址

- 定义AXI事务属性

- 管理字节流

- 八条缓存线,每条缓存线有四个字宽

- 八个并发DMA通道线程

- 允许多个线程并行执行

- 发出最多8个读取和最多8个写入AXI事务的命令

- 对PS中断控制器和PL的八次中断

- DMA引擎程序代码中的八个事件

- 128(64位)字MFIFO,用于缓冲控制器在传输过程中写入或读取的数据

- 安全性

- 用于安全寄存器访问的专用APB从接口

- 整个控制器配置为安全或非安全

- 内存到内存的DMA传输

- 四个PL外设请求接口,用于管理进出PL逻辑的流量控制:每个接口最多可接受四个活动请求

DMA控制器的系统视图如图9-1所示。

方框图

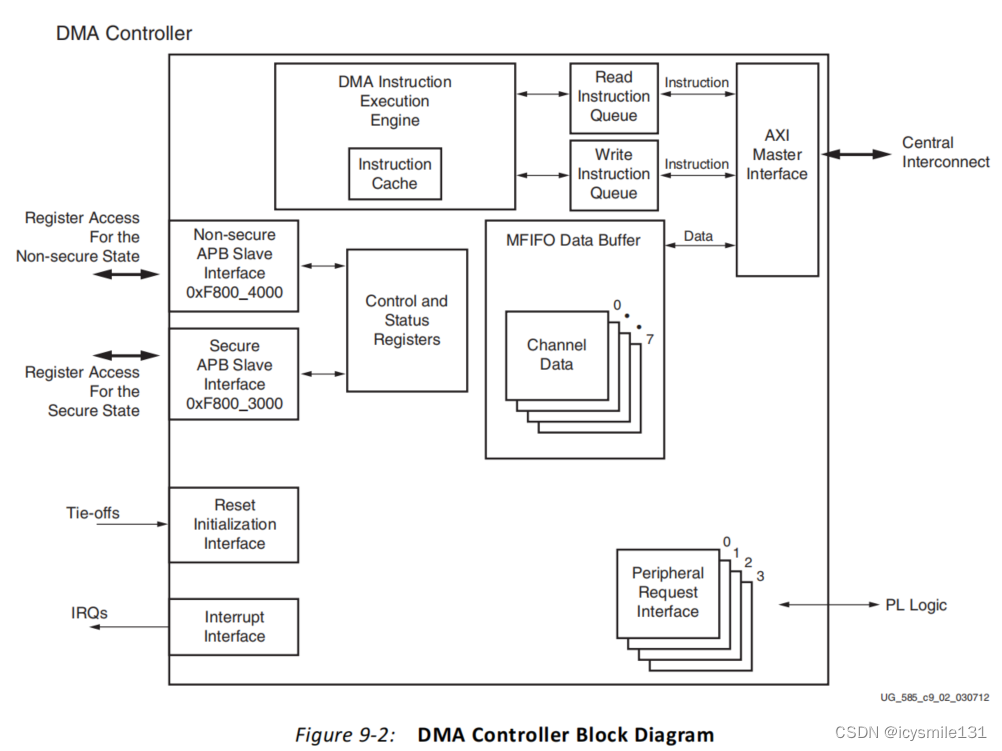

DMA控制器的框图如图9-2所示。

DMA指令执行引擎

DMAC包含一个指令处理块,使其能够处理控制DMA传输的程序代码。DMAC为每个线程维护一个单独的状态机。

- 渠道仲裁

- 为活动DMA通道提供服务的循环方案

- 在为下一个DMA通道提供服务之前,先为DMA管理员提供服务

- 不支持更改仲裁程序

- 渠道优先级

- 以同等优先级响应所有活动(active)DMA通道

- 不支持对DMA通道的优先级进行相对于其他DMA通道的任何更改

指令缓存

处理器内部通常包含一个或多个缓存,用于存储从主存中取出的指令和数据。缓存的目的是为了加速处理器访问这些指令和数据,因为从缓存中读取数据通常比从主存中读取要快得多。当一个线程(在处理器中执行的程序的一部分)请求从一个特定地址读取指令时,缓存首先会尝试查找这个地址是否在其存储的数据中。如果缓存中存在所请求的指令(即缓存命中),那么缓存会立即提供这个指令的数据给处理器,而不需要从主存中读取。这大大减少了处理器的等待时间。如果缓存中没有所请求的指令(即缓存未命中),那么线程会被暂停(stall),直到控制器使用AXI接口从主存中读取该指令并将其放入缓存中。这个过程被称为“缓存行填充(cache line fill)”。如果一条指令的大小超过四个字节,或者它跨越了缓存行的末尾(即这条指令的一部分在一个缓存行中,另一部分在另一个缓存行中),那么处理器需要执行多次缓存访问来获取这条完整的指令。这是因为缓存通常以固定大小的“缓存行”(cache line)为单位来存储数据,这些缓存行的大小通常是固定的,例如64字节或128字节。

当控制器正在通过AXI接口从主存中读取数据以填充缓存行时,它允许其他线程访问缓存。然而,如果在这个过程中另一个线程尝试访问的指令或数据不在缓存中(即发生另一个缓存未命中),那么该线程的指令流水线(pipeline)会被暂停(stall),直到第一个缓存行填充完成。

当指令缓存需要从系统内存中读取指令以填充其缓存行时,这个填充操作的延迟(latency)取决于系统内存的读取延迟。换句话说,如果系统内存(比如DRAM)的读取速度较慢,那么指令缓存填充操作就需要更长的时间。DMAC的性能高度依赖于64位AXI主接口(AXI master interface)的带宽。

读/写指令队列

当通道线程执行加载或存储指令时,控制器将该指令添加到相关的读取队列或写入队列。在AXI互连上发布事务之前,控制器将这些队列用作指令存储缓冲区。

多通道数据FIFO

DMAC使用多通道先进先出(MFIFO)数据缓冲器来存储它在DMA传输期间读取或写入。

用于指令获取和DMA传输的AXI主接口

程序代码存储在系统存储器的一个区域中,控制器使用64位AXI主接口访问该区域。AXI主接口还使DMA能够将数据从源AXI从设备传输到目标AXI从机。

用于寄存器访问的APB从接口

控制器通过32位APB从接口响应下列两个地址范围,这两个地址范围被软件用作读取和写入控制寄存器。

- 非安全寄存器访问

- 安全的寄存器访问

中断接口

中断接口允许硬件事件或软件条件有效地将通知(或称为中断信号)传递给中断控制器(Interrupt Controller)。当这些事件或条件发生时,它们会触发中断,中断控制器随后会暂停当前正在执行的指令(如果处理器正在执行),并跳转到特定的中断处理程序(Interrupt Handler)或中断服务例行程序(Interrupt Service Routine, ISR)以处理该中断。

PL外设DMA请求接口

PL Peripheral DMA Request Interface 通常指的是在可编程逻辑中,用于支持具备DMA能力的外设与DMA控制器之间进行通信的接口。这个接口允许外设在不需要处理器干预的情况下,直接访问系统内存,从而大大提高数据传输的效率。

PL外部设备请求接口支持连接具有DMA功能的外部设备驻留在PL中。每个PL外围请求接口彼此异步,并且与DMA本身异步。

重置初始化接口

用于在设备退出复位状态后,由软件来初始化直接内存访问控制器(Direct Memory Access Controller,简称DMAC)的操作状态的一个接口。当系统启动、重启或经历某个特定的事件导致DMAC需要重置时,这个接口就非常重要。