- 1【深度学习笔记】6_7 门控循环单元(GRU)

- 2LeetCode(Python)—— 二叉树的中序遍历(简单)_python二叉树中序遍历

- 3vision transformer 剪枝论文汇总_vision transformer slimming: multi-dimension searc

- 4Python中的f字符串的用法_python f

- 5索引的数据结构

- 6在ffmpeg中添加编解码器_ffdecoder.lib

- 7【Matlab群体智能算法第二期】基于反向学习的改进粒子群算法(含matlab代码)_改进粒子群算法matlab代码

- 8bat, shell脚本ssh自动输入密码_bat自动输入用户名和密码

- 9单片机和嵌入式设计的区别

- 10大型语言模型的语义搜索(一):关键词搜索_如何查看大模型的关键词

Xilinx IP 应用 -- XADC应用

赞

踩

XADC IP 核 应用

前言

- XADC(全称为Xilinx Analog-to-Digital Converter)是赛灵思公司(Xilinx)推出的一个集成模拟信号采集(ADC)、温度传感器、电压参考等模块的IP核。它可以通过FPGA内部的片上资源来采集外部模拟信号并转换为数字信号,从而方便在FPGA中对这些信号进行处理。同时,XADC还可以测量FPGA芯片的温度,并提供精确稳定的参考电压,方便FPGA设计人员进行精确的模拟电路设计和调试。

- XADC IP 核 可使用DRP 或者 AXI4 Lite 总线控制,为了保证通用性与可扩展性(大部分XILINX IP 都有 AXIL 接口),本设计采用AXIL 接口驱动XADC IP核。

- 本文会介绍两种使用XADC 核 的方法,microblaze驱动与verilog 驱动

- 硬件平台:xc7k325tffg900

- 软件平台:VIVADO 2018.3

- 文中所提文档与工程,在文章最后会提供

IP核配置

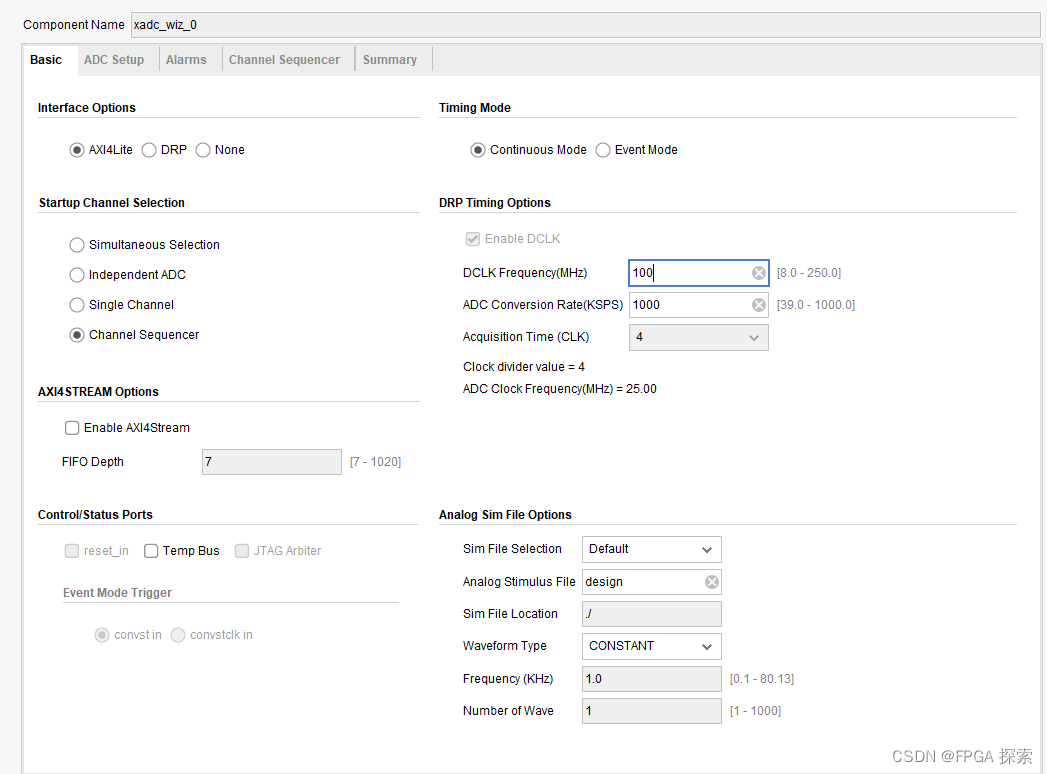

1- Basic 页

Interface:本设计选择AXI4Lite,如果不需要具体温度电压数值,只需要告警信号,则可选择None,不去读取数据

Timing mode:连续采样or事件触发,建议选择连续采样,采样间隔为1us(1000ksps)

Startup:工作模式

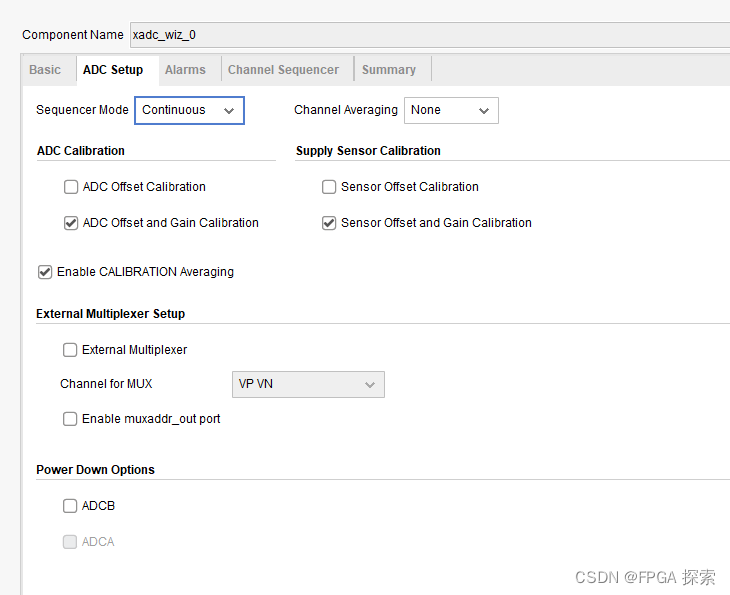

2- ADC Setup

本页默认不操作,默认精度基本足够用

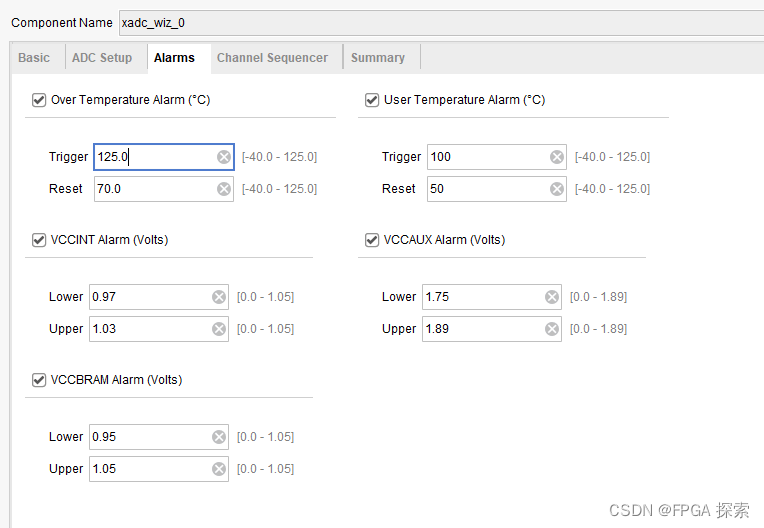

3- Alarms

告警边界设置,对应到输出端口,可以全部勾选上,电压监控默认就行,没有特殊需求不需要更改,超温告警的温度选择芯片工作的最高温度(国内的一些芯片需要咨询厂家);用户设置的告警温度,自己根据需求设置

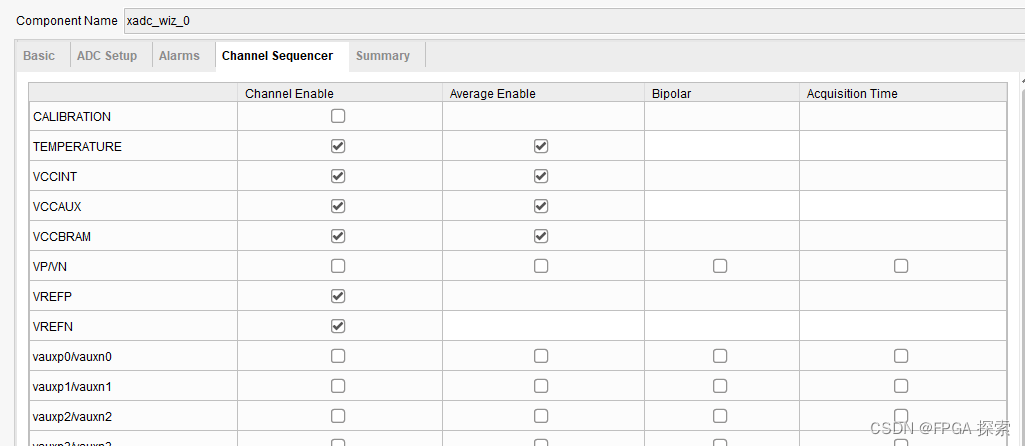

4- Channel

选择了single channel 模式的话,这页配置不了,这页默认只有temperature 通道,且不可更改

选择 channel sequencer 模式的话,可根据实际需求勾选,本设计没有外部传感器,因此只选择了片上温度与电压

注意:这里没有勾选的话,如果需要使用,需要通过配置接口进行使能,否则获取数据为0.

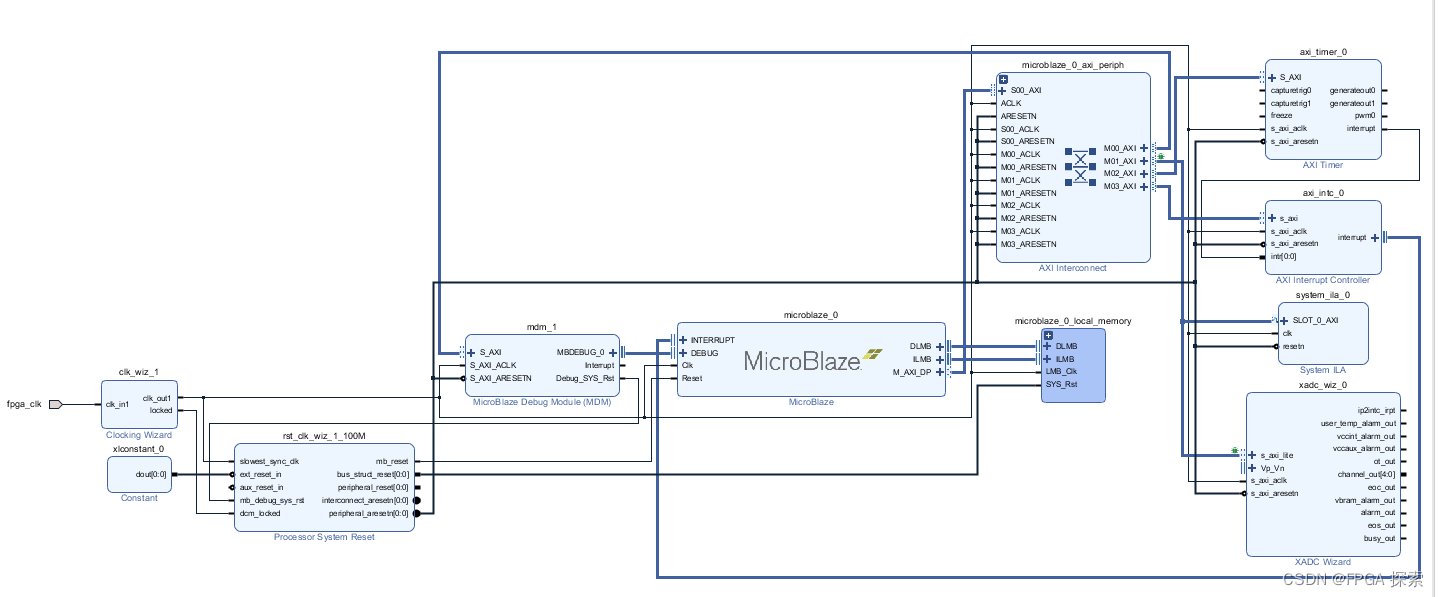

Microblaze 最小系统

Microblaze 系统搭建

主要IP核介绍及应用

clock: MMCM 分频 ,MB主频100M

reset:MB 复位系统控制

mdm:MB 数据管理系统,本设计使用其JTAG UART功能,作为SDK打印输出,实际应用可不使用该功能,开销1个BUFG

microbaze: 软核,实现小型cpu功能

axi timer: 计时器,用于控制系统时间,需要把中断接到终端控制器上

axi intc:中断控制器,用于管理多个中断,单个IP核最多支持32个中断,支持多个IP核级联

interconnect: AXI4 多路仲裁,用于管理多个子设备

XADC:温度/电压监控

SDK 驱动

注意:读取XADC数据前需要等待一段时间,等XADC数据准备好之后再去读,否者读取的数据会出错,或者再读数据之前,判断下XADC的状态,也可以。读取代码如下,代码中的函数都是SDK xadc库自带的。

int SysMonPolledPrintfExample(u16 SysMonDeviceId) { XSysMon_Config *ConfigPtr; u32 TempRawData; float TempData; XSysMon *SysMonInstPtr = &SysMonInst; ConfigPtr = XSysMon_LookupConfig(SysMonDeviceId); if (ConfigPtr == NULL) { return XST_FAILURE; } XSysMon_CfgInitialize(SysMonInstPtr, ConfigPtr, ConfigPtr->BaseAddress); sleep(1); while(1){ TempRawData = XSysMon_GetAdcData(SysMonInstPtr, XSM_CH_TEMP); TempData = XSysMon_RawToTemperature(TempRawData); printf("\r\nThe Current Temperature is %0d.%03d Centigrades.\r\n", (int)(TempData), SysMonFractionToInt(TempData)); sleep(10); }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

XADC 驱动RTL逻辑

需要注意的是:XADC输出的值与实际观测值之间需要转换,转换关系如下。详细内容参见ug480

Temperature Sensor :

Temp = (adc_data * 503.975)/4096-273.15 大约为 adc_data*0.123 - 273.15

Power Supply Senso:

VCCINT,VCCAUX, and VCCBRAM ,On Zynq-7000 SoC devices, the VCCPINT, VCCPAUX, and VCCO_DDR supplies are also monitored

Voltage = adc_data/4096*3 V

- 1

- 2

- 3

- 4

- 5

AXIL 读状态机设计

always@(posedge clk_100m)begin rd_curr_state <= rd_next_state; end always @(*)begin case(rd_curr_state) IDLE:begin if(axil_ctrl_en) rd_next_state = RD_INIT; else rd_next_state = IDLE; end RD_INIT:begin//需要读取的地址在本状态更新 if(rd_done) rd_next_state = RD_DONE; else rd_next_state = RD_ADDR; end RD_ADDR:begin //读地址 if(s_axi_arvalid && s_axi_arready) rd_next_state = RD_DATA; else rd_next_state = RD_ADDR; end RD_DATA:begin if(s_axi_rready && s_axi_rvalid) rd_next_state = RD_INIT; else rd_next_state = RD_DATA; end RD_DONE:begin if(time_cnt[27]) rd_next_state = IDLE; else rd_next_state = RD_DONE; end default: rd_next_state = IDLE; endcase end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

AXIL 读数据

需要注意的是,电压与温度数据是12bit的,在s_axi_rdata 低16bit的高12bit,详细内容看ug480

//*读数据控制 (* MARK_DEBUG="true" *) reg [31:0] alarm_reg = 32'h0; always @(posedge clk_100m)begin if((rd_curr_state == RD_DATA)&(rd_next_state == RD_INIT))begin case(reg_cnt) 4'd0:xadc_status<= s_axi_rdata ; //Status register 4'd1:alarm_reg <= s_axi_rdata ; //Alarm output status register 4'd2:board_tmp <= s_axi_rdata[15:4] ; //Temperature 4'd3:vccint <= s_axi_rdata[15:4] ; //VCCINT 4'd4:vccaux <= s_axi_rdata[15:4] ; //VCCAUX 4'd5:vp_vn <= s_axi_rdata[15:4] ; //Vp/Vn 4'd6:vrefp <= s_axi_rdata[15:4] ; //Vrefp 4'd7:vrefn <= s_axi_rdata[15:4] ; //Vrefn 4'd8:vbram <= s_axi_rdata[15:4] ; //Vbram default :begin xadc_status <= xadc_status; alarm_reg <= alarm_reg ; board_tmp <= board_tmp ; vccint <= vccint ; vccaux <= vccaux ; vp_vn <= vp_vn ; vrefp <= vrefp ; vrefn <= vrefn ; vbram <= vbram ; end endcase end else begin xadc_status <= xadc_status; alarm_reg <= alarm_reg ; board_tmp <= board_tmp ; vccint <= vccint ; vccaux <= vccaux ; vp_vn <= vp_vn ; vrefp <= vrefp ; vrefn <= vrefn ; vbram <= vbram ; end end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

资源

XILINX IP XADC 应用例子工程

补充:[XILINX IP XADC 应用例子工程] https://download.csdn.net/download/reveryql/88136815