- 12022危险化学品经营单位主要负责人考试题库及模拟考试_生产经营运输储存使用危险物品或者处置废弃危险物品的行为可能构成

- 2K-Nearest-Neighbors_k nearest neighbor selects all features all a subs

- 35分钟轻松学Python:4行代码写一个爬虫(附零基础学习资料)_爬虫代码

- 4面试经验:字节跳动面试中的难题_字节常考hard题

- 5ERP&EIRP_eirp和erp区别

- 6驱动程序无法通过使用安全套接字层(SSL)加密与 SQL Server 建 立安全连接。错误-“PKIX path building failed-_sqlserver中ssl加密

- 7SpringBoot中进行简单的密码加密_springboot密码加密

- 8Springboot学习笔记(缓存介绍及缓存在springboot中的应用)_springboot如何使用缓存

- 9Java设计模式——单例模式_java单例模式

- 10百度地图js api 为覆盖物添加索引_百度地图覆盖物属性ja

基于FPGA的串口通讯设计_基于fpga的串口通信设计

赞

踩

这个小项目是在2013年初学FPGA时所做的,现把当时的设计笔记贴出来。

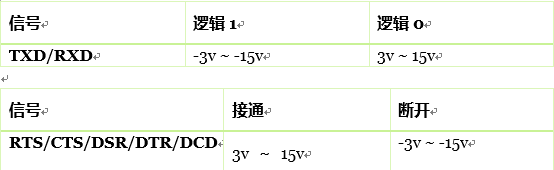

RS232C电气规定

EIA-RS-232C对电气特定、逻辑电平和各信号线功能都做了相关规定。在此部分,只简单介绍相关的电气特性。

对于RS232C标准对逻辑电平的定义,在数据部分,逻辑1的电平低于-3V;逻辑0的电平高于3V。在控制信号部分,信号有效的电平高于+3V;信号无效的电平低于-3V。在介于-3V~3V之间,高于15V,低于-15V的电压没有意义。

所以在实际的工作中,需要完成RS232电平与TTL电平的转换,以保证MCU,FPGA等能匹配RS232电平。最常用的芯片MAX232芯片可以完成TTL到RS232电平的转换。

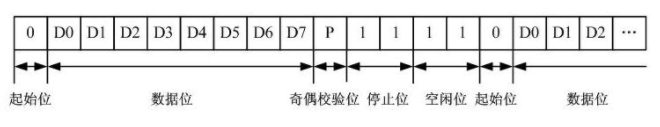

串行通信数据格式

一帧异步通信的数据格式主要包含以下几个部分:

起始位:以一位低电平开始,表示发送端开始发送一帧数据

数据位:即要传输的数据信息,低位在前,高位在后。数据位长度一般为5-10bit,常使用8bit.

奇偶校验位:用于校验数据的正确性,可以选择为奇校验或者偶校验

停止位:用于向接收端表示一帧数据已经发送完成,长度一般为1~2位。

空闲状态:一般用高电平表示,用于通知接收端等待数据传输。

RS232C的串行总线在空闲的时候总保持为逻辑1状态,即串行数据连接线上的电平为-3v~-15v。当需要传输一个字符时,首先会发送一个逻辑0为起始位,表示开始发送数据;之后就逐个发送数据位、奇偶校验位和停止位(逻辑1),每一次传输1个字符(通常为8bit).由于两次传输中的时间间隔是可变的,所以这种传输被称之为异步传输。

RS232C规定了一系列的波特率标准,常用的有9600b/s、115200b/s等。在设置波特率的时候,必须通知通信双方。

具体设计

本设计在KC705的Demo板上,实现了波特率为9600b/s,停止位为1bit,不带奇偶校验位,具有异步复位功能的串口通讯控制器。最终要求和PC上的超级终端完成双向通信。为了测试串口通信是否正常,在顶层设计的时候添加了可供测试验证的部分:当在开发板上按下button时,发送数据每次加1,并且当通过PC发送数据的时候,点亮对应的LED灯。

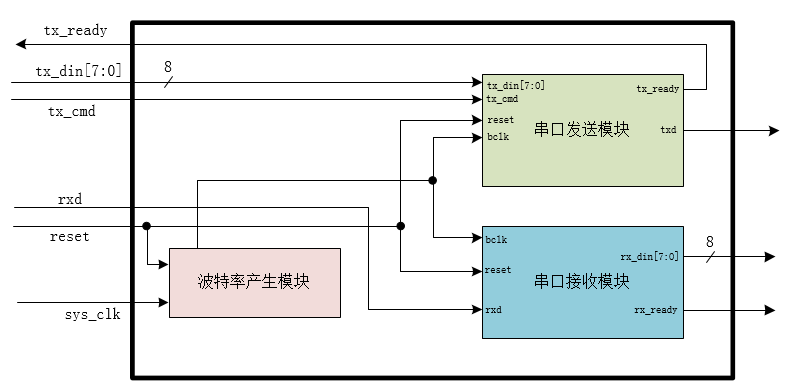

总体设计方案

RS232串口通信主要由波特率发生模块,串口数据发送模块,串口数据接收模块构成。在顶层设计中还加入了外部按键相应模块和LED驱动模块。总体设计框图如下:

在本设计中采用自底向上的设计方法。

波特率产生模块

板级整体输入时钟为50M,为了要产生9600b/s的波特率,那么必须使用分频器。一般来讲,为了提高系统的容错性处理,经常会要求波特率发生器的输出时钟为实际串口数据波特率的N倍,N一般取值为8、16、32等。由于串口通讯的速率较慢,取N倍后的时钟频率也不是很高&#