- 1已解决EROR 1064 (42000): You have an error in. your SOL syntax. check the manual that corresponds to yo_you have an error in your sol syntax; check the ma

- 2Hadoop学习日记-HDFS分布式文件存储系统整体概述_namenode和datanode分布式存储

- 3阿里云Big Data - |分层| ODS& DWD& DWS& ADS| 行为数仓_dws表 data

- 4一文读懂非关系型数据库(NoSQL)

- 5百度安全多篇议题入选Blackhat Asia以硬技术发现“芯”问题

- 6Locust性能测试教程_locust 性能测试

- 7Linux 常用命令与教程_/sbin:/usr/sbin:/usr/local/sbin:/root/bin:/usr/loc

- 8论文阅读:(AAAI 2019)M2det: A single-shot object detector based on multi-level feature pyramid network_a detector based on dl

- 9LCD1602命令代码整合

- 10基于JAVA高考志愿辅助填报系统

从零开始利用MATLAB进行FPGA设计(五)详解双口RAM_matlab仿真fpga

赞

踩

创作于谱仪算法设计过程中的数字能谱生成模块设计。

往期回顾:

从零开始利用MATLAB进行FPGA设计(四)生成优化HDL代码

从零开始利用MATLAB进行FPGA设计(三)将Simulink模型转化为定点数据类型

目录

1.关于双口RAM

简单说RAM表示随机存储器,作为一种易失型存储器,在计算机关闭或重新启动时RAM中存储的数据就会丢失。

FPGA工程实践中的RAM形式包括单口RAM(SPRAM)、简单双口RAM(Simple Dual Port RAM)和真双口RAM(True Dual Port RAM)。

单口RAM只有一套读写线,读写时分复用,不能同时读写。也就是说单口指的是一个读写数据接口,用于写入或读出。

对于双端口RAM来说,分别有一套读写地址线,可以同时进行读写(同一时间内读写地址不能冲突)。也就是说有两个读写数据接口。

简单双口RAM的A口只能用于写入,B口只能用于读出;真双口RAM的A口可以用于写入或写出,B口也可以用于写入或写出。

2.System Generation中的双口RAM

Xilinx的双口RAM允许使用多个数据宽度以不同的采样频率同时访问内存空间。

2.1模块接口

这种双口RAM有两组独立的端口,同时用于读写。独立的地址、数据和写使能端口允许对内存空间进行共享。每个端口组都有一个输出端口和三个输入端口,用于地址、输入数据和写使能。每个端口组也可以添加端口使能和同步复位。

这种双口RAM可以利用FPGA中的分布式存储器、块RAM或UtralRAM资源实现。

2.1.1形态因素

双口RAM块支持各种形态因素(FF),形态因素定义如下:

![]()

W是A和B端口的数据宽度,端口B的深度定义为:

![]()

输出端口具有和输入端口相同的数据类型。当形态因素为1时,端口A和B的输入端口可以具有不同算术类型和二进制点位置的数据;形态因素大于1时端口A和端口B的数据输入仅具有无符号的算术类型,二进制点为位于0。

通过在每个单独的地址端口提供有效地址,可以访问内存块中的位置进行读取或写入。有效地址是从0到d-1的无符号整数,其中d表示该端口的RAM深度(RAM中的字数)。在仿真中,试图读取内存末尾之后的位置会报错。当双口RAM在分布式存储器或块RAM中实现时,初始RAM内容可以通过块参数指定。每个写使能端口必须是一个布尔值。当WE端口为1时,数据输入端口上的值将被写入到地址线指示的位置。

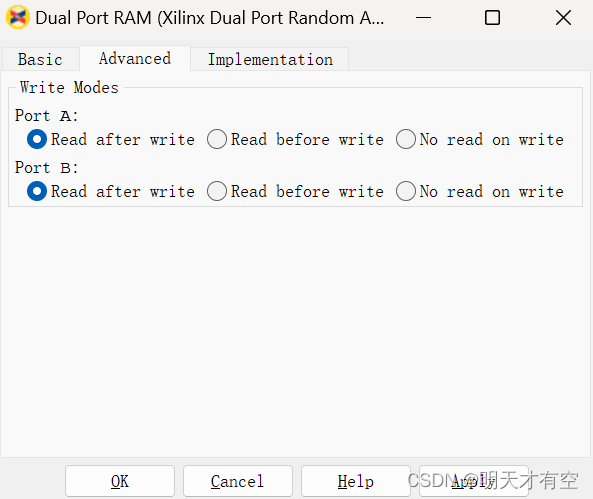

2.1.2写模式

当双端口RAM块在块RAM中实现时,可以在块参数对话框中设置块的写入模式。

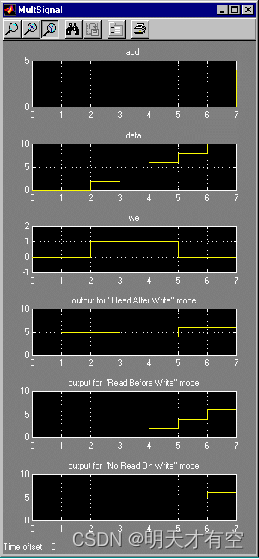

在写入操作期间,输出取决于写入模式。当WE为0时,输出端口具有由地址线指定的位置处的值。在写入操作期间,输入数据端口上呈现的数据被存储在由端口的地址输入选择的内存中。在写入周期中,可以将每个数据输出端口A和B的行为配置为以下选择之一:

写入模式可以借助下图描述。在图中,内存已设置为初始值5,并且地址位被指定为4。当使用无读取写入模式时,输出不受地址线的影响,并且输出与WE为0时的最后一次输出相同。对于另外两种模式,输出来自由地址线指定的位置,因此是正在写入的位置的值。这意味着输出可以是对应于写入后的旧值,这对应于写入后读取。

2.1.3冲突行为

- 读-读冲突:两个端口同时从同一存储单元读取,读取操作可以成功。

- 写-写冲突:两个端口同时从同一存储单元写入,则两个输出都被标记为无效。

- 读-写冲突:一个端口写入,另一个端口从同一存储单元读取的情况下,虽然内存内容不会被破坏,但读取端口上输出数据的有效性取决于写入端口的写入模式:

- 如果写入端口处于写入前读取模式,则另一个端口可以可靠地读取旧的存储器内容。

- 如果写入端口处于写入后读取或不读取写入模式,则读取端口输出的数据无效(NaN)。

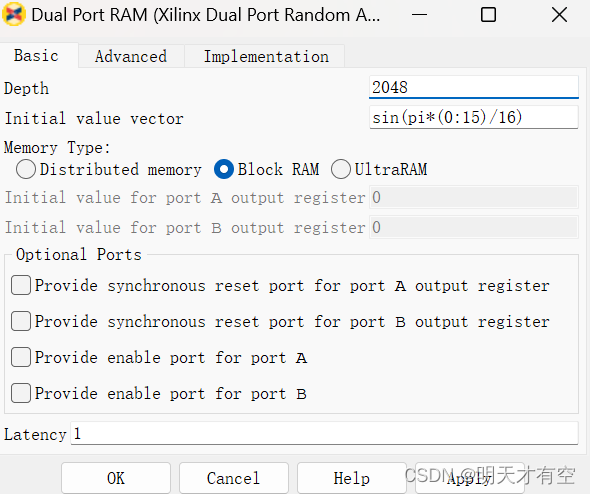

2.2块参数

Depth:指定端口A中内存的字数,必须是正整数。端口B的深度是由输入数据宽度指定的形态因素推断的。

Initial value vector:对于分布式存储器或块RAM,指定初始内存内容。初始值向量中元素的大小和精度基于为端口A指定的数据格式。当向量比RAM长时,向量的尾部元素被丢弃。当RAM比向量长时,RAM的尾部字被设置为零。初始值向量根据RAM的端口A上指定的精度进行饱和和舍入。UltraRAM存储器在上电或设备复位期间初始化为全0。

Memory Type:选择是否将双端口RAM实现为分布式存储器、块RAM或UltraRAM的选项。分布式双端口RAM始终设置为使用端口A处于写入前读取模式,端口B处于只读模式。