热门标签

热门文章

- 1RocketMQ定时(延迟)消息

- 23.图解排序算法(三)之堆排序

- 3【HarmonyOS 4.0 应用开发实战】如何配置环境、创建并运行项目_鸿蒙设备开发环境配置教程

- 4OCR文字识别领域经典论文总结_毕业论文 ocr自动识别 在游戏中的应用

- 5【官方】第18届全国大学生智能汽车竞赛百度完全模型组线上资格赛baseli_百度飞桨完全模型组

- 6USB控制器接口手动传递(XHCI Hand Off)的含义及编程实现_xhci hand off什么意思

- 7Spark RDD编程基础_rdd.map

- 8项目启动报错:If you want an embedded database (H2, HSQL or Derby), please put it on the classpath_consider the following: if you want an embedded da

- 9软件工程师资格证

- 10大学生选课系统|基于Springboot的大学生选课系统设计与实现(源码+数据库+文档)_数据库学生选课系统课程设计

当前位置: article > 正文

Xilinx基于MIG IP Core的DDR3设计【1】 -- 建立仿真平台_mig core 框图

作者:盐析白兔 | 2024-05-24 05:03:46

赞

踩

mig core 框图

在图像拼接的工程中,前端相机生成图像数据,需要对图像数据进行缓存后,再根据后端标准的HDMI时序输出图像数据。在这个过程中,因为前端相机的时钟与后端HDMI输出的时钟是不相同的,为了使输出的图像没有像素丢失,所以需要将相机图像先进行缓存,然后输出。对于高清图像,一帧图像所占用的存储空间比较大,单独依靠Xilinx器件内部的RAM是无法完成工作的,因为FPGA内部的RAM在级联以后对于布局布线过程是一个极大的挑战。为了避免布局布线所带来的问题,这就需要在整体的项目设计中引入DDR3来进行数据的缓存。

开发平台

硬件平台:KC705 MT8JTF12864HZ

软件平台:ISE14.7 / Vivado 2015.4 modelsim 10.2

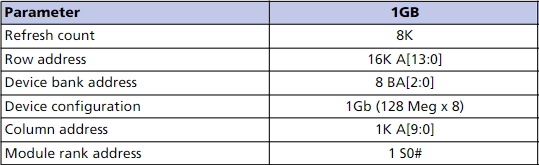

KC705开发板上所带的内存条为总存储大小为1GB的内存条,其地址空间参数如下如所示:

那么总的存储容量1GB是如何计算出来的呢?

从上图可以看出,该内存条总共包含1个RANK(S0#),8个BANK(BA[2:0]),在每一个BANK中,对应的行地址总数为16K(A[13:0]),列地址总数为1K

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/盐析白兔/article/detail/615949

推荐阅读

相关标签