- 1程序员入门培训班多少钱?可以学到哪些东西?_程序员培训班要多少钱

- 2jwt 介绍_怎么查看一个浏览器网页的jwt

- 32021年危险化学品生产单位安全生产管理人员考试题库及危险化学品生产单位安全生产管理人员考试内容_人体是导体,在静电场中可能接触起电

- 4Vivado工程经验与时序收敛技巧_vivado fix cell

- 5算法——动态规划_完全加括号是什么意思

- 6git代码库迁移保留commit历史_Git 如何迁移仓库并保留 commit 记录

- 7RK3328 Debian安装OpenMediaVault

- 8git 拉取代码时显示Filename too long的解决办法_git file name too long

- 9系统盘50G,数据盘100G(需求:将数据磁盘扩容至1T)_系统盘和数据盘配比

- 10WooCommerce入门指南:简介

FPGA芯片选型和命名规则_fpga型号命名规则

赞

踩

1. 芯片选型

在采用FPGA电路设计中,首先要进行芯片选型。而芯片选型都是根据你的设计需求来找器件。需求可能涉及以下几个方面:

1. 时钟速度(逻辑时钟、IO时钟等),不同Family能达到的速度不同

2. 时钟数量,不同Family的时钟资源不同

3. IO数目和支持的电平标准

4. 板上封装(焊接方式、体积大小)

5. 其他各种硬核功能(PowerPC,MGT,GTP,TEMAC等)

6. 功耗要求,顺便考虑散热空间

7. 非易失性要求,Spartan 3A系列有内置Flash

8. 产品调试和升级扩容空间,比如调试时用较大的器件,完成后改用同样封装较小规模的器件

1.1 Xilinx芯片

6系列用ISE开发,7系列用vivado。

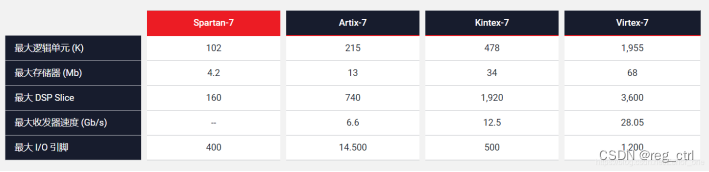

- Spartan-7 的定位为低成本应用,容量中等,性能仅为满足一般的逻辑设计要求。

- Artix-7 和 Kintex-7 均可认为其定位为高性价比:

- Artix-7 系列提供了最高性能功耗比结构、收发器线速、DSP 处理能力以及 AMS 集成;

- Kintex-7 系列最佳成本/性能/功耗平衡,同时提供高 DSP 率、高性价比封装;

- Virtex-7 则定位为高性能应用,容量大,性能定位为能满足各类高端应用。

关于各系列的片上资源,可直接参考各系列的芯片选型手册:

Cost-Optimized Portfolio Product Tables and Product Selection Guide

All Programmable 7Series Product Selection Guide

UltraSCALE FPGA Product Tables and Product Selection Guide

1.2 Altera芯片

Altera 的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Cyclone,CycloneII;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Startix,StratixII等,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件

2. 芯片命名规则

2.1 Altera命名规则

器件系列 + 器件类型(是否含有高速串行收发器) + LE 逻辑单元数量 + 封装类型 + 高速串行收发器的数量(没有则不写) + 引脚数目 + 器件正常使用的温度范围 + 器件的速度等级 + 后缀举例:

EP4CE10F17C8N 为例

- EP4C:Altera 器件 Cyclone IV 系列;

- E/GX:E 表示普通逻辑资源丰富的器件,GX 表示带有高速串行收发器的器件;

- 10:LE 逻辑单元的数量,单位为 k,10 表示约有 10k 的逻辑单元;

- C:表示高速串行收发器的数量,该芯片没有高速串行收发器所以不写;

- F:表示 PCB 封装类型,F 是 FBGA 封装,E(EQFP)、Q(PQFP)、U(UBGA)、M(MBGA);

- 17:表示引脚数量,17 代表有 256 个引脚;

- C:工作温度,C 表示可以工作在 0℃到 85℃(民用级),I 表示可以工作在-40℃

- 到 100℃(工业级),A 表示可以工作在-40℃到 125℃(军用级);

- 8:器件的速度等级,6 最大约是 500MHz,7 最大约是 430MHz,8 最大约是400MHz

- N:后缀,N 表示无铅,ES 代表工程样片。

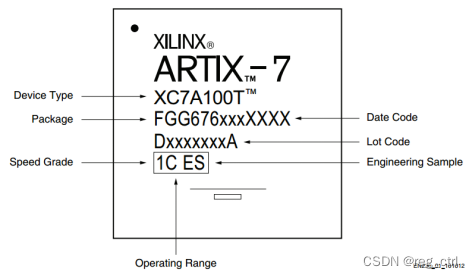

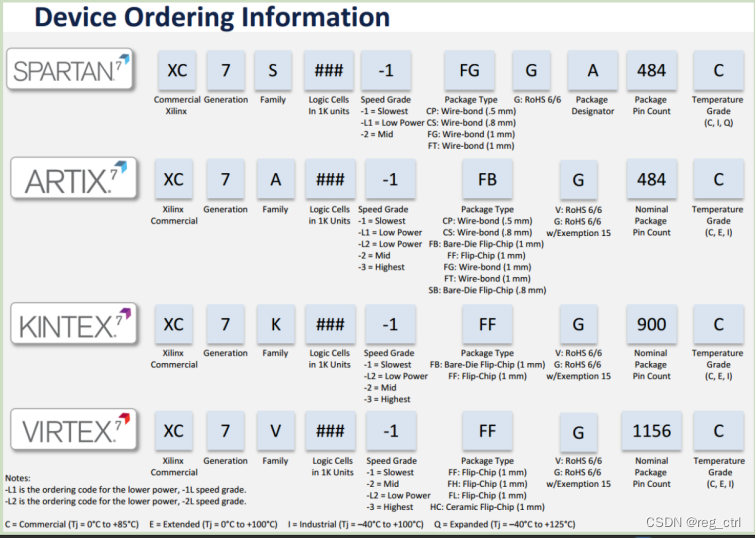

2.2 Xilinx的FPGA命名规则

UG-112:Device Package User Guide

UG-116:Device Reliability Report

譬如,对于编号为XC4VLX60-1FFG668CS2的FPGA,器件类型是XC4VLX60-10,封装是FFG668CS2。具体而言

- XC4VLX:代表FPGA的家族,这里是VIRTEX 4LX

- 60: 代表system gates或logic cells的数目,即60,000

- -1: 代表速度等级

- FFG: 是封装方式(Pb-free flip-chip BGA)

- 668: 是引脚数目

- C: 代表的温度等级Temperature grade ,这里是商用(Commercial)

- S2: 即step2

2.3 速度等级

序号越低,速度等级越高 这是Altera FPGA的排序方法,“序号越高,速度等级也越高”这是Xilinx FPGA的排序方法

在芯片生产出来之后,实际测试标定出来的;速度快的芯片在总产量中的比率低,价格也就相应地高。

一般来讲,提高一个速度等级将带来 12%到 15%的性能提升,但是器件的成本却增加了 20%大 30%。如果利用设计结构来将性能提升12%到 15%(通过增加额外的流水线),那么就可以降低速度等级,从而节约20%大 30%的成本;

2.4 温度等级

3. FPGA IO引脚及命名方式

参考:FPGA开发者看过来:IO是怎么命名的?上电又有什么规律?__凤凰网

命名方式多样,A13,B14,BANK34,BANK12,MIO0,EMIO···。这是FPGA的特点,FPGA可以兼容多种不同的电压标准,也有丰富的IO。

FPGA的IO物理命名规则,也就是我们做管脚约束时候的命名,芯片通常是长方体或者正方体,所以命名通常采用字母+数字组合的方式。

xilinx的命名(xilinx的文档是行业标杆,其它FPGA厂家的资料多多少少会参考xilinx)通常xilinx 的功能命名格式为:IO_LXXY#/IO_XX。其中:

- (1) IO代表用户IO;

- (2) L代表差分,XX代表在当前BANK下的唯一标识号,Y=[P|N]表示LVDS信号的P或者N;

- (3) #表示Bank号。

例如:IO_L13P_T2_MRCC_12,这是一个用户IO,支持差分信号,是BANK12的第13对差分的P端口,与此同时它也是全局时钟网络输入管脚(MRCC是全局时钟网络)

除了FPGA的用户IO外,还有很多其他的功能IO,如下载接口,模式选择接口,还有MRCC,最重要的是FPGA的电源引脚。

Zynq有两套独立的供电系统,(PS和PL),因此没有上电时序需求