热门标签

热门文章

- 1用cmd在每行文本前添加相同内容_dos如何在每行前加一个字

- 2【刷题记录15】Java工程师丨腾讯面试真题(3)_第一行输入,表示一共有 组数据第二个是n个空格分隔的整数,h1,h2,h3,..hn代表建筑

- 3一文看懂大数据生态圈完整知识体系【大数据技术及架构图解实战派】_互联网和大数据知识体系图

- 4MySQL用into outfile导出出错The MySQL server is running with the --secure-file-priv option so it cannot ex_windows into outfile running with the --secure-fil

- 5电子班牌系统服务器,校园班牌系统,电子班牌系统,智慧校园班牌系统

- 6 前端需要什么样的方案设计

- 7RetinaNet模型解析

- 8LeetCode刷题笔记(JAVA)——14. 最长公共前缀

- 9微调BERT实现对IMDB数据集的情感分析(Sentiment Analysis)

- 10大数据技术与应用(Spark),2024年最新含面试题+答案_spark面试问题

当前位置: article > 正文

三人表决电路——Verilog HDL语言_verilog三人表决器代码

作者:知新_RL | 2024-05-04 20:11:44

赞

踩

verilog三人表决器代码

任务描述

根据所学的组合逻辑及数字电路的知识完成三人表决电路的设计,实现少数服从多数的表决规则,根据逻辑真值表和逻辑表达式完成表决功能。

运用Verilog HDL进行设计,完善三人表决电路的功能描述风格代码,具备组合逻辑电路的设计仿真和测试的能力。

相关知识

逻辑原理

三人表决电路中, 当表决某个提案时,多数人同意,则提案通过;同时有一个人具有否决权。若全票否决,也给出显示。

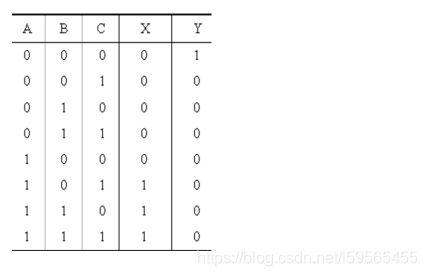

设输入为 A、 B、 C,且 A 具有否决权。同意用1 表示,不同意用 0 表示;输出 X 为 1 时表示提案通过; Y 为 1 时表示提案全票否决。 则三人表决电路的真值表如下表所示。

三人表决器真值表

编程要求

根据真值表,编写的程序要能根据不同的输入完成三人表决功能。

源代码

测试平台:EduCoder

module JG3(ABC,X,Y); input [2:0] ABC; output X, Y; reg X, Y; always@(ABC) // 请在下面添加代码,实现满足三人表决器真值表; /********** Begin *********/ case(ABC) //3'b000:begin X<=1'b0;Y<=1'B1;end 3'b000:begin X=1'b0;Y=1'b1;end 3'b001:begin X=1'b0;Y=1'b0;end 3'b010:begin X=1'b0;Y=1'b0;end 3'b011:begin X=1'b0;Y=1'b0;end 3'b100:begin X=1'b0;Y=1'b0;end 3'b101:begin X=1'b1;Y=1'b0;end 3'b110:begin X=1'b1;Y=1'b0;end 3'b111:begin X=1'b1;Y=1'b0;end default:begin X=1'b1;Y=1'b0;end endcase /********** End *********/ endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

觉得有帮助的可以点个赞再走哦!!

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/知新_RL/article/detail/535961

推荐阅读

相关标签