- 1axios get怎么还会显示跨域_axios解决跨域问题(vue-cli3.0)

- 2license是如何生成的 license生成原理

- 3pca主成分分析结果解释_主成分分析(PCA)原理精讲 | 统计学专题

- 4uniapp小程序如何分包?完整详细步骤教给你【小白教程】_uniapp小程序分包

- 52021年最新总结,腾讯、阿里、美团、百度、字节跳动、京东等技术面试题,以及答案,专家出题人分析汇总。持续更新中。_rtskmpk

- 6VTK9.2.0+QT5.14.0绘制三维显示背景

- 7Web前端JS通过getUserMedia API 获取 麦克风(话筒)、摄像头(相机) 等音视频多媒体数据(语音、录音、录屏、相机、视频对话、屏幕共享、流媒体)_js获取麦克风权限

- 8C语言单链表面试题详解_单链表的题看不懂

- 92023年五一杯A题无人机定点投放问题完整论文+代码分析_无人机定点投放数学建模论文

- 10为什么说深耕AI领域绕不开知识图谱?

FPGA工程经验_vivado 12-1411

赞

踩

一、引脚分配及电平

码给自己看,工程路径是

D:/E_Learning_doc/FPGA/AD7616/my_ip_AD7616/0317

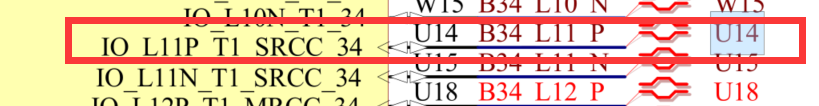

1、对于电路中的时钟信号要放到专用引脚,对于单端时钟,要放到SRCC或者MRCC的P端。

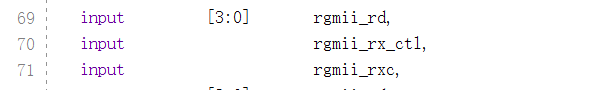

在将PS端的以太网通过EMIO引出时,用到了gmii_to_rgmii的IP核,在分配它的时钟引脚rgmii_rxc时报了一个错

[DRC UCIO-1] Unconstrained Logical Port: 1 out of 167 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: rgmii_rxc.

大致意思是说没给rgmii_rxc分配引脚,但是我明明在约束文件给了引脚分配,结合下面的警告猜测到了上面说的问题

[Vivado 12-1411] Cannot set LOC property of ports, Illegal to place instance i_system_wrapper/system_i/gmii_to_rgmii_0/U0/i_gmii_to_rgmii_block/system_gmii_to_rgmii_0_0_core/i_gmii_to_rgmii/i_gmii_to_rgmii/bufio_rgmii_rx_clk on site TIEOFF_X78Y88. The location site type (TIEOFF) and bel type (HARD0) do not match the cell type (BUFIO). Instance i_system_wrapper/system_i/gmii_to_rgmii_0/U0/i_gmii_to_rgmii_block/system_gmii_to_rgmii_0_0_core/i_gmii_to_rgmii/i_gmii_to_rgmii/bufio_rgmii_rx_clk belongs to a shape with reference instance i_system_wrapper/system_i/gmii_to_rgmii_0/U0/i_gmii_to_rgmii_block/rgmii_rxc_ibuf_i. Shape elements have relative placement respect to each other. The invalid location might results from a constraint on any of the instance in the shape. [“D:/E_Learning_doc/FPGA/AD7616/my_ip_AD7616/0317/AD7616_BD/parallel_if_constr.xdc”:3]

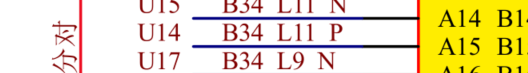

将引脚按这个要求更改后: “对于电路中的时钟信号要放到专用引脚,对于单端时钟,要放到SRCC或者MRCC的P端”,上面的错误就解决了,而且这个IP的这几个脚一定要放到同一个BANK,不然还会报错。因为我的rgmii_rd和rgmii_rx_ctl选了BANK34的脚,所以rgmii_rxc我也需要选了BANK34的脚。图中的B34代表BANK34

2、查看FPGA的BANK电压方法

在原理图里面找到这些模块,然后看 VCCO_XX 引脚的电压,后面的XX代表BANK,VCCO_13就表示BANK13,接的电平是3V3就表示这个BANK的引脚都是3V3的。

还是上面的这个工程,看到VCCO_34接的电压是VCC_ADJ,找到原理图中VCC_ADJ是3V3的电平,所以在引脚约束时选的是LVCOMS33

二、Z7的MIG IP核使用问题

在综合MIG IP核时可以选择Global和Out of context per IP。选择Out of context per IP时报了下面的错误

[Opt 31-67] Problem: A LUT5 cell in the design is missing a connection on input pin I2, which is used by the LUT equation. This pin has either been left unconnected in the design or the connection was removed due to the trimming of unused logic. The LUT cell name is: u_mig_7series_0/u_mig_7series_0_mig/u_memc_ui_top_std/mem_intfc0/mc0/rank_mach0/rank_common0/refresh_generation.refresh_bank_r[0]_i_1.

但是后面综合IP核时改为Global又不会报这个错误。

MIG的这个配置界面每次只要一旦双击打开过这个IP核,这个配置就会自己跳回到400M,即使后面点了Cancel没保存设置,一样会自己跳回去。所以一旦手贱一不小心点开了就要重新设置一次