数字系统设计

1、数字电路(Digital Circuit) :对数字信号进行算术运算和逻辑运算的电路。

2、组合逻辑电路: 组合逻辑电路的输出只依赖于当前输入,与输入历史无关。

- 高电平、低电平----二值逻辑

- 二-十进制码(BCD码-Binary-Coded-Decimal): 8421BCD码、2421码、余3码

- 格雷码:相邻的两个码组之间仅有一位不同

- 十进制数 8421BCD码 余3码 格雷码

0 0000 0011 0000

1 0001 0100 0001

2 0010 0101 0011

3 0011 0110 0010

4 0100 0111 0110

5 0101 1000 1110

6 0110 1001 1010

7 0111 1010 1000

8 1000 1011 1100

9 1001 1100 0100 - ASCII码:键盘的键符用7位二进制码表示

- 布尔代数、逻辑门:与、或、非 与门、或门、非门、与非门、或非门、异或门

- 逻辑函数表示方法:真值表、逻辑表达式、逻辑图、时序图

- 逻辑函数的化简:最小项、卡诺图

- 组合逻辑设计方法:真值表--表达式--卡诺图化简--逻辑电路图

- 常用组合逻辑电路:编码器、译码器、数据选择器、数据分配器、数值比较器、加法器、函数发生器、奇偶校验器

- 译码器

- 2-4译码器

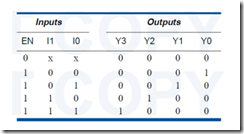

2线4线译码器 真值表

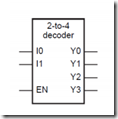

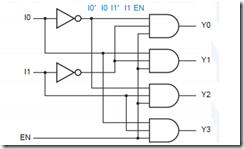

2-4译码器 电路符号 2-4译码器 门级原理图

- 译码器(74X138--3线8线译码器)

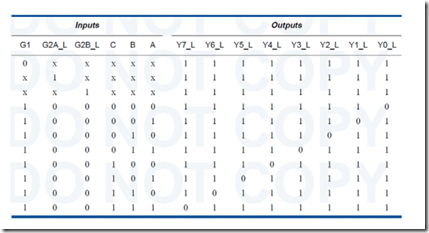

74X138 真值表

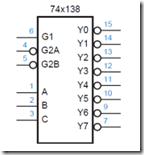

74X138 电路符号

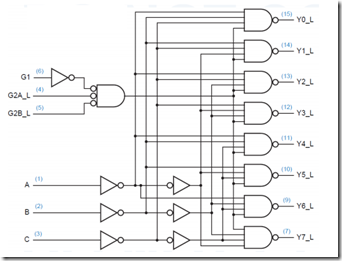

74X138 门级原理图

- 编码器

- 普通编码器

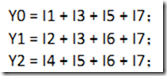

逻辑表达式

8-3编码器 门级原理图

- 优先编码器

优先编码器符合

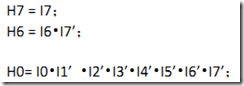

优先编码器 中间变量H7---H0

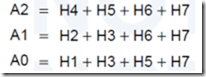

逻辑表达式 A2—A0

IDEL 表达式

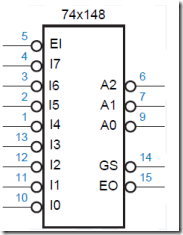

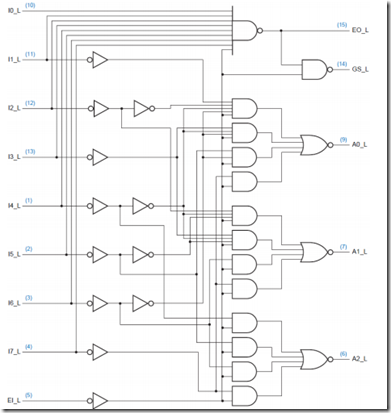

74X148--8输入优先编码器

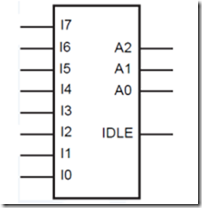

74X148--8输入优先编码器 符号

74X148--8输入优先编码器 门级原理图

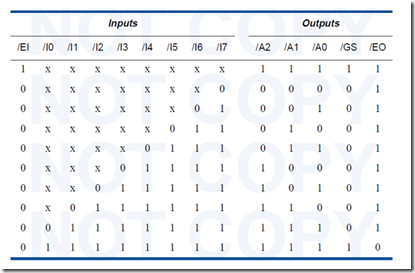

74X148--8输入优先编码器 真值表

- 数据选择器

- 数据选择器(74X151--1位宽8选1数据选择器)

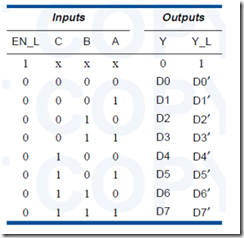

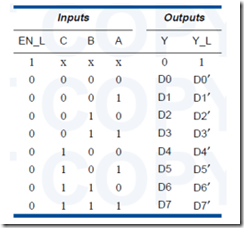

74X151--1位宽8选1数据选择器 真值表

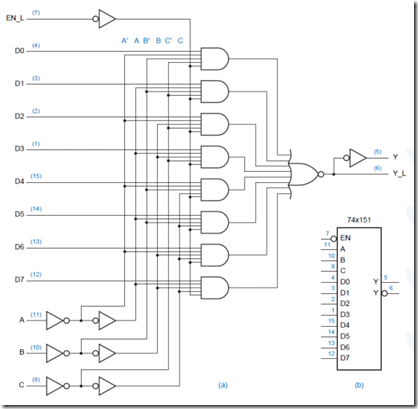

74X151--1位宽8选1数据选择器 门级电路图及符号

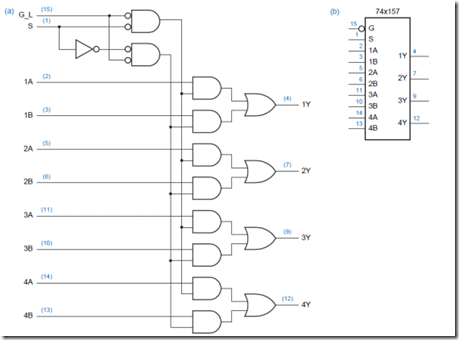

- 数据选择器(74X157--4位宽2选1数据选择器)

数据选择器(74X157--4位宽2选1数据选择器)真值表

数据选择器(74X157--4位宽2选1数据选择器) 门级电路图及符号

- 数值比较器

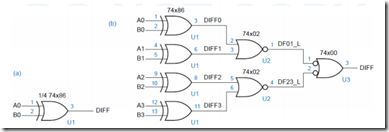

- 比较器(74X86--异或门、74X85--4位比较器)

74X86--异或门构成比较器

3、时序逻辑电路: 时序逻辑电路的输出不仅依赖于输入的当前值,而且还依赖于输入的历史值。

- 由于时序逻辑电路的输出依赖于输入的历史值,因此时序逻辑电路中必须包含存储元件(memory

elements),时序逻辑电路使用存储元件“记忆”输入的历史。 - 时序电路的输出依赖于它的状态,时序电路也成为有限状态机。有限状态机分为两类:摩尔状态机和米利状态机。 摩尔状态机的输出只由电路的状态决定,与电路的输入无关(输入决定电路状态)。米利状态机至少有 1个输出由输入和状态共同决定。

- 时序逻辑分为异步时序和同步时序两大类。 异步时序逻辑电路的存储元件不是在统一的时钟信号控制下工作,电路中存储元件的状态的更新不是同时发生的,这种电路称为异步时序电路,异步时序电路的状态转换难易预知,这给电路的设计和调试带来很大困难。