- 1手把手教你给电脑安装manjaroLinux操作系统_manjaro linux

- 2crossover软件2023跨电脑系统兼容工具好用吗?_crossover软件好用吗

- 3解读iaas-pre-host.脚本(国基北盛)_iaas-pre-host b

- 4QT配置android环境,简单易懂_qt andriod

- 5opencv 暴力特征匹配+FLANN特征匹配_java使用opencv的bf匹配器

- 6“AttributeError: module ‘cv2‘ has no attribute ‘SIFT_create‘ “_attributeerror: module 'cv2.cv2' has no attribute

- 7阿里云域名备案流程分析和采坑总结_并在开通之日起30日内登录全国互联网安全管理平台提

- 8C++判断质数

- 9Docker 容器编排之 --- docker-compose 详解_docker-compose.yml 用#号注释吗

- 10elasticsearch 基础介绍及使用 (high-level-client)_elasticsearch highlevelclient

【计算机组成与体系结构Ⅰ】实验5 CPU组成与机器指令执行实验_cpu组成与机器指令执行实验报告

赞

踩

一、实验目的

1:将微程序控制器同执行部件(整个数据通路)联机,组成一台模型计算机。

2:用微程序控制器控制模型机数据通路。

3:通过CPU运行几条机器指令(排除中断指令)组成的简单程序,掌握机器指令与微指令的关系,牢固建立计算机的整机概念。

二、实验设备

TEC-4计算机组成原理实验系统(实验箱)和仿真软件。

三、实验内容

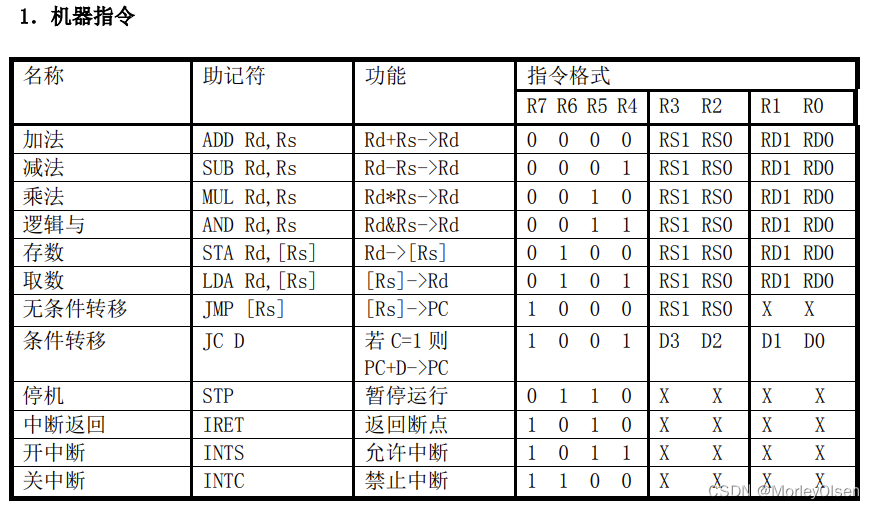

1:机器指令系统组成的简单程序进行译码

| 存储地址 | 指令 | 机器代码 |

| 00H | LDA R0,[R2] | 0101 1000 |

| 01H | LDA R1,[R3] | 0101 1101 |

| 02H | ADD R0,R1 | 0000 0100 |

| 03H | STP | 0110 0000 |

2:根据框图完成连线

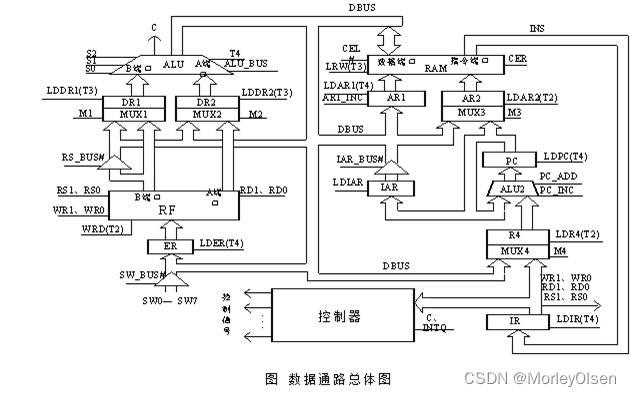

控制器是控制部件,数据通路(包括数据通路总图中运算器、存储器及输入输出等各模块)是执行部件,时序产生器是时序部件。

1)将跳线开关J1用短路子短接。时序发生器的输入TJI接控制存储器的输出TJ。控制器的输入C接运算器ALU的C。控制器的输入IR7、IR6、IR5、IR4依次指令寄存器IR的输出IR7、IR6、IR5、IR4。共6条线。

2)控制器的输出LDIR(CER)、LDPC(LDR4)、PC_ADD、PC_INC、M4、LDIAR、LDAR1(LDAR2)、AR1_INC、M3、LDER、IAR_BUS#、SW_BUS#、RS_BUS#、ALU_BUS、CEL#、LRW、WRD、LDDR1(LDDR2)、M1(M2)、S2、S1、S0依次与数据通路的对应信号连接。共27条线。

3)指令寄存器IR的输出IR0接双端口寄存器堆的RD0、WR0,IR1接RD1、WR1,IR2接RS0,IR3接RS1。共6条线。

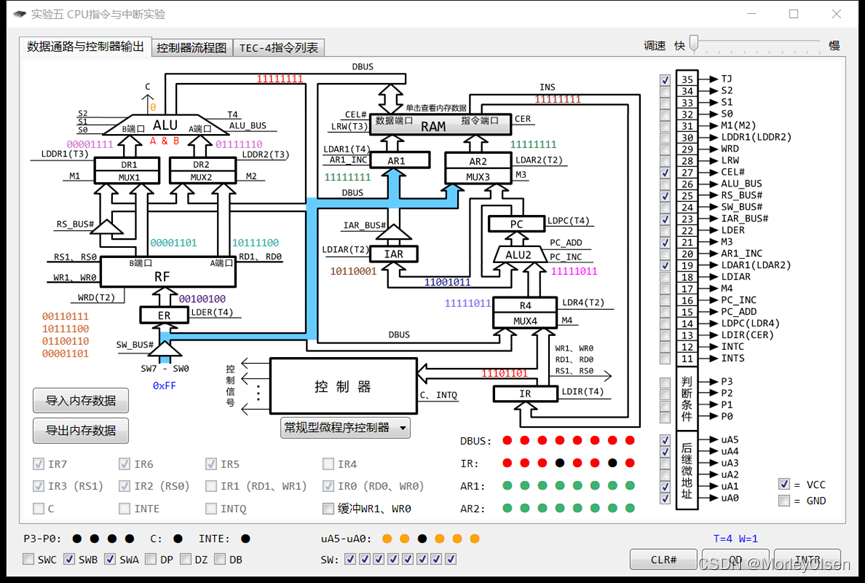

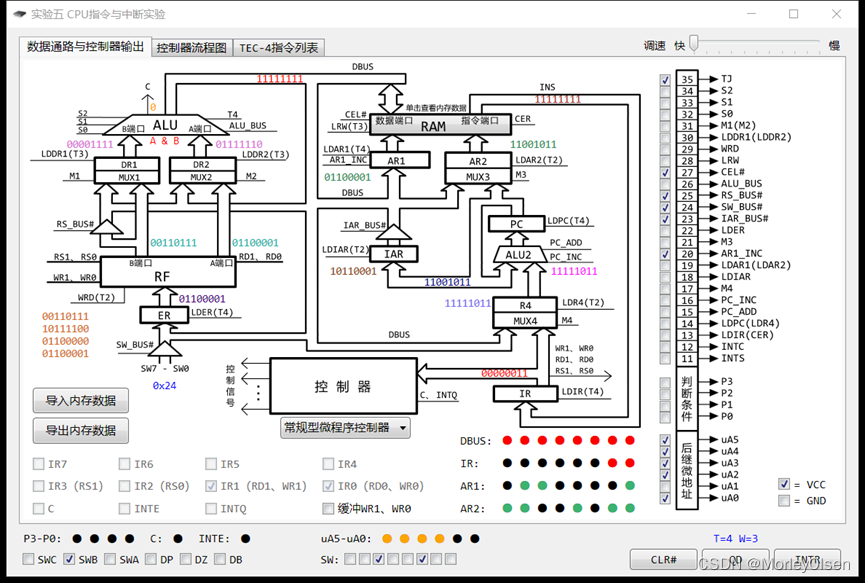

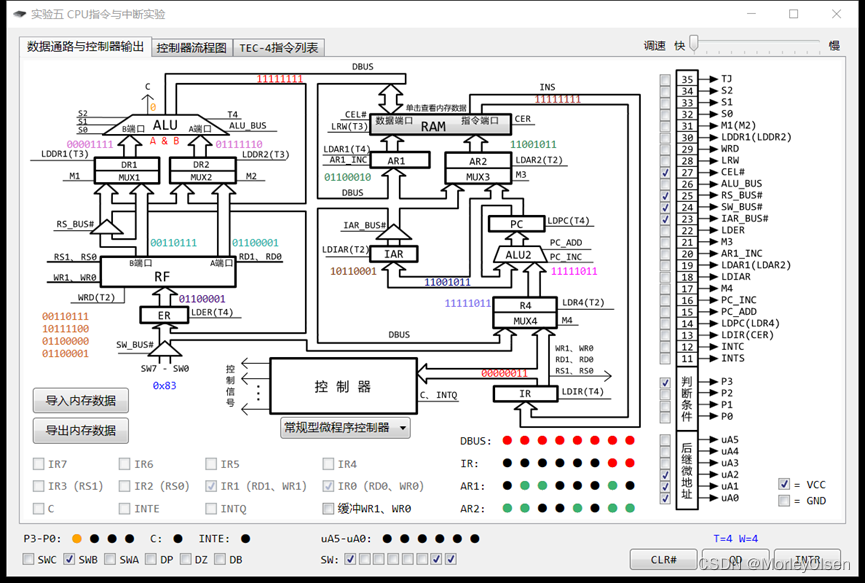

以仿真面板为例,各部件(微程序控制器、数据通路、控制台)之间所需要的连线如下图所示:

最终的连线结果如下图所示:

3:存程序机器代码,设置通用寄存器R2、R3及内存相关单元的数据

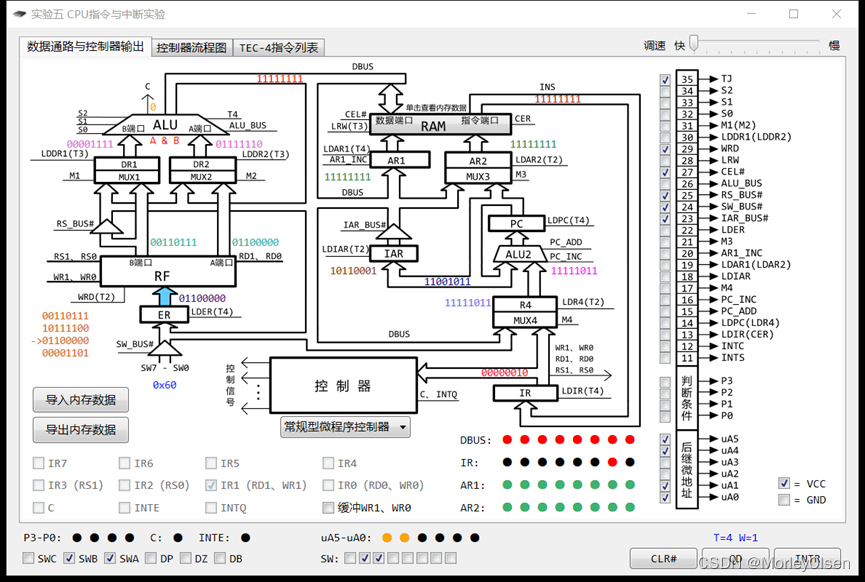

● 设置通用寄存器R2、R3的值

第一步:令DP=0,DB=0,DZ=0,使实验系统处于连续运行状态。令SWC=0、SWB=1、SWA=1,使实验系统处于寄存器加载工作方式KLD。按CLR#按钮,使实验系统处于初始状态。

第二步:令SW=1111 1111,按下QD。即把RAM中的FF内存单元供设置通用寄存器使用,此步为选中RAM中的FF内存单元.

第三步:令SW=0000 0010,按下QD。即把通用寄存器R2的寄存器号写入IR中。

第四步:令SW=0110 0000,按下QD。即把60H写入IR指定的R2寄存器中。

第五步:令SW=0000 0011,按下QD。即把通用寄存器R3的寄存器号写入IR中。

第六步:令SW=0110 0001,按下QD。即把61H写入IR指定的R3寄存器中。

第七步:按下CLR#,使实验系统恢复到初始状态。

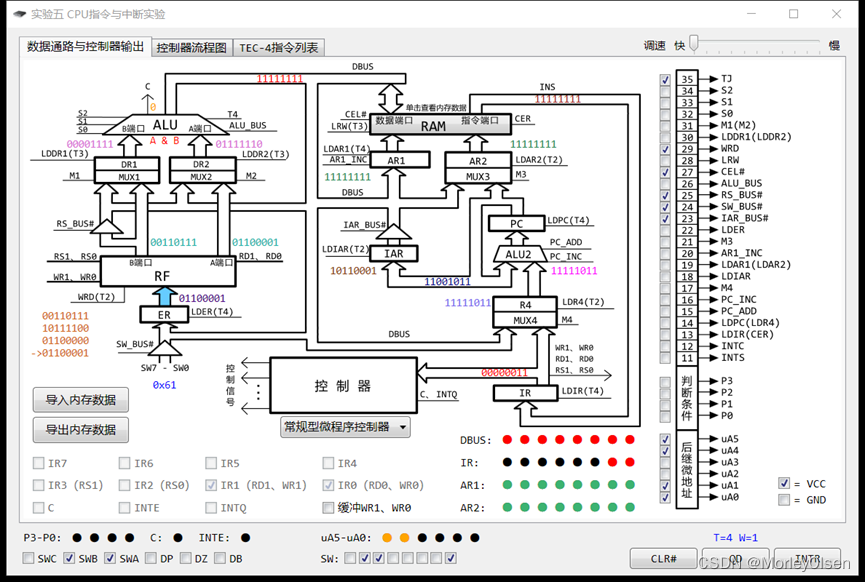

● 存程序机器代码

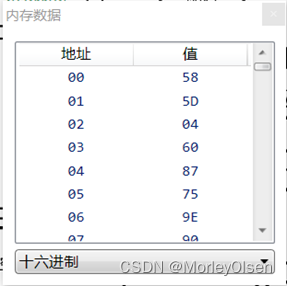

第一步:令DP=0,DB=0,DZ=0,使实验系统处于连续运行状态。令SWC = 0、SWB = 1、SWA = 0,使实验系统处于写双端口存储器工作方式KWE。按CLR#按钮,使实验系统处于初始状态。

第二步:令SW=0000 0000,按下QD。将00H写入AR1。

第三步:令SW=0101 1000,按下QD。将58H写入存储器00H单元。AR1自动加1,变为01H。

第四步:令SW=0101 1101,按下QD。将5DH写入存储器01H单元。AR1自动加1,变为02H。

第五步:令SW=0000 0100,按下QD。使AR1+1,AR1此时为03H。

第六步:令SW=0110 0000,按下QD。使AR1+1。AR1此时为04H。

第七步:按CLR#,令SW=0110 0000,按下QD。将60H写入AR1。

第八步:令SW=0010 0100,按下QD。将24H写入存储器60H单元。AR1自动加1,变为61H。

第九步:令SW=1000 0011,按下QD。将83H写入存储器61H单元。

第十步:按CLR#,使实验系统恢复到初始状态。

第十一步:查询01H、02H、03H、04H、60H、61H存储单元中在之前步骤中所存储的数据是否正确。

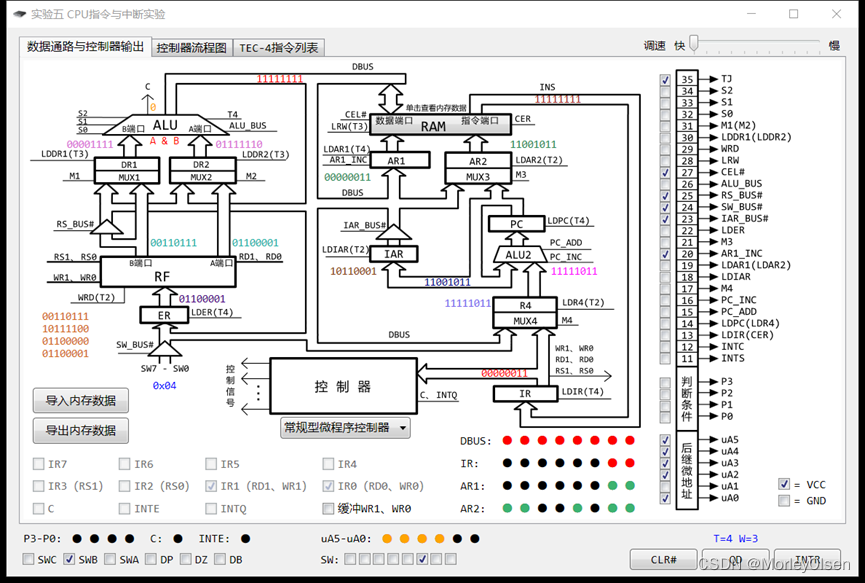

4:用单拍(DP)方式执行一遍程序

设置SWC=0,SWB=0,SWA=0,计算机处于PR启动程序阶段,同时设置DP=1,DB=0,DZ=0,用SW7-SW0设置这几条指令的起始地址00H,按QD单拍执行。观察执行过程微地址变化和执行结果如下表所示:

| QD次数 | 后继微地址 | 执行内容 |

| 1 | 000111 | 取指 |

| 2 | 000101 | 译码 |

| 3 | 010101 | 加载寻址 |

| 4 | 110110 | 读取 |

| 5 | 110100 | 写入 |

| 6 | 001111 | 取指 |

| 7 | 000101 | 译码 |

| 8 | 010101 | 加载寻址 |

| 9 | 110110 | 读取 |

| 10 | 110100 | 写入 |

| 11 | 001111 | 取指 |

| 12 | 000101 | 译码 |

| 13 | 010000 | 加法寻址 |

| 14 | 111011 | 运算加法 |

| 15 | 110100 | 写入 |

| 16 | 001111 | 取值 |

| 17 | 000101 | 译码 |

| 18 | 010110 | 停机 |

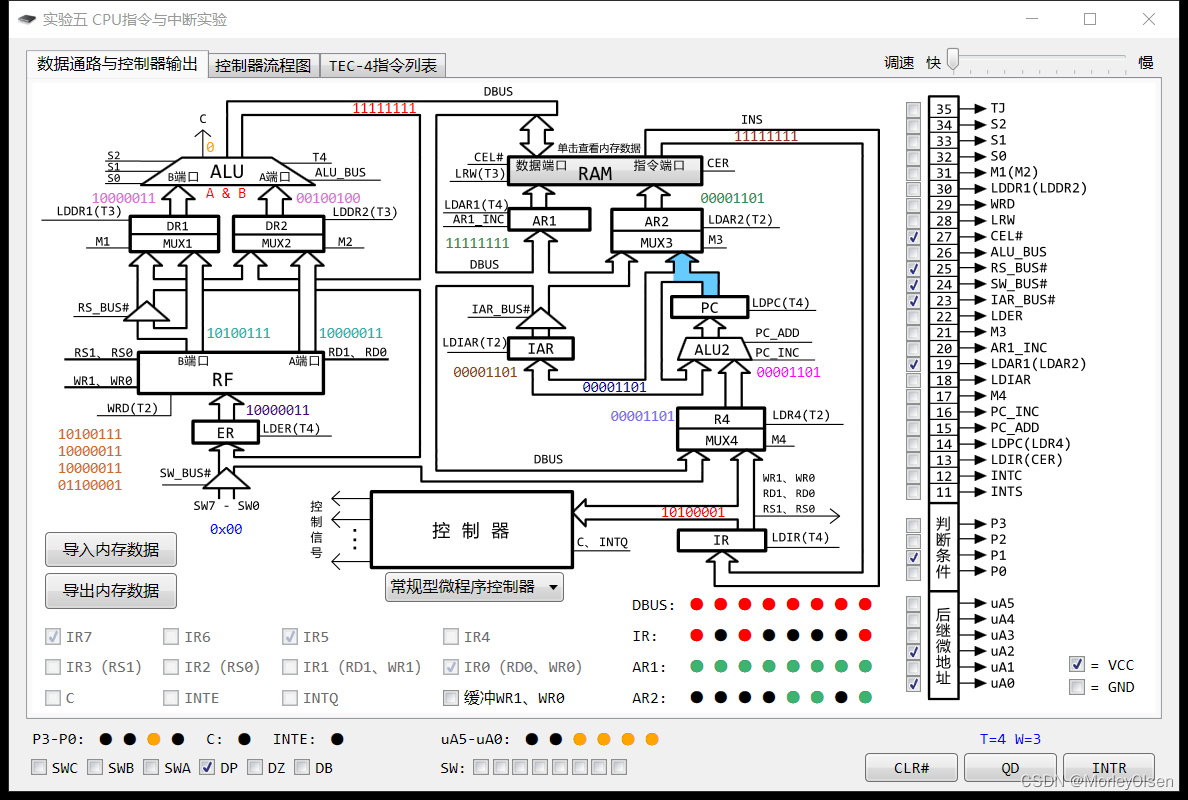

最终运行结果如下图所示:保存在R0处的数据为两数相加的结果A7(1010 0111)。

5:比较单拍和单指方式执行程序

两种条件下寄存器的数据如下表所示:

| 单拍模式 | 单指模式 | |

| R0 | 0010 0100 | 1010 0111 |

| R1 | 1000 0011 | 1000 0011 |

| R2 | 0110 0000 | 0110 0000 |

| R3 | 0110 0001 | 0110 0001 |

四、实验数据通路总图

五、分析问题

1:为什么IR0,IR1对应接RD0、RD1, 还要接WR0、WR1?

RDl、RD0选择从A端口读出的寄存器,WR0、WR1选择被写入的寄存器。由于运算结果需写回寄存器中,因此需要同时指WRl、WR0,即IR0和IR1需要同时连接RD0、RD1和WR0、WR1。

2:KLD方式的功能是什么?为什么要用到内存的一个存储单元?

KLD的功能是加载寄存器堆。该存储单元供设置通用寄存器使用,在设置通用寄存器值的时候,该存储单元会暂存寄存器的编号。该存储器地址最好是不常用的一个地址,以免设置通用寄存器操作破坏重要的存储器单元的内容0。在本次实验中选用的为FFH。

3:总结实验出现的问题、解决办法,实验体会。

- CPU运行指令主要需要如下几个过程:

取指令:CPU的控制器从内存读取一条指令并放入指令寄存器。指令的格式一般是操作码+操作数的地址;

指令译码:指令寄存器中的指令经过译码,决定该指令应进行何种操作(操作码)、操作数的地址。

执行指令:执行指令分为取操作和进行运算两个阶段。

修改指令计数器,决定下一条指令的地址。 - 模型计算机如何区分所取的8位是数据还是指令:数据和指令存放在RAM存储器中。执行指令的过程分为取指令、指令译码、取操作数、运算、送结果。程序运行时计算机会根据指令和数据的访问阶段不同来区分二者,在取指令阶段取出的为指令,在取操作数阶段取出的为数据。

TEC4-A模型计算机一条机器指令的字长为8位,前4位为操作码、后4位为寄存器编号。具体的机器指令格式如下图所示:

- 在本实验中,把数据和地址存入RAM中的操作是一样的,首先通过SW7~SW0选中RAM中的目标存储单元,然后将数据通过SW7~SW0存入目标存储单元中。

- 在本实验中,我们从00地址开始存4个机器代码,对应4条机器指令。在 60H存入24H,用于给R0置初值;在61H存入 83H,用于给R1置初值。

- CPU的内部结构可分为:控制单元、逻辑运算单元、存储单元三大部分。其中,控制单元完成数据处理整个过程中的调配工作;逻辑单元完成各个指令以便得到程序最终想要的结果;存储单元负责存储原始数据以及运算结果。

- 数据通路的各端口和微程序控制器的各端口相连,是因为微程序控制器需要向数据通路发出控制信号,以控制数据通路的运行。

- 在本实验中,我们首先设置了通用寄存器内的值,然后在RAM里面存入了程序机器指令,最后通过单拍或单指的方式执行了一遍程序。因此,程序编写和运行的过程整体同上,即先存指令,后点运行。

- 在遇到不理解的信号或操作时,优先在《TEC4 模型计算机介绍》中使用control+F键进行查找。