- 1Paddlenlp之UIE模型实战实体抽取任务【打车数据、快递单】_uie模型的训练数据集

- 2从区块链到DAG(五)--DAG项目介绍IOTA和Obyte_the tangle popov, serguei

- 3【云计算与虚拟化】第二章 实验二 Vmware Workstation 15的使用

- 4解决文件传输难题:如何绕过Gitee的100MB上传限制_gitee在线上传单个文件最大 10m,本地推送单个文件最大 100m

- 5kafka消费信息时,产生重复消费的情况 - 20190121

- 6【AI大模型】在测试中的深度应用与实践案例_ai大模型在测试中的应用

- 7Python3.0学习笔记2_“*”可用于字符串的重复,下面选项正确的有

- 8spark中的cache和checkpoint_spark cache checkpoint

- 9C# list 成员对象是int型存在堆区还是栈区

- 10区块链技术之身份认证_区块链中的身份认证

转载:从底层结构开始学习FPGA(1)— 可配置逻辑块CLB(Configurable Logic Block)_clb模块

赞

踩

本文转载自CSDN博主「孤独的单刀」的原创文章,原文链接:https://blog.csdn.net/wuzhikaidetb/article/details/125175418

一、CLB概述

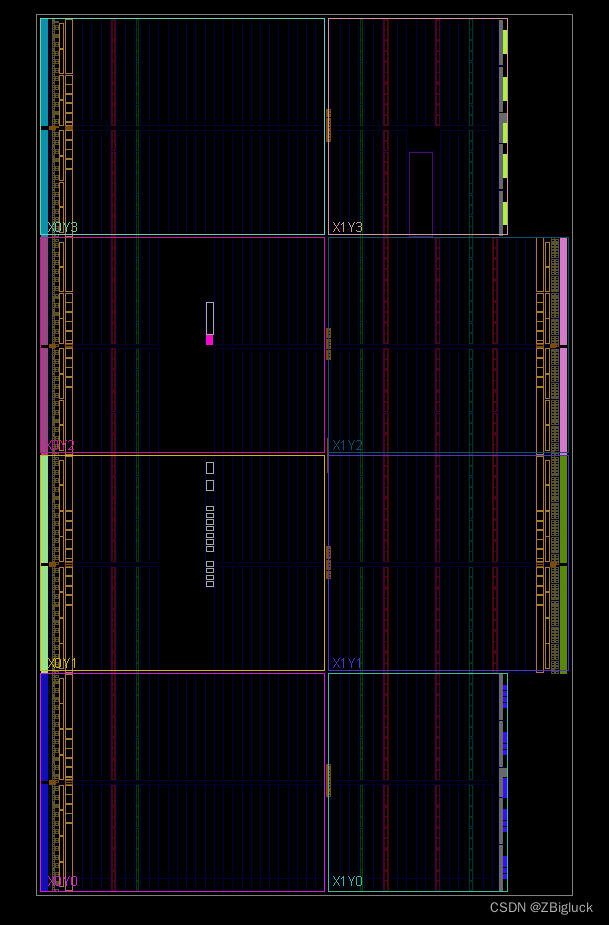

我们可以用 vivado 打开一个器件的 device 视图:

可以看到这些花里胡哨的五颜六色就分别代表了 FPGA 的底层硬件单元,主要有:可编程输入输出单元(IOB)、可编程逻辑单元(CLB)、时钟管理单元(MMCM/PLL)、BRAM、布线资源、内嵌的底层功能单元和内嵌专用硬件模块。其中最为主要的是可编程输出输出单元(IOB)、可编程逻辑单元(CLB)和布线资源。

而我们今天的主角可编程逻辑单元 CLB 则在上图中蓝色的若隐若现的位置,我们需要把它放大才能更好地观察:

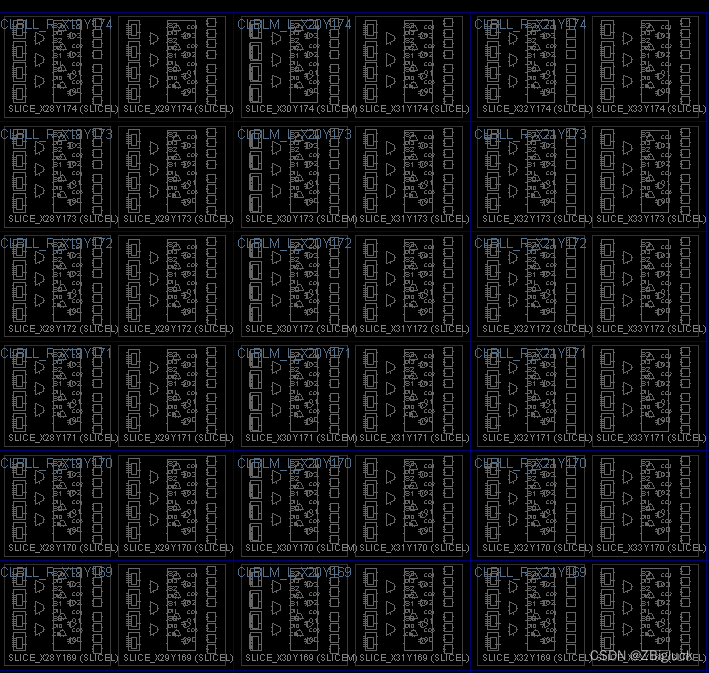

蓝色框中的就是 CLB ,同时也可以发现,CLB 是由两种不同的元素组成,这个元素我们称之为 SLICE 。

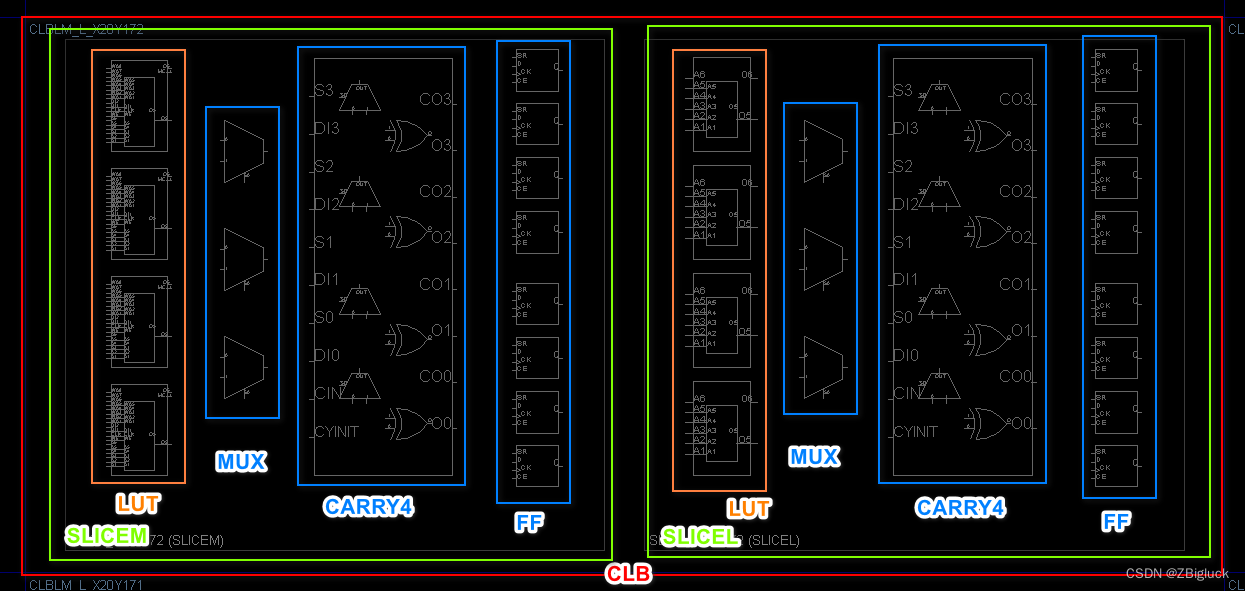

如果把 FPGA 实现的电路看做是积木拼成的摩天大楼,那么 CLB 就是实现大楼的最基本元素 — 砖块。 但是我们盖楼不可能只使用一种砖块,同样的为了实现各种功能的电路,我们也要把 CLB 切成了更小的块以便灵活组合实现更复杂的电路。

所以,CLB 实际上是四种基本元素的集合 —— 查找表LUT、进位链CARRY4、多路选择器Multiplexer以及存储单元FF。有了这四种基本元素后,我们就可以灵活组合实现各种时序逻辑和组合逻辑了。

二、SLICEM与SLICEL

一个 CLB 是由2个 SLICE 组成的,SLICE 根据其中的 LUT6 能实现的功能可以分为以下两种:

SLICEM(M:Memory):其内部的 LUT 可以读也可以写,可以实现移位寄存器和 DRAM 等存储功能,还可以实现基本的查找表逻辑

SLICEL(L:Logic): 其内部的LUT只可以读,只能实现基本的查找表逻辑

CLB 的组成可以是上图的1个 SLICEM + 1个 SLICEL ,或者是2个 SLICEL ,但是不会是2个 SLICEM 。一般情况下,CLB 中比例 SLICEL : SLICEM = 2 : 1。

总结一下:1个 CLB = 2个 SLICE = 2 × ( 4个 LUT + 3个 MUX + 1个 CARRY4 + 8个 FF ),这就是CLB和SLICE的架构了。

三、查找表LUT

查找表(Look-up Table),本质上就是1个6输入,64深度的 ROM ( SLICEM 中的则是 RAM,因为可读)。通过将所有结果保存在其内部,使用时通过由输入构建的地址线对其进行查找,从而实现6输入的函数逻辑。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/码创造者/article/detail/762291

Copyright © 2003-2013 www.wpsshop.cn 版权所有,并保留所有权利。