- 1手把手教你创建自己的 GPTs,打造专属的 AI 聊天机器人_创建自己的gpt,对话启动器怎么填

- 2域内渗透基本技巧

- 3【论文阅读笔记】A modified YOLOv5 for object detection inUAV-captured scenarios_drone-yolo论文

- 4进阶高工必备技能:Android插件化技术全解析!(附项目实战+视频分享)_android 插件化

- 5docker构建镜像方式--2--docker-maven-plugin 插件 ,远程连接docker服务器,一键快速生成镜像 【个人不推荐】

- 6【开源物联网】MQTT物联网网关Broker与Java开源实现_mqtt物联网协议java实现

- 7Kafka 2.5.0发布——弃用对Scala2.11的支持_kafka scala 2.11和2.13

- 8pytorch安装_pytorch install

- 9微信公众号开发之生成并扫描带参数的二维码_微信 showqrcode

- 10小米微信与电脑连接到服务器,小米微信多开文件怎么上传电脑

华为机考题库2024校园招聘-硬件通用/单板开发题库/-----(部分题目分享,完整版带答案,共十二套)_华为24硬件实习机考

赞

踩

部分题目分享,完整版带答案(有答案和解析,答案非官方,未仔细校正,仅供参考)

获取(QQ:453498735,加我备注:CSDN硬件单板题目,谢绝白嫖哈,知识付费)

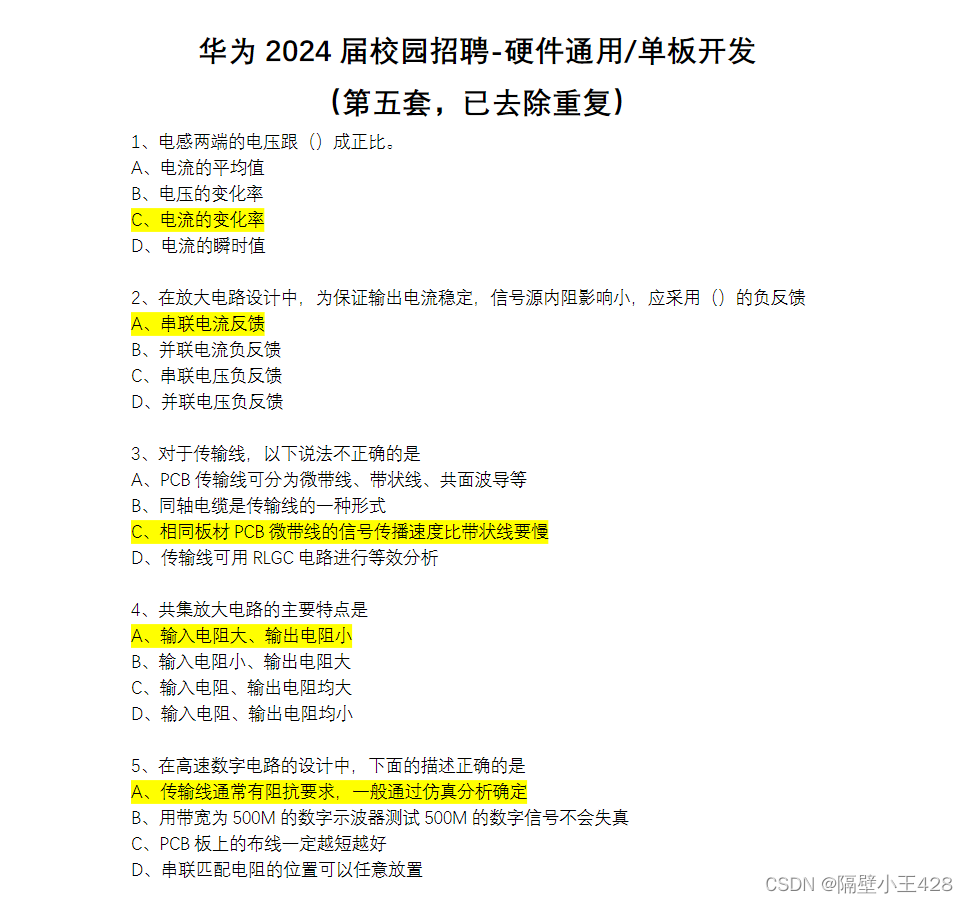

华为 2024 届校园招聘-硬件通用/单板开发

1、I2 C 总线的“START”信号是:

A. SCL 电平为低,SDA 电平由低变高

B. SCL 电平为低,SDA 电平由高到低

C. SCL 电平为高,SDA 电平有低变高

D. SCL 电平为高,SDA 电平由高到低

答案:D

解析: I2C 属于两线式串行总线,由⻜利浦公司开发用于微控制器(MCU)和外围设备(从

设备)进行通信的一种总线,属于一主多从(一个主设备(Master),多个从设备(Slave))的总线

结构,总线上的每个设备都有一个特定的设备地址,以区分同一 I2 C 总线上的其他设备。 物

理 I2 C 接口有两根双向线,串行时钟线(SCL)和串行数据线(SDA)组成,可用于发送和接

收数据,但是通信都是由主设备发起,从设备被动响应,实现数据的传输。

I2C 总线协议无非就是几样东⻄:起始信号、停止信号、应答信号、以及数据有效性。

空闲状态:SCL 和 SDSA 接上拉电阻,默认高电平

从设备地址来区分总线上不同的从设备,一般会在最低位加上读/写信号,一般对应 0/1

起始 START 信号:起始信号由主设备发起,SCL 保持高电平,SDA 由高到低

停止 STOP 信号:也由主设备终止,SCL 为高,SDA 由低到高

数据有效性:I2 C 总线进行数据传送时,在 SCL 的每个时钟脉冲期间传输一个数据位,

时钟信号 SCL 为高电平期间,数据线 SDA 上的数据必须保持稳定,只有在时钟线 SCL 上的

信号为低电平期间,数据线 SDA 上的高电平或低电平状态才允许变化,因为当 SCL 是高电

平时,数据线 SDA 的变化被规定为控制命令(START 或 STOP,也就是前面的起始信号和停

止信号)。

应答信号:接收端收到有效数据后向对方响应的信号,发送端每发送一个字节(8 位)数

据,在第 9 个时钟周期释放数据线去接收对方的应答。 当 SDA 是低电平为有效应答(ACK),

表示对方接收成功; 当 SDA 是高电平为无效应答(NACK),表示对方没有接收成功。

2、关于 CPU 和 I/O 设备之间的数据传送,下面说法正确的是:

A. 在中断方式和 DMA 方式下,CPU 都可以与 I/O 设备同步工作

B. 在中断方式下,CPU 需要执行程序来完成数据传送

C. 快速 I/O 设备更适合采用中断方式传送数据

D. 当 CPU 同时收到 DMA 请求和中断请求时,CPU 优先响应 DMA 请求

答案:D

A:中断方式下 CPU 无法和 I/O 设备同步工作;

B:中断时 CPU 需要停止程序的执行;

C:快速 I/O 设备更适合 DMA,例如磁盘存储等,而低速复杂的 I/O 适合中断比如打印机;

D:CPU 必须以更短的时间隔离查询并响应 DMA 请求。响应中断请求是在每条指令执行周

期结束的时刻,而响应 DMA 请求是在存取周期结束时刻。故选 D

解析: CPU 和 I/O 设备之间的数据传输主要分为以下三种:

程序查询方式:

在执行输入或输出前,要先查询相应设备的状态,当输入设备处于准备好状态,输出设备处

于空闲状态时,CPU 才执行输入/输出指令与外设交换信息。为此,接口电路中既要有数据

端口,还要有状态端口。

优点:控制简单,无需额外的硬件支出;

缺点:CPU 和外设之间只能串行工作,而 CPU 的速度比外设的速度快很多,CPU 将花费大

量时间都处于等待、空闲状态,使系统效率大大降低。

程序中断方式:

CPU 和外设之间只能串行工作,而 CPU 的速度比外设的速度快很多,CPU 将花费大量时间

都处于等待、空闲状态,使系统效率大大降低。当产生中断请求后,用程序方式有选择地封

锁部分中断,而允许其余中断仍然得到响应,称为中断屏蔽。 每个中断源设置一个中断屏

蔽触发器来屏蔽该设备的中断请求。将该位置 1,屏蔽该中断源的请求;为 0 则响应。通过

中断屏蔽字可以重新设定中断优级。

中断处理过程:中断请求、中断响应、保护现场、执行中断服务子程序、恢复现场、中断返

回。

中断响应条件:①外设提出中断申请;②本中断位未被屏蔽;③本中断优先级最高;④ CPU

允许中断。

原则:当到来的中断优先级高于正在处理的中断时,优先处理新到来的优先级更高的中断。

DMA 控制方式:

DMA 是指外部设备不通过 CPU 而直接与系统内存交换数据的接口技术。这样数据的传送速

度就取决于存储器和外设的工作速度。

通常系统总线是由 CPU 管理的,在 DMA 方式时,就希望 CPU 把这些总线让出来,即 CPU

连到这些总线上的线处于第三态(高阻状态),而由 DMA 控制器接管,控制传送的字节数,

判断 DMA 是否结束,以及发出 DMA 结束信号。

3、3、电容容值稳定性由高到低排序正确的是()

A. Y5V\NPO\X7R\X5R

B. X7R\X5R\Y5V\NPO

C. NPO\X7R\X5R\Y5V

D. X7R\NPO\X5R\Y5V

解析:C

NPO 属于I类陶瓷,而其他的 X7R、X5R、Y5V、Z5U 等都属于II类陶瓷。

I类陶瓷电容器(ClassIceramic capacitor),过去称高频陶瓷电容器(High-frequency

ceramic capacitor),介质采用非铁电(顺电)配方,以 TiO2 为主要成分(介电常数小于 150),

因此具有最稳定的性能;特别适用于振荡器、谐振回路、高频电路中的耦合电容,以及其他

要求损耗小和电容量稳定的电路,或用于温度补偿。

II类陶瓷电容器(Class II ceramic capacitor)过去称为为低频陶瓷电容器(Low frequency

ceramic capacitor),指用铁电陶瓷作介质的电容器,因此也称铁电陶瓷电容器。这类电容器

的比电容大,电容量随温度呈非线性变化,损耗较大,常在电子设备中用于旁路、耦合或用

于其它对损耗和电容量稳定性要求不高的电路中。其中II类陶瓷电容器又分为稳定级和可用

级。X5R、X7R 属于II类陶瓷的稳定级,而 Y5V 和 Z5U 属于可用级。

4、GPIO 一般要求给定态,不要随意配置为 NP,但是以下哪种场景一般都是不能配置为 PD

的?

A. 用作输出,负载端默认是高阻态

B. 用作输入

C. 用作输出,负载端有下拉电阻,且默认时使能的

D. 用作输出,负载端有上拉电阻,且默认时使能的

解析:D

GPIO,general purpose input output 具有多种模式,每个 GPIO 都有单独的时钟开关,每使

用到一个 GPIO 都要对其时钟使能,而且 STM32 的 GPIO 的输入输出必须单独配置。

GPIO 配置一般分为:高阻抗(Hi-Z),上拉(PULL-UP),下拉(PULL-DOWN)。

在 pull-up resistor(pull-up 外接高电压,pull-down 通常会接地)的作用之下,让 port 的维持

在明确的高电压状态(pull-down 则是让 port 维持在低电压状态)。

输入上拉(Pull up):即输入端口配置一个电阻接到电源(Power)端,该电阻可以使用芯片

内置,也可以是外部电阻。

输入下拉(Pull down):即输入端口配置一个电阻到地(Ground),该电阻可以使用芯片内

置,也可以是外部电阻。

上拉(Pull Up)是对器件注入电流,下拉(Pull down)是输出电流。因此在 GPIO 配置为 PD

时,已经默认电位为 0,如果再接上有上拉电阻的负载端,那么将形成回路无法正确的识别

信号。

5、光耦隔离的驱动器的优点是

A. 不需承受主电路高压

B.不需增加额外电源

C. 电磁干扰小

D.有时需增加脉冲电流放大器

解析:光耦合器是利用光在两个隔离电路之间传输电信号的电子元件,它们可防止高电

压影响接收信号的电路。它们由 LED 和光电晶体管组成,采用各种封装。

光耦合器的主要优点是:信号单向传输,输入端与输出端完全实现了电气隔离,输出信

号对输入端无影响,抗干扰能力强,工作稳定,无触点,使用寿命⻓,传输效率高。

将发光元件和受光元件组合在一起,通过电-光-电这种转换,利用“光”这一环节完成隔

离功能,使输入和输出在电气上是完全隔离的。根据受光元件的不同可分为晶体管输出型和

晶闸管输出型两类。 光电耦合器具有三个特点:①信号传递采取电-光-电的形式,发光部

分和受光部分不接触,能够避免输出端对输入端可能产生的反馈和干扰,②抑制噪声干扰能

力强;③具有耐用、可靠性高和速度快等优点,响应时间一般为数 以内,高速型光电耦合

器的响应时间有的甚至小于 10ns。

6、用示波器在产品板上在线测试(信号没有断开)一路 3.125Gbps 的高速串行信号,需要

选择的探头是

A. 50 欧无源探头

B. 不需要探头,直接用 50 欧同轴线连接

C. 高带宽高阻探头

解析:C

无源探头细分:低阻电阻分压探头、带补偿的高阻无源探头(最常用的无源探头)、高压探头。

有源探头:单端有源探头、差分探头、电流探头。 由于有源探头里包含了类似晶体管和放

大器的有源部件,需要供电支持,因此称作有源探头。最常⻅的情况下,有源设备是一种场

效应晶体管(PET),它提供了非常低的输入电容,低电容会在更宽的频段上导致高输入阻抗。

有源 FET 探头的规定带宽一般在 500MHz ~4GHz 之间。除带宽更高外,有源 FET 探头的高

输入阻抗允许在阻抗未知的测试点上进行测量,而产生负荷效应的⻛险要低得多。另外,由

于低电容降低了地线影响,可以使用更⻓的地线。有源 FET 探头没有无源探头的电压范围。

有源探头的线性动态范围一般在±0.6V 到±10V 之间。

有的示波器会支持 50 Ω or 1 MΩ 输入阻抗切换。但对于大多数的测量,1 MΩ 是最最常⻅

的。50 Ω 的输入阻抗往往被用于测量高速信号,比如微波。还有逻辑电路中的信号传输延

迟和电路板阻抗测量等。

因为高速串行信号的频率比较高,需要探头具有较高的带宽才能保证信号的完整性和准确

性。同时,由于高速信号的阻抗通常比较高(例如 100 欧姆或以上),因此高阻探头比较适

合测量这种类型的信号。50 欧无源探头和 50 欧同轴线连接探头适用于测量低频或中频信

号,对于高速串行信号的测量来说,它们的带宽可能不足以支持信号的完整性和准确性。

7、网口物理层芯片与变压器相连时,后者的抽头必须通过电容下拉

A. 错误

B. 正确

解析:A

我们首先看配比的是什么芯片,不同的芯片设计有不同的接法,主要是看 PHY 芯片 UTP 口

驱动类型是什么,电压驱动的我们的网络变压器芯片侧中心抽头就要接电源(3.3V,2.5V,1.8V

都有);电流驱动的网络变压器芯片侧中心抽头就直接接个电容到地即可!

(但是按照我的理解应该是 A,题目描述的有点绝对?)这个说法是正确的。在将网口物理

层芯片与变压器相连时,需要在变压器的抽头(CT)和地之间串联一个电容,并将电容连接

到地,这被称为“CT 下拉电容”。 这是因为网口物理层芯片和变压器之间的连接构成了一个

电路环路,如果没有 CT 下拉电容,就会形成一个巨大的环路电感,会导致共模噪声的出现,

从而影响网络传输的性能和稳定性。CT 下拉电容的作用是将环路电感的影响降到最低,减

少共模噪声的干扰。 需要注意的是,CT 下拉电容的大小和类型需要根据具体的应用场景和

电路要求进行选择和设计。如果电容的容值过大或过小,都可能影响网络传输的性能和稳定性。因此,在设计和选择 CT 下拉电容时需要进行充分的分析和测试。