- 1hadoopdataplatform_hadoop大数据平台安全基础知识入门

- 2Qt中出现中文乱码的原因以及解决方法_qt中文乱码解决方法

- 3git submodule命令_.git文件 submodule

- 4学习Spring Cloud第六课(将微服务注册到Eureka Server上)_微服务192.168.153.1

- 5处理3D数据的强大工具 CloudCompare (多平台兼容)_cloud compare 出图

- 6详情!安全运维工程师怎么考?报考难度大吗?证书含金量高吗?_安全运维工程师证书

- 7数据结构—树(自学笔记)(郝斌)_树的每个结点有且仅有一个父节

- 8python 文件读写操作总结_python文件读写实验总结

- 9Unity C# 之 使用 HttpWebRequest 基础知识/HttpWebRequest 进行异步Post 网络访问/数据流形式获取数据(Task/async/await)的代码简单实现_unitywebrequest 异步

- 10微信小程序开发 json配置文件详解导航栏设置 tabbar设置,主题颜色设置_在index.json中如何设置导航条

数字IC设计 - 数字IC实现途径_门海sea of gate 定义

赞

踩

概述

IC设计实现方式有很多种,模拟IC的实现方式主要包括:全定制与宏单元/IP。SoC的实现方式主要是依靠CPU/DSP/MCU/ASSP作为主控单元(用于系统处理控制)并搭配其它IP构成片上系统芯片。而数字IC实现发主要方式有以下几种。

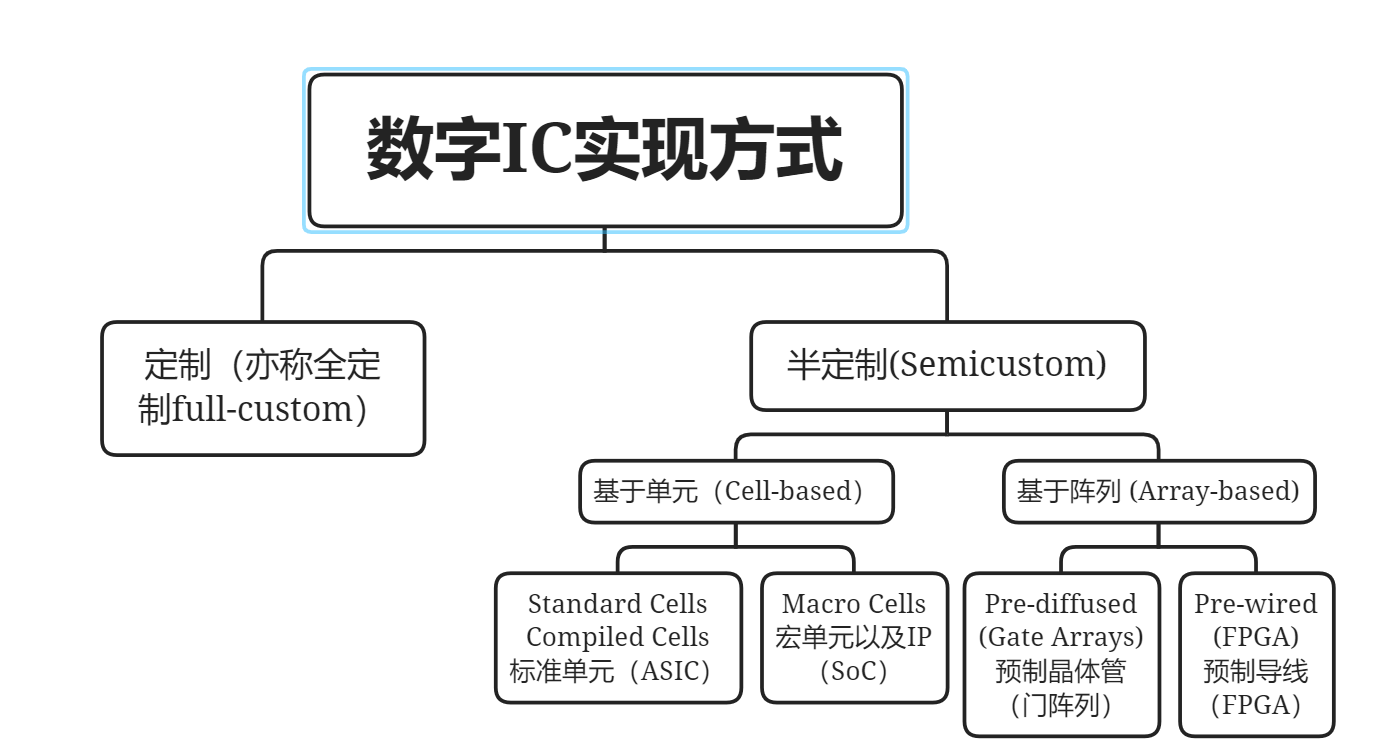

数字IC的实现方式

数字IC的实现方式分类如下图,

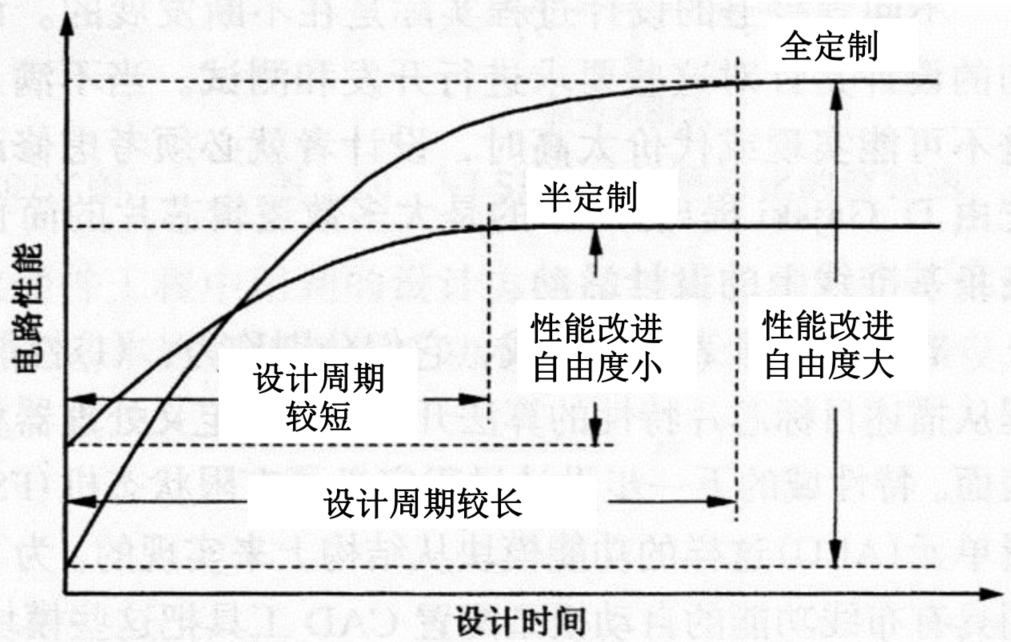

从大体上来说,数字IC可分为全定制和半定制。全定制的性能优化改进自由度更大,而半定制的设计研发的周期更短。

全定制

全定制的数字IC芯片,如字面意思,芯片内部的相关逻辑电路都需要进行人工设计定制,需要手工完成电路设计和物理设计。

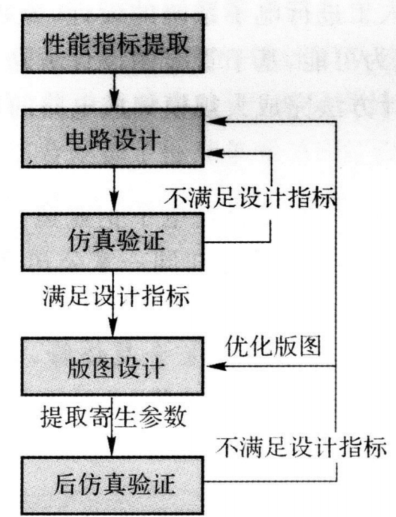

基本流程

全定制IC设计基本流程如下图所示,全定制设计数字IC芯片时,首先需要对性能指标进行提取分析,然后根据现有的性能指标进行电路设计,不断进行仿真验证,直到逻辑功能满足设计需求,然后可以进行版图设计以及验证的阶段,直到后仿真验证满足设计指标时,即可流片生产。

因此,针对上述全定制的设计流程,将主要使用工具进行辅助设计以下内容。

- 电路功能设计(Composer/S-Edit)

- 电路性能设计(HSpice, Spectre)

- 版图编辑(Virtuoso/L-edit)

- 版图验证(Diva, Dracula)

- 寄生参数提取(Star-RC)

- 电路后仿真( Dracula)

- 制板数据生成(Type out)

特点

全定制芯片可以做到底层最优化,也即

- 元器件层面: 可以将器件优化到最佳尺寸以获取最优性能。

- 拓扑结构层面:可以经过不断优化拓扑结构达到最佳布局从而获取符合要求指标的最小面积的芯片结构。

- 连线层面:可以通过优化找到最短路径设计,从而使芯片达到最快速度。

但是相比其他方式,全定制设计成本最高,且设计周期长;人力投入大;一次成功率低;设计复用性差;相对其他方式设计的自动化程度低;电路与版图规则性差,并且逻辑综合难以实现。

适用设计

针对全定制的设计特点,适用于进行以下设计:

- 绝大部分模拟电路:结构复杂而无规则

- 可复用模块:标准单元、库单元、具有重复性结构的单元(如ROM、RAM等)

- 对性能要求极高的单元:加速器、乘法器等

- 产量极大的标准电路:存储器、通用逻辑电路等, 成本~投片成本

- 不计开发成本与时间的设计:如超级计算机、巨型计算机

- 反向设计的芯片

半定制

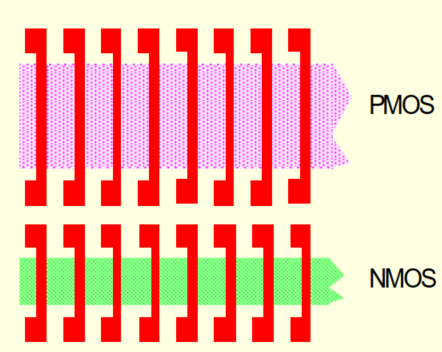

半定制方式主要又分为基于单元和基于阵列两个大类,基于单元的方式是将一个模块功能做成标准模块单元,然后在设计时调用成熟的标准单元进行互联设计功能。基于阵列的方式是将预制的晶体管或者导线做成阵列集成,然后在使用时更改晶体管或者导线的连接方式即可完成相关功能的设计。

标准单元/宏单元

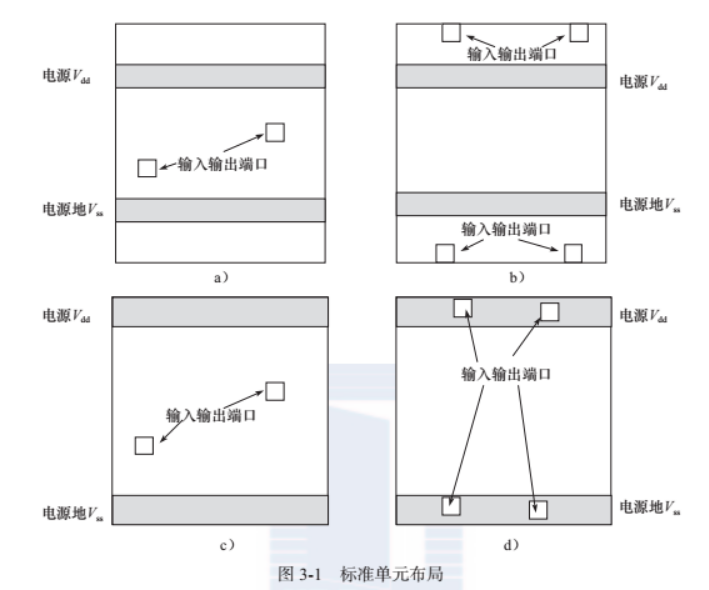

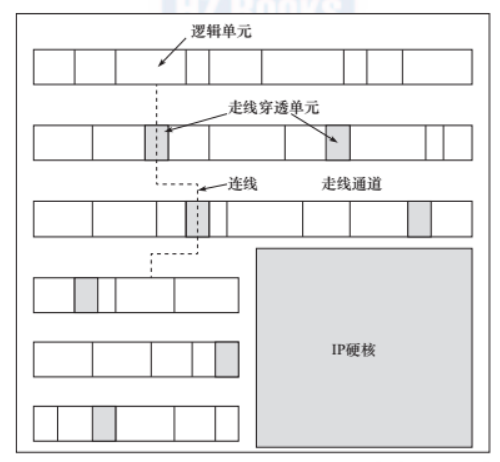

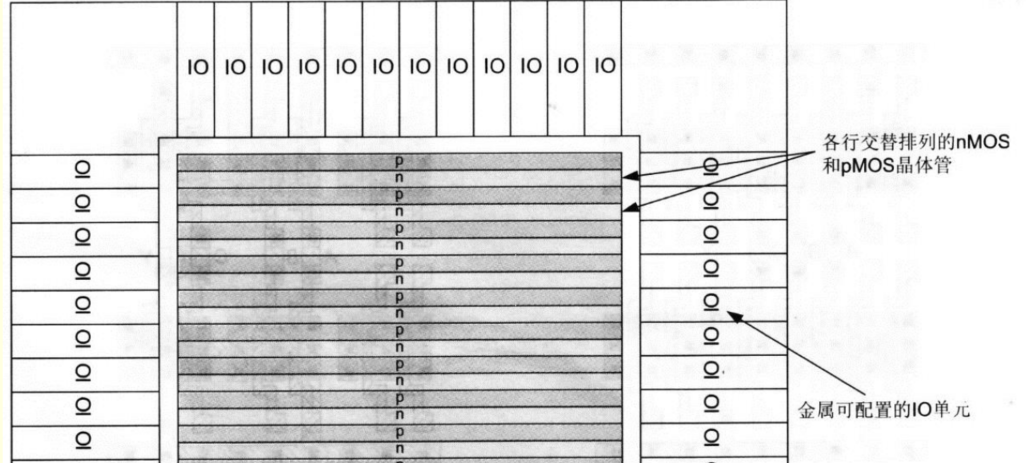

标准单元 (Standard Cell )法是库单元设计方法的一种,标准单元法的特点是各个单元高度相同宽度不等,单元宽度随单元功能的复杂程度而变,所有单元的电源线和地线位置相同,如图下所示。

将常用逻辑单元设计成等高不等宽(3: 1~1:3 不等)的标准单元,供设计者选用,标准单元行与布线通道行间隔排布,按网格实现规则化布线。

标准单元的设计有以下特点:

- 标准单元:等高不等宽

- Pad:可多可少

- 布线通道:可宽可窄

- 标准单元内部为全定制设计,与特定的工艺捆绑

- 不同的工艺有不同的标准单元库,标准单元的版图必须满足特定工艺的设计规则

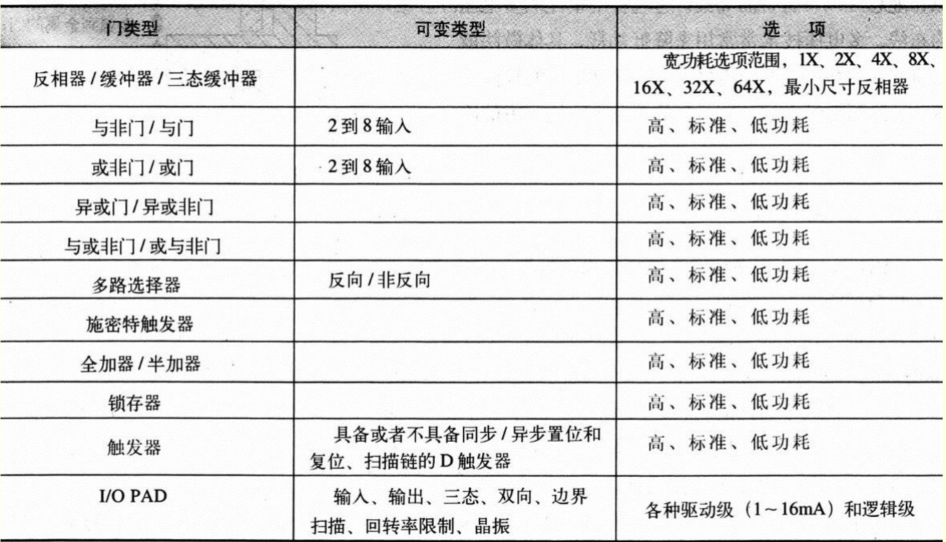

常见的标准单元库

使用标准单元优点与缺点

优点

- 面积利用率高于门阵列(可达到90%以上), 单元类型、数目、布线通道、 Pad数按需选用,设计合理可基本无冗余。

- 标准单元内部采用全定制设计, 底层性能优化程度高。

- 总体性能优化程度与经济性介于全定制和门阵列之间。

缺点

- 相对于门阵列而言,需全套掩模设计,故投片成本较高,生产周期较长。

- 依赖于单元库,不如全定制灵活,单元类型数目有限,建库工作量大。

- 依赖于EDA工具,能实现逻辑综合,但比门阵列相对难度大。

- 对寄生参数(互连寄生参数、负载系数、串扰等)的估计不如门阵列准确。

宏单元与标准单元区别

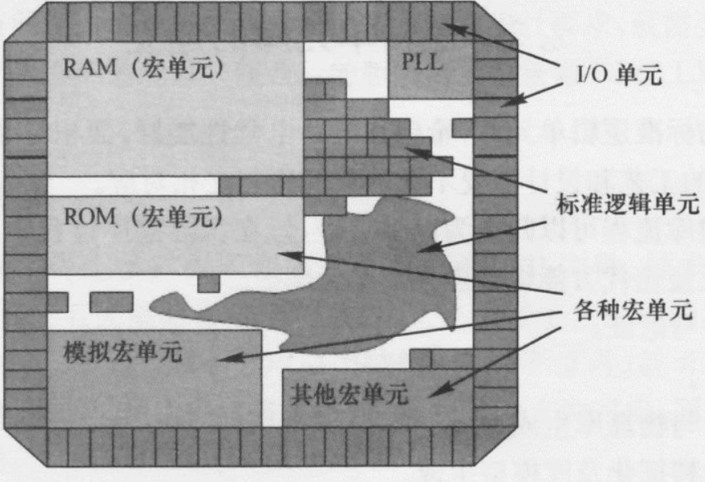

宏单元(macro block)也叫宏模块,相比标准单元,宏单元对单元的形状无限制。下图是一个SoC的典型布局,从图中可以看到不同型号的宏单元大小不一,分布在芯片的各个角落。

使用宏单元的优点与缺点

优点

- 面积利用率较标准单元法高,大约有25%。

- 性能优化程度高。

缺点

- 专用性强,通用性差

- 对单元库、 EDA综合、布线工具要求更高

宏单元设计的适用范围

- 嵌入式存储器,该类型也是最常见的宏单元设计。

- 模拟电路单元(运放、 ADC/DAC、 PLL、振荡器等)

- I/O单元

- SOC中的IP

- 标准单元难以甚至无法实现的其它电路单元

门阵列/门海

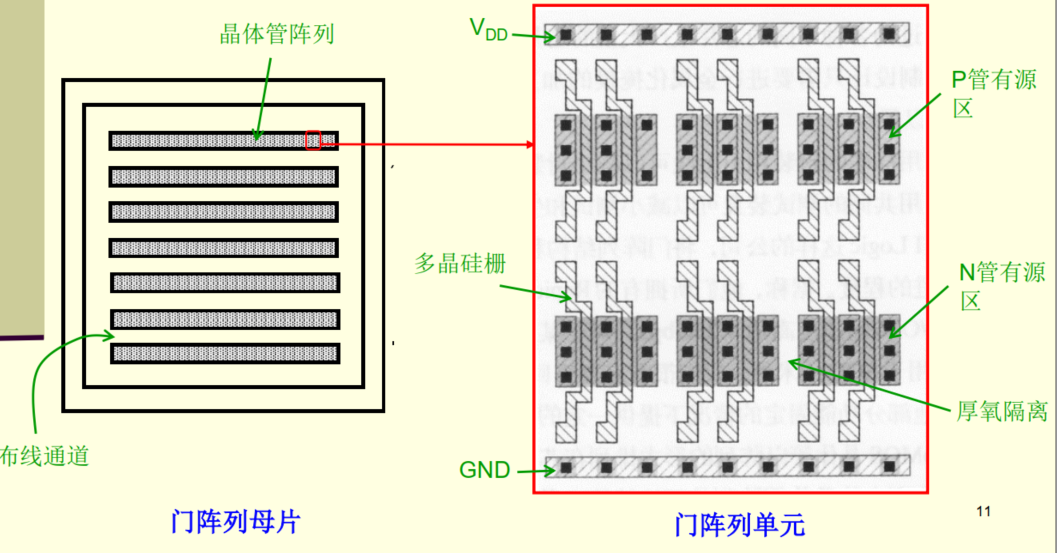

**门阵列(Gate Array)**是基于预制晶体管阵列的母片,设计者只需根据每种电路功能要求,设计管间的金属化互连和必要的通孔及接触孔即可。

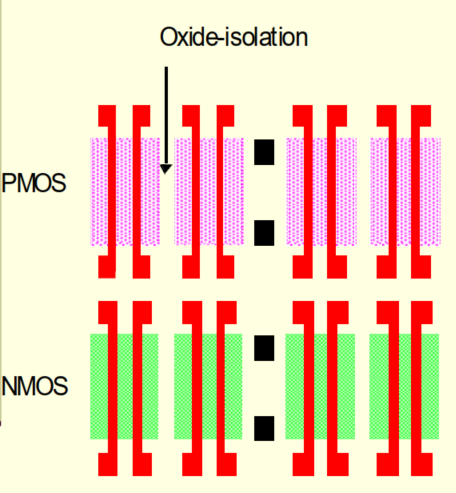

对于多层布线的IC,可取消与晶体管同层的布线通道,称为门海(Sea of Gate) 。

门阵列/门海的两种隔离方式

场氧隔离:用纵向厚氧和横向距离进行隔离,所占面积较大。

栅隔离:用截止CMOS单元(N管G->GND, P管G->VDD)进行隔离,所占面积较小。

门阵列/门海的优缺点

优点

- 设计周期短:约为全定制的50%,因为只需设计连线,无需设计晶体管。

- 投片成本低:母片通用,可大批量生产,只需追加与互连有关的掩模(金属化、接触孔、通孔等),成本降至全定制的1/4~1/8。

- 易于实现设计自动化:结构规则,对单元库和EDA工具要求较低。

缺点

- 芯片面积大:母片门数>实际需要门数,布线通道面积>实际需要布线面积,单元中有冗余管(如6管单元做2输入与非门,就有2管冗余),单元晶体管面积固定(通常取所需最大面积)。总体面积利用率为60~80%。

- 管脚数选择受限制:不适于内部单元少pad多以及内部单元多Pad少之电路。

- 底层优化程度低:所有门都用同种尺寸(最大面积)的晶体管构成,尺寸无从优化,延迟、负载能力等无法达到最佳。

可编程器件(预制导线)

现场可编程门阵列(FPGA, Field Programmable Gate Array),这个名词熟悉FPGA开发的人一定不陌生,但是该名词还可以进行进一步解读。

- 现场:在芯片应用现场,通过外部施加控制信号来改变芯片内部的编程关系。

- 可编程:用浮栅晶体管等方法控制阵列中晶体管的通断或连接。

- 门阵列:用与门阵列类似的晶体管阵列来实现逻辑运算

可编程逻辑阵列

可编程逻辑阵列 (PLA, Programmable Logic Array) :任何组合逻辑都能用积之和的形式表示,而积之和的功能可以用 “与” 阵列和 “或” 阵列的组合,或者 “或非” 阵列和 “或非” 的组合来实现。

PLA中,每个节点可以都设置一个晶体管,不过每个晶体管是生效(功能正常)还是失效(永久截止)可以通过外部干预(加大电流或高电压)改变,称之为“可编程”。 这种编程可以是一次性的,也可以是能修改的。同时,为了实现时序控制,必须在PLA阵列中加入时序控制元件(寄存器等) 。

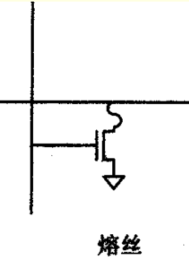

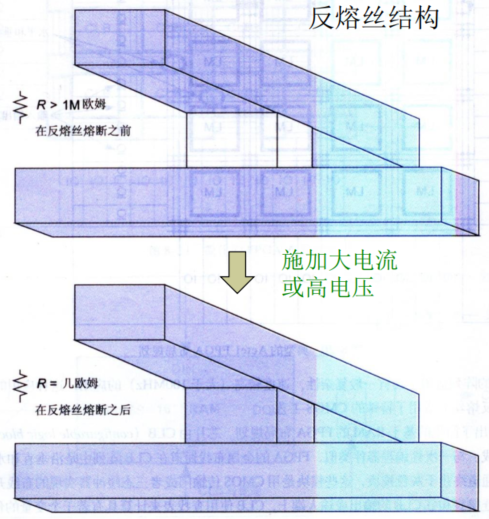

一次性编程

如果想实现一次性编程,将熔丝结构加电后开路,反熔丝结构加电后短路。因为编程资源(熔丝)占用面积小,导通电阻小,但只可编程一次,无法修改。

易失性编程

利用SRAM单元控制阵列中晶体管的通断,从而实现易失性编程 。采用标准CMOS工艺即可实现,但断电后无法保持(易失性),每次编

程需读入数据,工作时需定时刷新,编程器件占用面积较大。

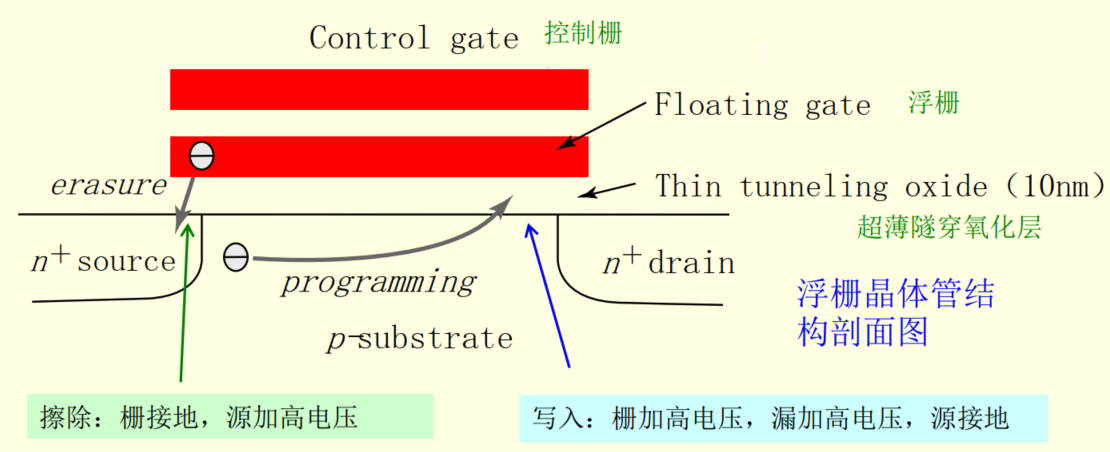

非易失性编程

基于浮栅晶体管实现的E2PROM或Flash编程可实现非易失性编程。断电后仍然保持(非易失性),可多次编程(通常10万次),但浮栅晶体管需特殊工艺制造,擦存储单元需高电压(通常>10V) 。

浮栅被注入电子后(阈值电压远高于正常值),晶体管在正常工作条件下总是处于截止状态;浮栅电子被排除之后,晶体管处于正常工作状态。

基于阵列的PLA的优缺点

优点

- 结构非常规则,寄生参数乃至相关的面积、速度、功耗易于精确估计。

- 实现能很好地映射为两层次逻辑的逻辑功能(如大扇入的有限状态机)时,效率很高。

缺点

- 用大阵列实现简单逻辑时会产生许多冗余项,造成面积的浪费,同时冗余节点的电容对电路的功耗、延迟有贡献。

- 实现大扇出逻辑或多层逻辑(如加法和乘法运算)时,效率很低。

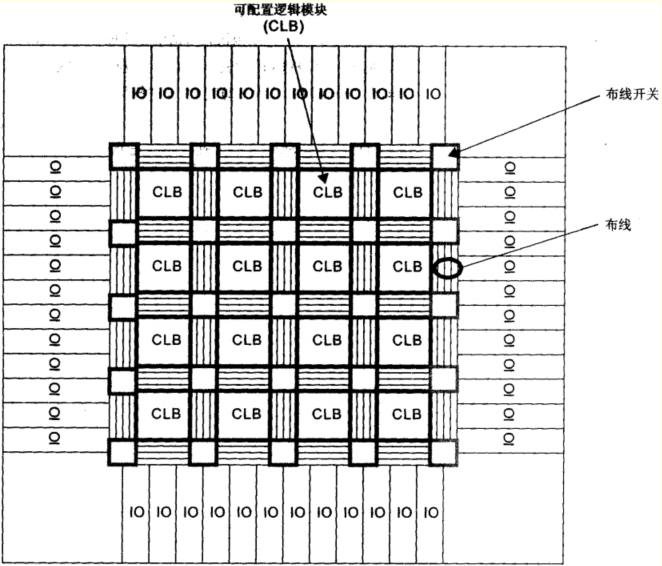

现场可编程门阵列FPGA

用基于单元的FPGA代替基于阵列的PLA,可解决PLA的弊端。

FPGA与传统PLA的区别

-

总体结构:基于单元,而非基于阵列

-

实现逻辑: 基于存储器,而非 “与”、“非”阵列

-

实现互连:基于可编程互连网格,而非阵列

FPGA内部依靠CLB(Configurable Logic Block)实现逻辑功能,CLB上电写入,支持反复编程,可以动态重构。

编程方式

- 反熔丝型:一次性编程

- SRAM型:易失,靠外加Flash保存编程信息,应用普遍

- Flash型:非易失,成本高

FPGA特点

优点

- 现场可编程,与芯片制造过程无关。

- 研发费用低,设计周期短,设计验证容易,大大降低了开发风险,因为无需制造掩膜和工艺投片。

- 一个芯片可实现多个功能,灵活性大。

- 版图规则,适合自动化设计,且非微电子人员易于设计。

缺点

- 单个芯片价格高,批量供货时成本高

- 性能难以充分优化,因为可编程消耗了资源,牺牲了面积、速度和功耗,在可比的条件下,性能与功耗比ASIC差10倍左右

数字IC实现方法的比较

综合角度

| 实现方法 | 一次工程开销 | 单位成本 | 功耗 | 实现复杂度 | 上市时间 | 性能 | 灵活度 |

|---|---|---|---|---|---|---|---|

| 基于微处理器 | 低 | 中等 | 高 | 低 | 短 | 低 | 高 |

| PLA | 低 | 中等 | 中等 | 低 | 短 | 中等 | 低 |

| FPGA | 低 | 高 | 中等 | 中等 | 短 | 中等 | 高 |

| 门阵列/门海 | 中等 | 中等 | 低 | 中等 | 中等 | 中等 | 中等 |

| 基于标准单元/宏单元 | 高 | 低 | 低 | 高 | 长 | 高 | 低 |

| 全定制设计 | 高 | 低 | 低 | 高 | 长 | 非常高 | 低 |

| 微处理器SoC设计 | 高 | 低 | 低 | 高 | 长 | 高 | 中等 |

设计角度

| 类型 | 版图设计法 | 器件编程法 | |||

|---|---|---|---|---|---|

| 实现方法 | 全定制 | 门阵列 | 标准单元 | 宏单元 | FPGA |

| 集成密度 | 高 | 中 | 中 | 高 | 低 |

| 灵活性 | 高 | 低 | 中 | 中 | 低(高) |

| 模拟 | 能 | 不能 | 不能 | 能 | 不能 |

| 性能 | 非常高 | 中 | 高 | 非常高 | 低 |

| 设计周期 | 长 | 中 | 中 | 中 | 短 |

| 设计成本 | 高 | 中 | 中 | 高 | 低 |

| 设计工具 | 非常复杂 | 复杂 | 复杂 | 复杂 | 简单 |

| 规模 | 大 | 中 | 大 | 大 | 小 |

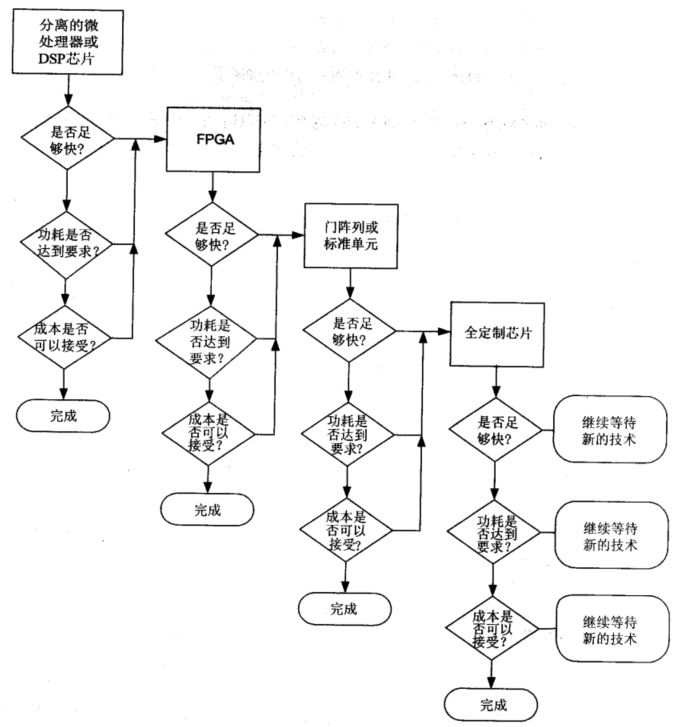

针对具体的选择,可以从以下几个方面进行考虑:速度、功耗、成本、灵活性。

小结

- 数字集成电路有全定制、门阵列、标准单元、可编程器件以及微处理器等多种实现方式,需根据性能要求、研发周期、经济性、灵活性等要求权衡选择。

- 对于大规模数字集成电路,除单元内部采用全定制之外,目前以标准单元和宏单元为主要实现方式。

- 如果重点考虑使用灵活性和研发周期而非性能与功耗的话,可以采用可编程器件甚至微处理器。

- 可编程器件常用于数字集成电路的硬件仿真工具,而嵌入式微处理器是系统芯片的核心IP。

reference

- 数字集成系统设计课程资料