热门标签

热门文章

- 1uboot代码分析_uboot 源码分析

- 2windows下使用ngrok让本地flask服务外网可访问_flask 发布到网上别人可以访问

- 3#if defined 宏定义常用“与”、“或”、“非”判断_ifdef判断两个宏

- 4github搭建博客_怎么搭建github

- 5总结:Prometheus长期存储方案_prometheus 存储

- 6496.下一个更大的元素

- 7分布式系统共识机制:一致性算法设计思想_分布式系统一致性设计

- 8【云计算学习教程】用户如何使用云服务产品?_云服务消费者从云服务提供商或者云服务代理商那里租赁云服务产品在合同期内和

- 9少年侠客【InsCode Stable Diffusion美图活动一期】_stable diffusion调参

- 10[论文笔记]LORA: LOW-RANK ADAPTATION OF LARGE LANGUAGE MODELS

当前位置: article > 正文

国产AGM fpga试用过程/型号:AGRV2KL48

作者:笔触狂放9 | 2024-05-24 01:40:23

赞

踩

agm fpga

#之前一直使用的是Xilinx的fpga,其他厂家的使用的很少,为此有意将之前在ZYNQ7020上的FPGA工程项目转移到国产AGM AGRV2KL48之上也是一次尝试#

#由于之前没接触过,因此先从入门闪烁灯开始#

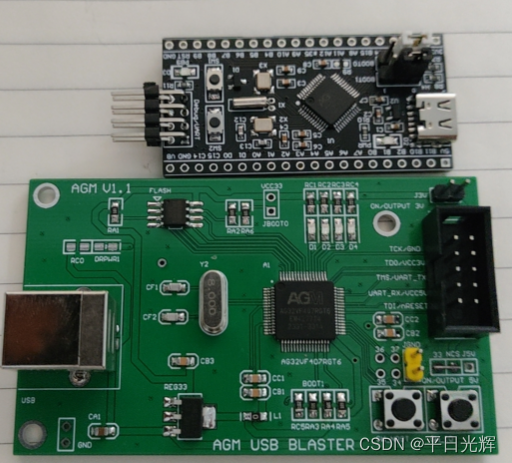

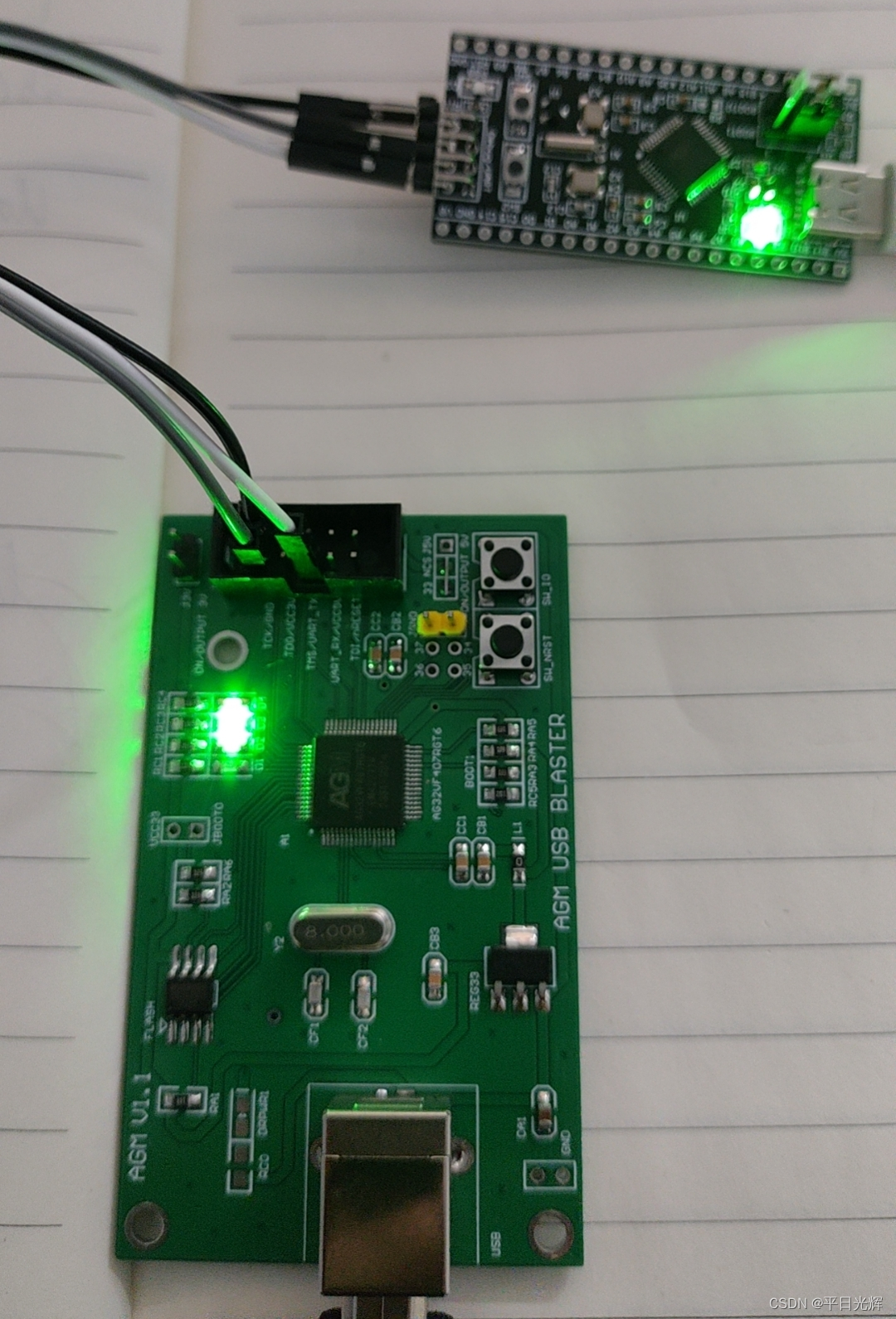

下载器以及测试板如下:

一、软件安装

此次用到的软件如下图所示:Quartus、Supra安装流程可以去AGM官网找到

![]()

二、生成项目

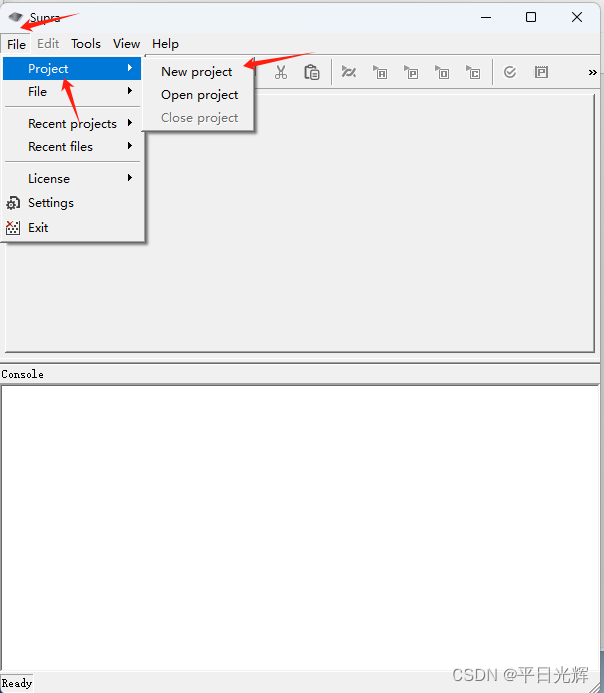

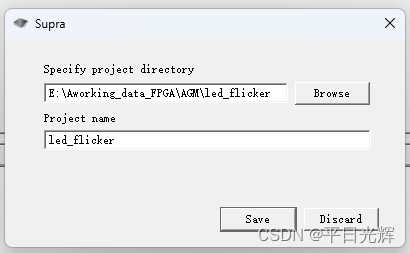

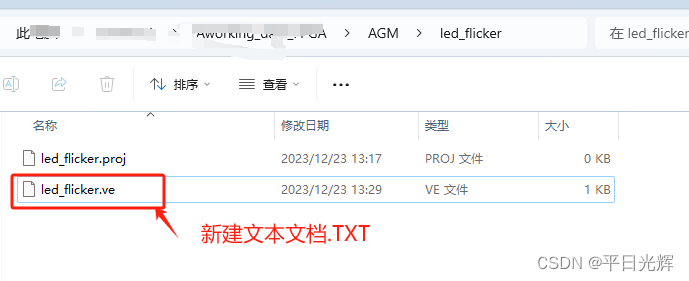

1、打开刚刚安装好的Supra:File-Pro-New Pro新建工程

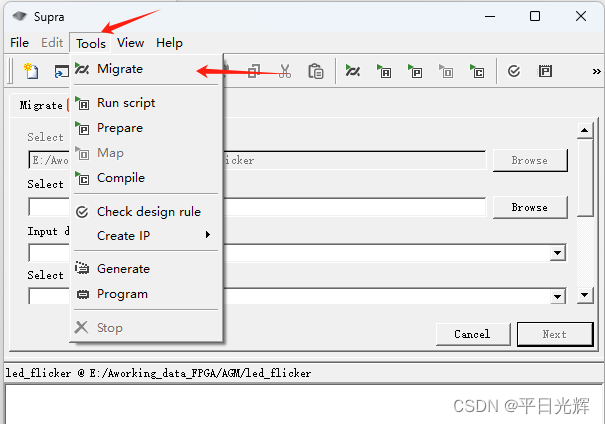

2、Tools-Migrate输入设计信息

我这里输入设计名称、芯片型号AGRV2KL48

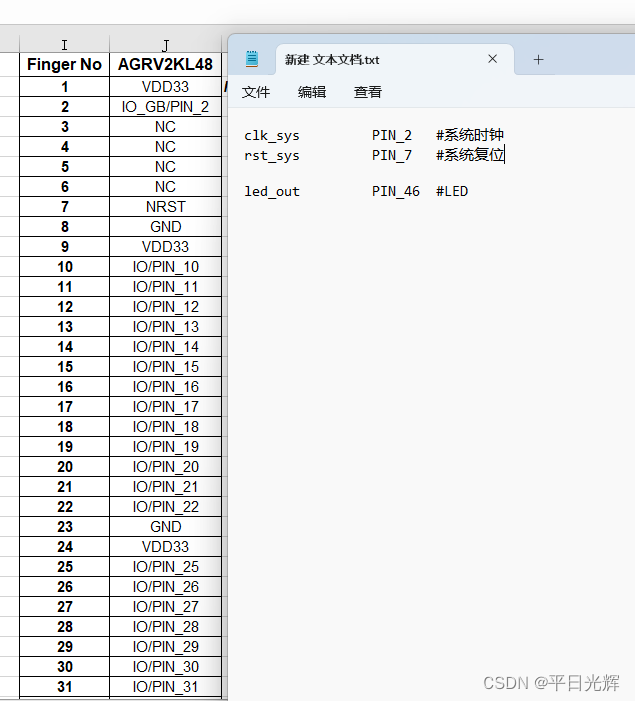

接下来需要选择一个ve文件,这个ve文件为IO的管脚位置设置文件,这个文件可以用txt文本编辑后更改为ve文件即可,如下:

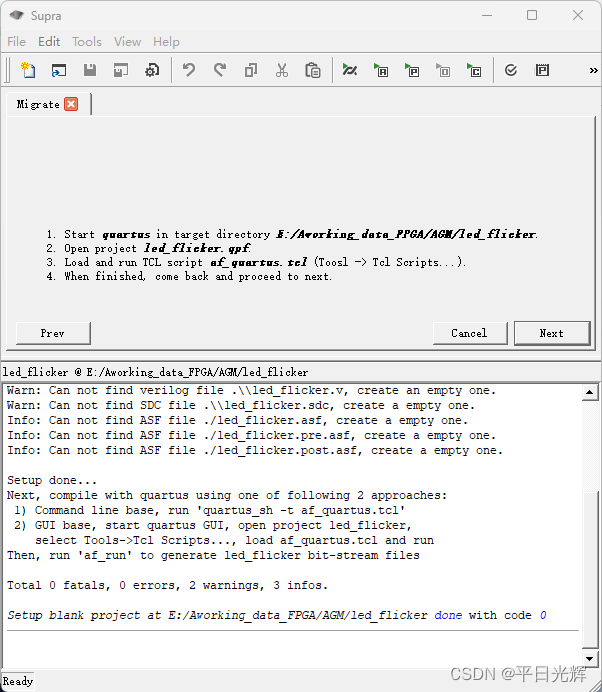

3、设计生成next

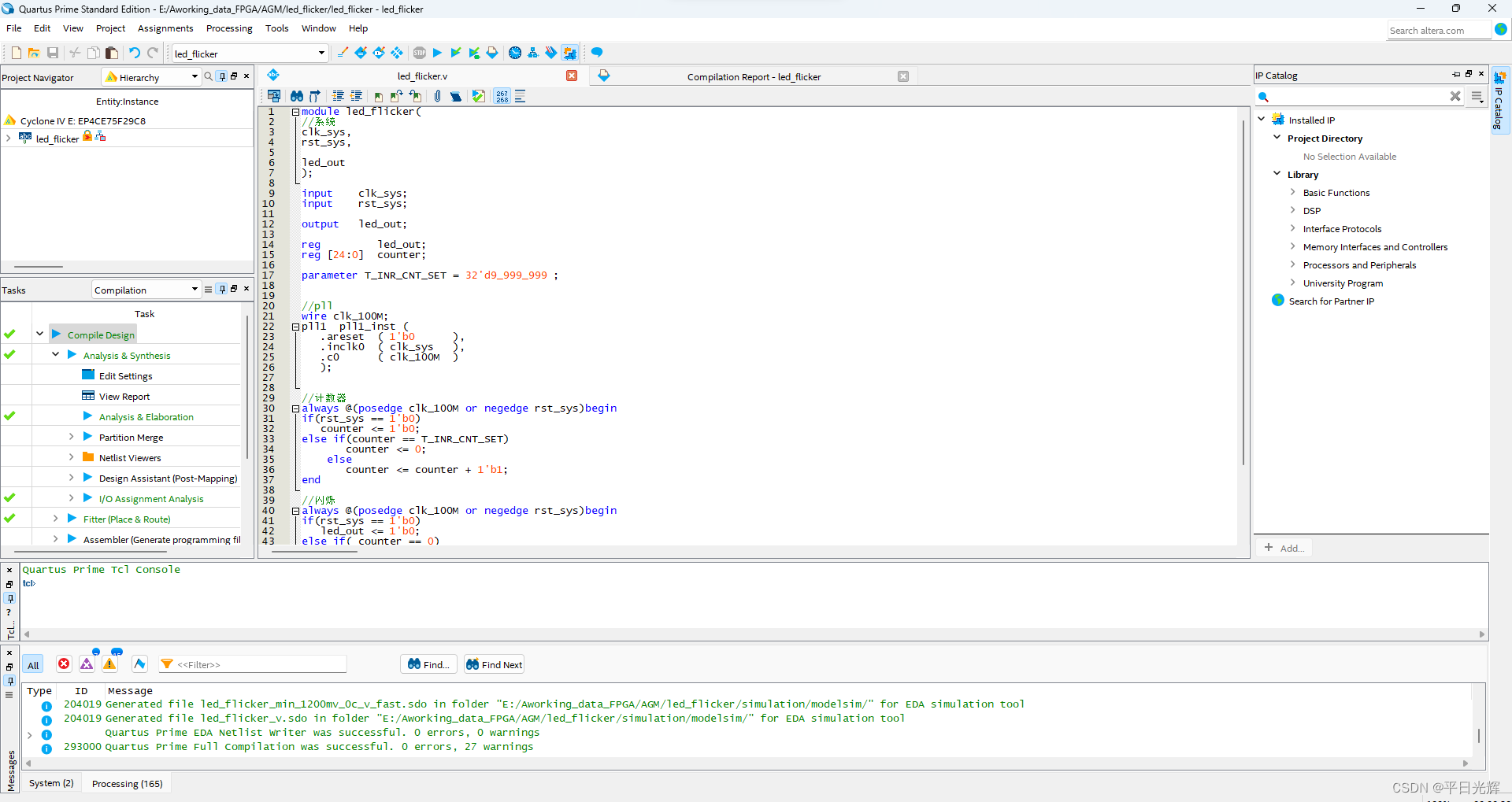

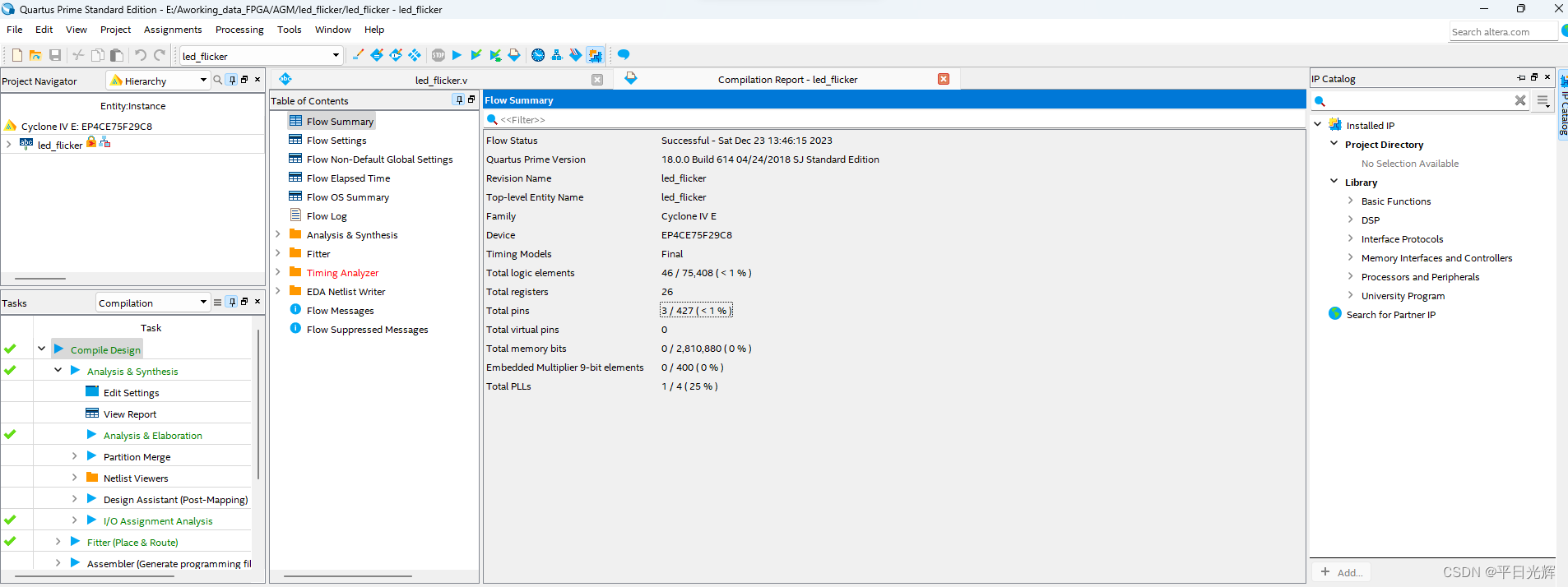

4、Quartus打开工程并设计

写入逻辑

编译成功后其逻辑数不能超过2K

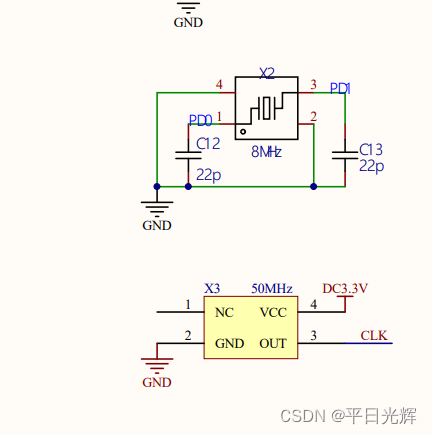

代码中用到了PLL的ip核,AGM的该型号支持PLLIP,其中关于pll的输入时钟,即系统时钟解释如下:(该款FPGA用了双晶振8M无源和50M有源,50M是纯cpld使用,8M无源是给内部纯mcu使用,其中PIN2引脚默认50MHz有源,这也是该芯片的一个优势)

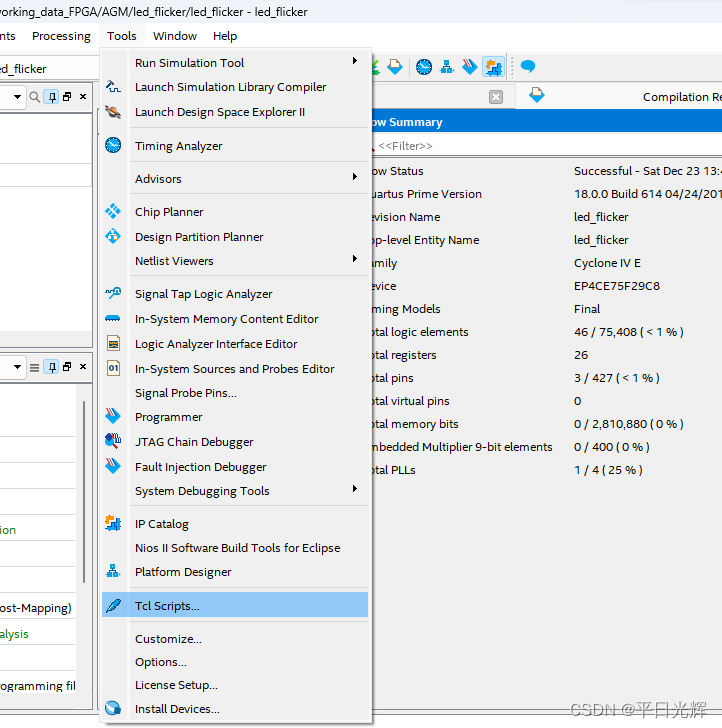

Tools-Tcl生成vo文件

选择af_quartus-run

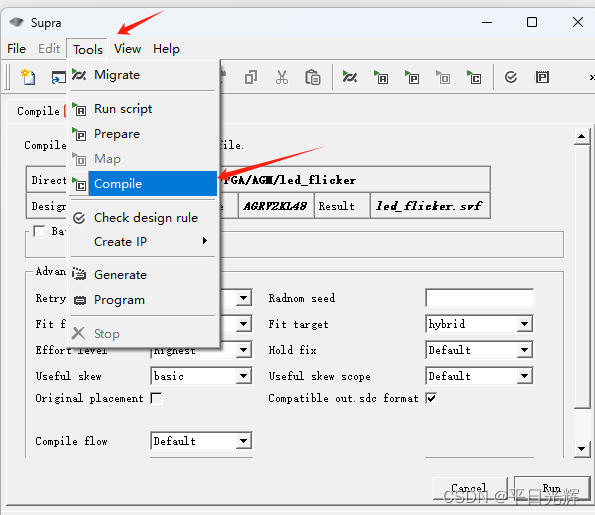

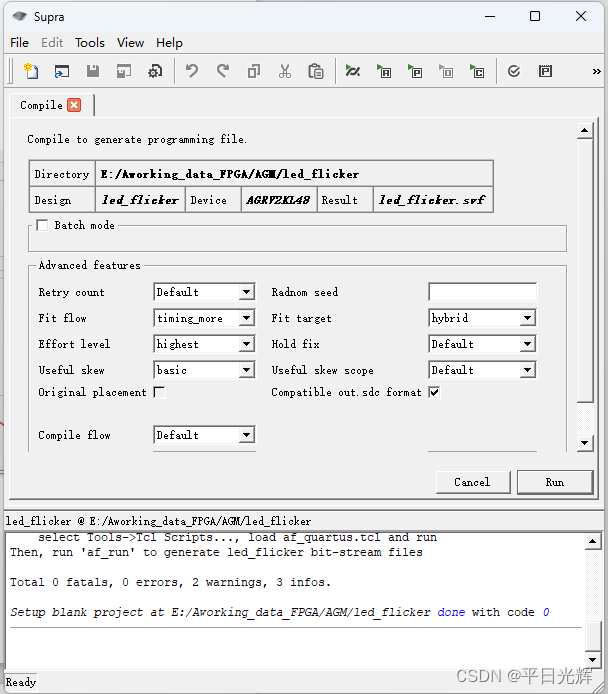

转到Supra生成bin文件Tools-Com

run

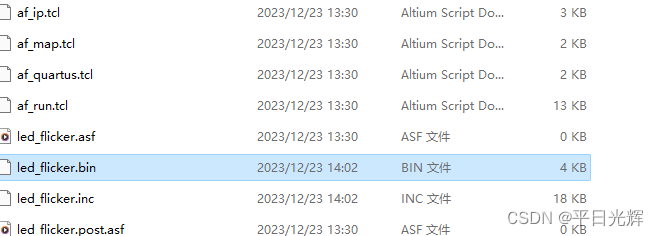

bin生成成功

三、下载

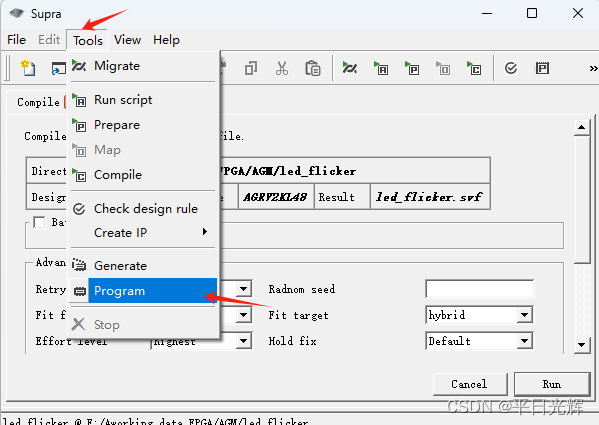

Tools-Pro

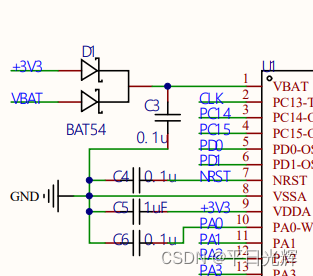

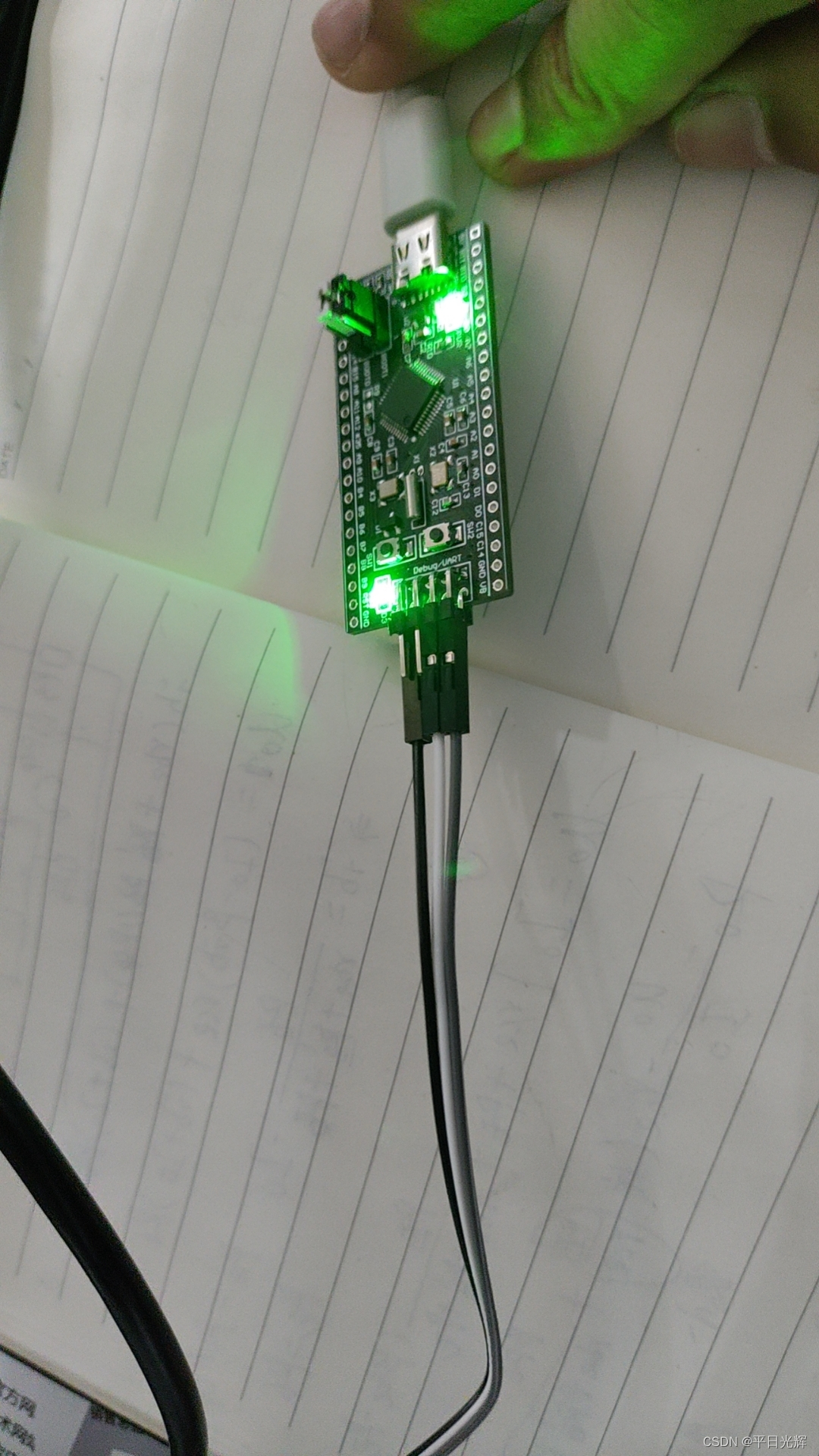

硬件连接(GND、TCK、TMS)

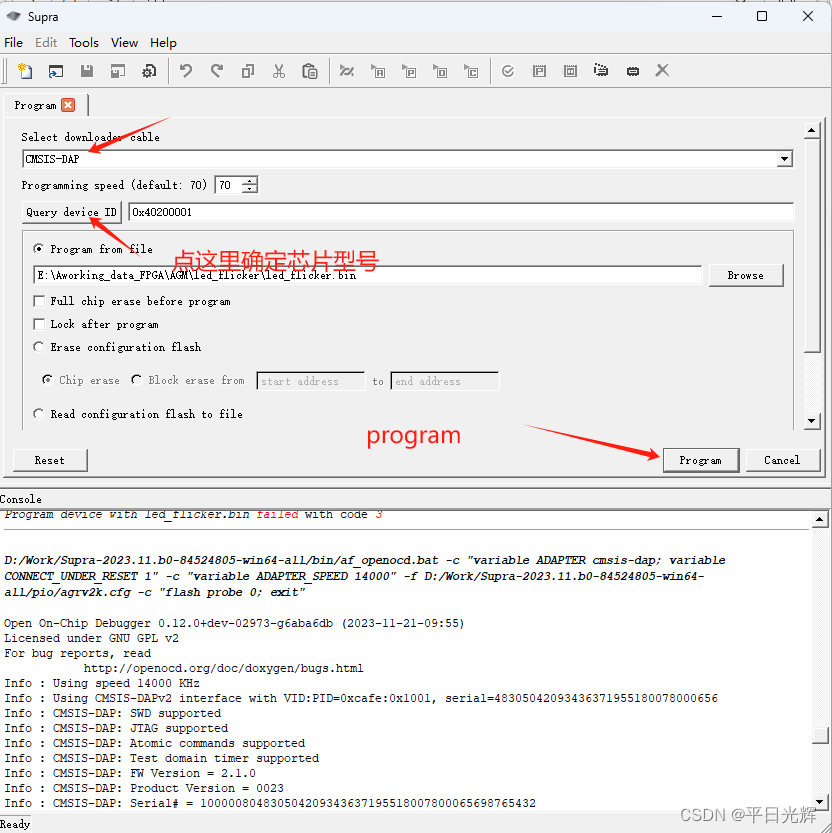

烧录方式选择CMSIS-DAP,Query device ID,program

OVer

之前逻辑的时候,把复位电平搞错了-OVER

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/615202

推荐阅读

相关标签