热门标签

热门文章

- 1程序员入门培训班多少钱?可以学到哪些东西?_程序员培训班要多少钱

- 2jwt 介绍_怎么查看一个浏览器网页的jwt

- 32021年危险化学品生产单位安全生产管理人员考试题库及危险化学品生产单位安全生产管理人员考试内容_人体是导体,在静电场中可能接触起电

- 4Vivado工程经验与时序收敛技巧_vivado fix cell

- 5算法——动态规划_完全加括号是什么意思

- 6git代码库迁移保留commit历史_Git 如何迁移仓库并保留 commit 记录

- 7RK3328 Debian安装OpenMediaVault

- 8git 拉取代码时显示Filename too long的解决办法_git file name too long

- 9系统盘50G,数据盘100G(需求:将数据磁盘扩容至1T)_系统盘和数据盘配比

- 10WooCommerce入门指南:简介

当前位置: article > 正文

FPGA控制AD7606_代码设计_ad7606 fpga代码

作者:笔触狂放9 | 2024-07-15 12:57:22

赞

踩

ad7606 fpga代码

前言

一、模块接口

用户接口主要是将读到的数据进行输出,AD7606接口则是上篇介绍的一些主要控制接口

module AD7606_drive#( parameter P_RANGE = 0 )( input i_clk ,//50MHz 1 cycle = 20ns input i_rst , /*------user interface------*/ input i_user_ctrl , output [3 :0] o_user_chnl , output [15:0] o_user_data_1 , output o_user_valid_1 , output [15:0] o_user_data_2 , output o_user_valid_2 , output [15:0] o_user_data_3 , output o_user_valid_3 , output [15:0] o_user_data_4 , output o_user_valid_4 , output [15:0] o_user_data_5 , output o_user_valid_5 , output [15:0] o_user_data_6 , output o_user_valid_6 , output [15:0] o_user_data_7 , output o_user_valid_7 , output [15:0] o_user_data_8 , output o_user_valid_8 , /*------AD7606 interface------*/ output o_ad_psb_sel , output o_ad_stby , output o_ad_range , output [2 :0] o_ad_osc , output o_ad_reset , output o_ad_convstA , output o_ad_convstB , output o_ad_cs , output o_ad_rd , input i_ad_busy , input i_ad_firstdata , input [15:0] i_ad_data );

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

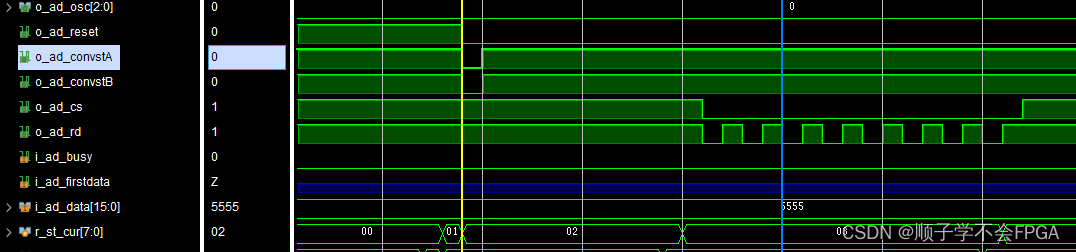

二、状态机转移

状态转移过程:

always @(*)begin

case(r_st_cur)

P_ST_RESET : r_st_nxt = r_st_cnt == 10 ? P_ST_CONVST : P_ST_RESET ;

P_ST_CONVST : r_st_nxt = ri_user_ctrl ? P_ST_BUSY : P_ST_CONVST ;

P_ST_BUSY : r_st_nxt = r_st_cnt >= 10 && !ri_ad_busy ? P_ST_READ : P_ST_BUSY ;

P_ST_READ : r_st_nxt = r_st_cnt == 16 - 1 ? P_ST_WAIT : P_ST_READ ;

P_ST_WAIT : r_st_nxt = r_st_cnt == 70 ? P_ST_RESET : P_ST_WAIT ;

default : r_st_nxt = P_ST_RESET;

endcase

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

P_ST_RESET :复位状态,需要满足至少50ns,所以状态计数器需要计数多少个周期需要看自己的设计当中时钟频率,我这里是50Mhz,状态计数器计数到10即200ns,符合时序。

P_ST_CONVST :转换状态,即控制CONVSTA/B信号产生上升沿。图中黄线部分

P_ST_BUSY :忙状态,等待一段时间后开始读忙信号,不忙则进入读数据状态

P_ST_READ :控制CS和RD信号开始读数据,读8个数据,在RD上升沿进行读数据

P_ST_WAIT :等待状态,俩次转换操作之间需要等待一个tCYCLE,AD7606在并行模式下需要5us,具体内容参考上一篇介绍。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/829463

推荐阅读

相关标签