热门标签

热门文章

- 1某东h5st 3.x-4.x 本篇web端4.7的生成方式和逆向分享_h5st4.7

- 2用于文本的TensorFlow:使用TensorFlow进行词嵌入_文本张量表示 tensorflow

- 3Hive中的索引_hive charindex

- 4LabVIEW 32位与64位版本比较分析:性能与兼容性详解

- 5时序收敛:基本概念

- 6SpringBoot的端口占用问题_spring启动端口占用

- 7数据结构—List底层_c# list底层

- 8今日头条 2018 AI Camp 5 月 26 日在线笔试编程题第一道——最佳路径_有一个n*m的矩阵 ,且矩阵中的每个方格都有一个整数

- 9优象光流使用的一些注意事项(转载)(光流数据要融合其他传感器使用比较好)_优像光流

- 10阿里云服务器搭建hadoop集群后无法访问9870,8088web端口解决方案_阿里云服务器登不上hadoop的8970

当前位置: article > 正文

FPGA基础之内置逻辑门_fpga 逻辑门

作者:繁依Fanyi0 | 2024-06-16 09:38:16

赞

踩

fpga 逻辑门

目录

verilog语言中,针对逻辑门,有许多内置可直接使用的逻辑门,从输入输出数量可分为多输入门和多输出门。

一、多输入门

有单个或多个输入,只有单个输出的逻辑门,包含and(与),or(或),xor(异或),nand(与非),nor(或非),xnor(同或/异或非)门等。

二、多输出门

有单个或多个输出,只有单个输入的逻辑门,多输出门的作用主要是用于缓冲作用。此处定义可看出与多输入门存在重叠,未方便记忆,可记住只有以下两种:buf,not(非)

三、特殊门

3.1 三态门

三态门:三态门可理解为带有控制端的缓冲门,只有在控制信号有效时,数据才能传递,否则输出为高阻态z。

三态门端口分为一个输入端口,一个输出端口,一个控制端口。

类型:bufif0、bufif1、notif0、notif1,bufif0/notif0在控制信号为1时,输出为z,为0时数据输出,bufif1/notif1在控制信号为0时,输出为z,为1时数据输出,

格式:如bufif0 test(out,in,control)

3.2 上拉/下拉电阻

只有输出没有输入,上拉电阻pullin将输出固定为1,下拉电阻pulldown将输出固定为0

格式:pullin pull_in(out1)

3.3 MOS 开关

包含cmos、pmos、nmos、rcmos、rpmos、rnmos

输入输出端口:与三态门类似,第一个端口为输出,第二个端口为输入,第三个为控制端口

nmos和rnmos开关在控制信号为0,pmos和rpmos开关在控制信号为1时,输出为z

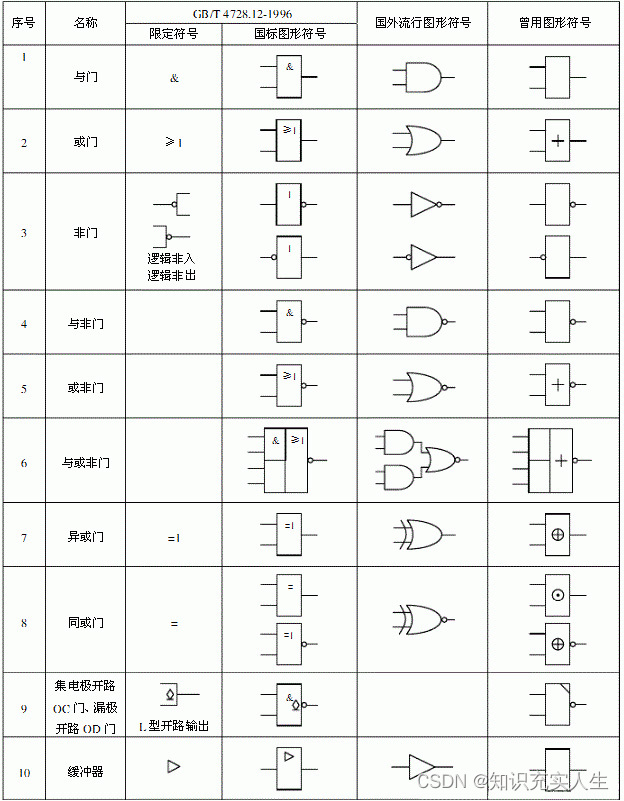

四、逻辑门图形符号

各种逻辑门的图像符号如下图,注:图片来源百度图片

五、参考来源

部分内容来源于《Verilog Hdl 硬件描述语言.pdf》

声明:本文内容由网友自发贡献,转载请注明出处:【wpsshop】

推荐阅读

相关标签