- 1kafka java api示例_kafka生产者和消费者的javaAPI的示例代码

- 2彻底弄懂ES6中的Map和Set

- 3论文浅尝 | 基于表示学习的大规模知识库规则挖掘

- 4监控MySQL的工具_mysql enterprise monitor

- 5Redis面试题24道

- 6ModuleNotFoundError: No module named ‘mysql‘解决方案_modulenotfounderror: no module named 'mysql

- 7Linux Mysql表名默认区分大小写【已解决】_mysql-5.7.18 linux版本的配置文件区分大小写

- 8正排索引 vs 倒排索引 - 搜索引擎具体原理_正排索引和倒排索引

- 9MAC OS X 系统镜像各版本下载_macos下载

- 10git 下载特定分支_git 下载分支

FPGA图像处理——YCbCr灰度转换

赞

踩

之前的单通道灰度转换作为一个图像处理FPGA框架搭建完成后的一个简单效果的测试,其图像的层次感有待提高,图像处理灰度转换用的更多的还是YCbCr。

一、YCbCr

YCbCr或Y’CbCr有的时候会被写作:YCBCR或是Y’CBCR,Y’为颜色的亮度(luma)成分、而CB和CR则为蓝色和红色的浓度偏移量成份。Y就是所谓的亮度(luminance),表示光的浓度且为非线性,使用伽马修正(gamma correction)编码处理。人的肉眼对视频的Y分量更敏感,因此在通过对色度分量进行子采样来减少色度分量后,肉眼将察觉不到的图像质量的变化,因此后面的图像处理使用灰度图像都是基于Y分量图像。以后这个YCbCr工程将被作为图像处理的模板。

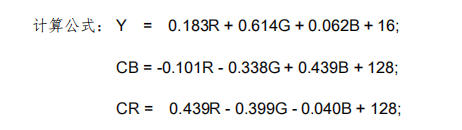

RGB转YCbCr:

二、MATLAB图像处理

代码:

效果图:

这张图目测Y分量和G分量差别不大,理论上Y分量图像的层次感是最好的,在其他更加精致的图像上能比较明显的观察到,但由于我比较喜欢这张图,就放这张图的效果图好了。

三、FPGA实现

工程设计图和上一个单通道是一致的,都是简单的图像变换,时序上只要求信号同步。将上个单通道输出部分重新编写即可。

1.由于FPGA无法进行浮点数运算,需要将浮点数进行转换。

将浮点数乘以256后,向右移位8位(相当于除以256),再把123写进括号即为YCbCr最终的Verilog表达式。

2.RGB转YCbCr

(1)接收数据,有tft传过来的数据为RGB565,通过低位补零转为RGB888

//组合逻辑无时延

assign R0 = {TFT_rgb[15:11],3'd0};

assign G0 = {TFT_rgb[10:5],2'd0};

assign B0 = {TFT_rgb[4:0],3'd0};

- 1

- 2

- 3

- 4

(2)首先进行上述运算的第一步,乘法运算256对应系数

//时序逻辑,延时clk1

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

{R1,G1,B1} <= {16'd0, 16'd0, 16'd0};

{R2,G2,B2} <= {16'd0, 16'd0, 16'd0};

{R3,G3,B3} <= {16'd0, 16'd0, 16'd0};

end

else begin

{R1,G1,B1} <= {{R0 * 16'd77}, {G0 * 16'd150}, {B0 * 16'd29 }}; //Y = 0.299*R + 0.587*G + 0.114*B

{R2,G2,B2} <= {{R0 * 16'd43}, {G0 * 16'd85}, {B0 * 16'd128}}; //Cb = 0.586*(B-Y) + 128 = -0.172*R - 0.339*G + 0.511*B + 128

{R3,G3,B3} <= {{R0 * 16'd128}, {G0 * 16'd107}, {B0 * 16'd21 }}; //Cr = 0.713*(R-Y) + 128 = 0.511*R - 0.428*G - 0.083*B + 128

end

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

(3)把YCbCr常数项128加入

//第二次延时clk1

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)begin

Y1 <= 16'd0;

Cb1 <= 16'd0;

Cr1 <= 16'd0;

end

else begin

Y1 <= R1 + G1 + B1; // Y = ( 77*R + 150*G + 29*B) >> 8

Cb1 <= B2 - R2 - G2 + 16'd32768; //128扩大256倍// Cb = (-43*R - 85*G + 128*B + 32768) >> 8

Cr1 <= R3 - G3 - B3 + 16'd32768; //128扩大256倍// Cr = (128*R - 107*G - 21*B + 32768) >> 8

end

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

(4)除以256即右移8位,即用一个8位数取16位数据的高8位

//第三次延时clk1

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)begin

Y_out <= 8'd0;

Cb_out <= 8'd0;

Cr_out <= 8'd0;

end

else begin

Y_out <= Y1[15:8];

Cb_out <= Cb1[15:8];

Cr_out <= Cr1[15:8];

end

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

(5)到此处,YCbCr格式数据得到了,只用Y分量,取Y分量的高位565值,最终输出ycbcr_rgb

assign ycbcr_rgb = {Y_out[7:3],Y_out[7:2],Y_out[7:3]};

- 1

到这里,到这里对于信号ycbcr已经得到,中间三个时序变化,延时3个clk,控制信号也要同步

(6)把控制信号进行同步(手法!!!!!)

always @(posedge clk or negedge rst_n) begin if(!rst_n) begin TFT_de_r <= 3'b0; TFT_hs_r <= 3'b0; TFT_vs_r <= 3'b0; TFT_pwm_r <= 3'b0; TFT_begin_r <= 3'b0; TFT_clk_r <= 3'b0; end else begin TFT_de_r <= {TFT_de_r[1:0], TFT_de}; //延时一个时钟_ _ de 延时两个时钟_ de de 延时三个时钟de de de TFT_hs_r <= {TFT_hs_r[1:0], TFT_hs}; TFT_vs_r <= {TFT_vs_r[1:0], TFT_vs}; TFT_pwm_r <= {TFT_pwm_r[1:0], TFT_pwm}; //延时一个时钟_ _ de 延时两个时钟_ de de 延时三个时钟de de de TFT_begin_r <= {TFT_begin_r[1:0], TFT_begin}; TFT_clk_r <= {TFT_clk_r[1:0], TFT_clk}; end end //取最高位,即完成控制信号的同步延时三个clk时钟 assign ycbcr_de = TFT_de_r[2]; assign ycbcr_hs = TFT_hs_r[2]; assign ycbcr_vs = TFT_vs_r[2]; assign ycbcr_pwm = TFT_pwm_r[2]; assign ycbcr_begin = TFT_begin_r[2]; assign ycbcr_clk = TFT_clk_r[2];

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

3.rtl视图

4.开发板验证图