- 1java.security.cert.CertificateException异常的正确解决方法,亲测有效,嘿嘿嘿

- 2Git下载和安装_git 下载

- 3zookeeper is not a recognized option

- 4【11】SCI易中期刊推荐——计算机方向(中科院4区)_非oa 人工智能sci四区

- 5Pytorch实用教程:pytorch中 argmax(dim)用法详解

- 6提示词(prompt)工程指南(三):高级提示_awesome prompt

- 7Python中4种读取JSON文件和提取JSON文件内容的方法

- 8【Linux】shell编程4(break语句、continue、exit、shell的函数、返回值return)_linux break

- 9凸多边形最优三角剖分(算法设计:动态规划)_凸多边形的最优三角剖分,按照三步,采用动态规划去解决

- 10Python常用模块 之 redis:连接和操作redis数据库_python redis库

NES(FC) FPGA游戏卡开发笔记(3)---- AGM AG32VF407开发环境的使用

赞

踩

AG32VF407是内带2K FPGA逻辑单元的MCU芯片。虽然目前不考虑这款FPGA芯片,因为是开发笔记,就记录一下我的学习使用过程。使用这个IDE就是想了解一下这块MCU到底如何使用的。

安装IDE说明

http://www.tcx-micro.com/doc_25499579.html提供了AGM MCU的开发软件下载。需要安装python3.8版本以上(因为AGM board的脚本使用3.8支持的语法,platformio自带的是3.7.7,会编译出错)。

IDE是基于VS-code的platformio。开发软件就是把package和platform加入到platformio环境中。

platformio/platforms

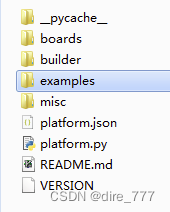

安装之后,在用户.platformio/platforms/中增加了AgRV的链接,链接到实际的agrv安装目录,下面是AgRV文件夹的内容,boards包括多款AGM MCU board源代码,builder下面是py编译脚本。

AgRv目录:

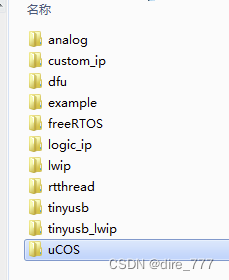

examples提供了一些有用的开发实例。

platformio/packages

下图中的快捷链接都是ArGV安装的framework和tools,包括ucoas,freertos,lwip,ips,sdk等源代码。tools包括flash下载,jlink下载调试,logic综合(FPGA编译生成bit stream文件,就是supra FPGA开发软件),risv-v编译工具。

编译遇到的问题

随便用了例子在platformio中试用一下。Py脚本运行出错,原因是platformio使用自带的python版本是3.7.7,有些语法需要在3.8以上才能运行。编译的时候使用platformio自带的python。

解决:在platformio配置中禁止使用内部python之后问题解决。

看了芯片手册之后的疑问:2K FPGA到底怎么配置生效

手册没有任何有用的信息。没有FPGA配置说明。

我从源代码中一步一步分析了解其使用方式。

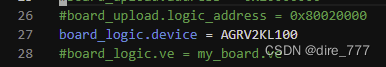

1)在platformio.ini(项目环境配置文件,格式见官网,可以进行扩展使用)中,

说明这个F407的逻辑设备是ARGV2K,而ARGV2K正好是AGM的另外一块纯2K FPGA芯片,下载了手册和烧写说明文档,只是从JTAG进行配置FPGA,没有其他有用信息。

通过分析F407 python编译脚本,首先了解了可以在platformio进行fpga的编译下载,MCU代码和FPGA代码是分开编译(可以合并下载吗?)。logic_address地址是芯片内部flash地址(地址起始位置有什么需求吗?)。

最后在agrv_sdk源代码中找到了我要了解的东西。

见agrv_sdk的fcb.c, fcb.h, example_fcb.c。(FCB:flash control block)

- #define FCB FCB0 // This is the only FCB supported

-

- // To store the config address of FPGA bit stream and it's complement value

- #define FPGA_CONFIG_ADDR 0x81000030

- #define FPGA_CONFIG_ADDR_N 0x81000034

-

- #define FCB_CTRL_INIT (1 << 0)

- #define FCB_CTRL_WRITE (1 << 1)

- #define FCB_CTRL_READ (1 << 2)

- #define FCB_CTRL_UPDATE (1 << 3)

- #define FCB_CTRL_ACTIVATE (1 << 4)

- #define FCB_CTRL_DEACTIVATE (1 << 5)

- #define FCB_CTRL_AUTO (1 << 6)

- #define FCB_CTRL_DMA (1 << 7)

-

- #define FCB_STAT_INIT (1 << 0)

- #define FCB_STAT_ACTIVE (1 << 1)

- #define FCB_STAT_ERR_ID (1 << 4)

- #define FCB_STAT_ERR_HEADER (1 << 5)

- #define FCB_STAT_ERR_CRC (1 << 6)

- #define FCB_STAT_ERR_ALL (FCB_STAT_ERR_ID | FCB_STAT_ERR_HEADER | FCB_STAT_ERR_CRC)

-

- #define FCB_AUTO_WORDS (99944 / 4)

-

- typedef struct

- {

- __IO uint32_t CTRL; // 0x00

- __IO uint32_t ADDR; // 0x04

- __IO uint32_t DATA; // 0x08

- __IO uint32_t AUTO; // 0x0c

- __IO uint32_t STAT; // 0x10

- __IO uint32_t INT; // 0x14

- } FCB_TypeDef;

头文件中定义了FPGA配置地址寄存器(指向bit stream文件存放在flash中的地址,用两个word表示)。最大99944字节长。

FCB结构图(struct FCB_TypeDef),是内存控制块寄存器,指向0x4001000。进行这些寄存器进行配置操作。

- #define FCB0_BASE 0x40010000

- #define FCB0 ((FCB_TypeDef *) FCB0_BASE)

- #define APB_MASK_FCB0 (1 << 0)

- #define FCB0_DMA_REQ 5

- #define FCB0_IRQn 3

两种配置函数,一种是单字节写,一种是DMA方式。

- // Fully automatic FPGA configuration. config_addr must point to configuration bit stream generated by Supra software

- ReturnCodeTypedef FCB_AutoConfig(uint32_t config_addr)

- {

- FCB->CTRL = FCB_CTRL_AUTO;

- uint32_t *ptr = (uint32_t *)config_addr;

- for (int i = 0; i < FCB_AUTO_WORDS; ++i) {

- FCB->AUTO = *ptr++;

- }

- return (FCB_IsActive() && !FCB_IsAnyError()) ? RET_OK : RET_ERR;

- }

-

- // The DMA version is about 2x faster

- ReturnCodeTypedef FCB_AutoConfigDma(uint32_t config_addr, DMAC_ChannelNumTypeDef channel)

- {

- FCB->CTRL = FCB_CTRL_AUTO;

- DMAC_WaitedTransfer(channel, config_addr, (uint32_t)(&FCB->AUTO), DMAC_ADDR_INCR_ON, DMAC_ADDR_INCR_OFF,

- DMAC_WIDTH_32_BIT, DMAC_WIDTH_32_BIT, DMAC_BURST_256, DMAC_BURST_256, FCB_AUTO_WORDS,

- DMAC_MEM_TO_MEM_DMA_CTRL, 0, 0);

- return (FCB_IsActive() && !FCB_IsAnyError()) ? RET_OK : RET_ERR;

- }

AGM MCU AG32在VSCode下的使用入门提供的信息

(见链接):

http://www.tcx-micro.com/doc_26309003.html

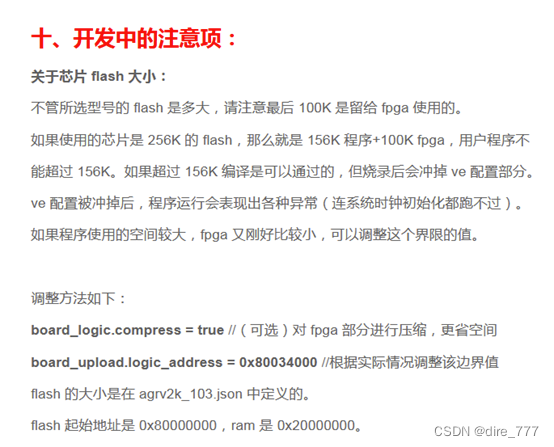

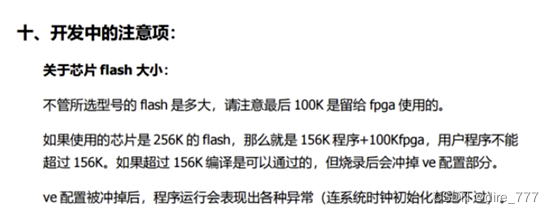

在第十节开发注意项中说明logic_address指向内部flash地址。jtag下载bit stream文件到这个地址。(然后怎么加载生效?)

上面这个信息是今天更新的?因为我5-29号截的图是这样的。

总结一下

集成在platfomio开发环境中进行芯片固件开发还是不错的。同时提供了logic和固件编译下载调试。提供了好几种常用的framework bsp包,sdk也很完整,python脚本和c代码写得都很清晰,方便使用。

芯片手册真的没法详细些吗?memory mapping详细说明,寄存器定义和使用这些对开发者这么重要的东西需要那么保密吗?