热门标签

热门文章

- 1google浏览器网站不安全与网站的连接不安全怎么办?_chrome你与此网站之间建立的连接不安全

- 2最简单逢7杀人游戏java代码_java中ab两个人玩抢7游戏

- 3IEEE论文LaTeX模板解析(八)| 列表(List)_latex list

- 4JavaScript 中从数组中删除元素_javascript 数组删除元素

- 5Python3.6安装以及numpy库、matplotlib库的安装方法(Win7)_安装matplotlib库的命令

- 6【突破限制】免费使用Qwen大模型的API接口_qwen api

- 7产品经理面试会被问到什么?_产品经理招聘 非旺季

- 8字节跳动大规模实践埋点自动化测试框架设计_web 埋点 框架

- 9sql server 2008 报错:(provider: 命名管道提供程序, error: 40 - 无法打开到 SQL Server 的连接)_sqlserver2008 无法用servername 登录 命名管道 40

- 10售票系统设计_在web中,休克更新是什么

当前位置: article > 正文

fpga如何约束走线_FPGA中的CLOCK REGION和SLR是什么含义

作者:羊村懒王 | 2024-06-17 12:10:31

赞

踩

fpga中slr与sll

上期内容:FPGA中的BEL, SITE, TILE是什么含义

上期内容:FPGA中的BEL, SITE, TILE是什么含义

由BEL到SITE再到TILE,具体内容可看上篇推文,那么TILE之上是什么呢?

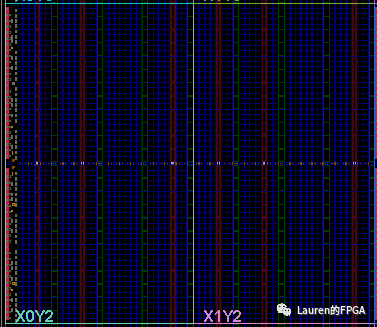

CLOCKREGION 不同类型的TILE按列排列构成了CLOCK REGION,如下图所示。实际上,考虑到时钟走线,每片FPGA都被分割为多个CLOCK REGION。 CLOCK REGION包含多个TILE,而TILE又有SITE构成,SITE又有BEL构成,因此,已知CLOCK REGION可以很方便地找到其下的TILE、SITE和BEL。反过来,已知SITE或TILE,可以找到其所在的CLOCK REGION。但如果已知BEL,不能直接找到其所在的CLOCK

CLOCK REGION包含多个TILE,而TILE又有SITE构成,SITE又有BEL构成,因此,已知CLOCK REGION可以很方便地找到其下的TILE、SITE和BEL。反过来,已知SITE或TILE,可以找到其所在的CLOCK REGION。但如果已知BEL,不能直接找到其所在的CLOCK

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/羊村懒王/article/detail/731150

推荐阅读

相关标签