- 1Redis面试题(总结最全面的面试题!!!)

- 2人工智能大模型即服务时代:OOV问题与解决方案

- 3Meterpreter的常用命令合集_meterpreter命令大全

- 4【持续更新】2024华为 OD 机试 C卷 与D卷 抽中题库清单(全真题库)含考点说明以及在线OJ_2023华为od统一考试(c卷)

- 5【Java】IDEA插件推荐,让你的开发效率翻倍_idea官网插件

- 6Swift5 新特性预览_swift 5心疼行

- 7单细胞RNA测序(scRNA-seq)cellranger count的细胞定量和aggr整合

- 8MySQL表的约束_mysql表格约束

- 9手把手教你安装搭建进销存源码|erp软件|仓库出入库登记系统源码(附源码下载)_erp系统仓库管理系统源码

- 10kafka最全面试题汇总_kafka面试题

Xilinx学习-AXI UART Lite v2.0_ip核axi_uartlite

赞

踩

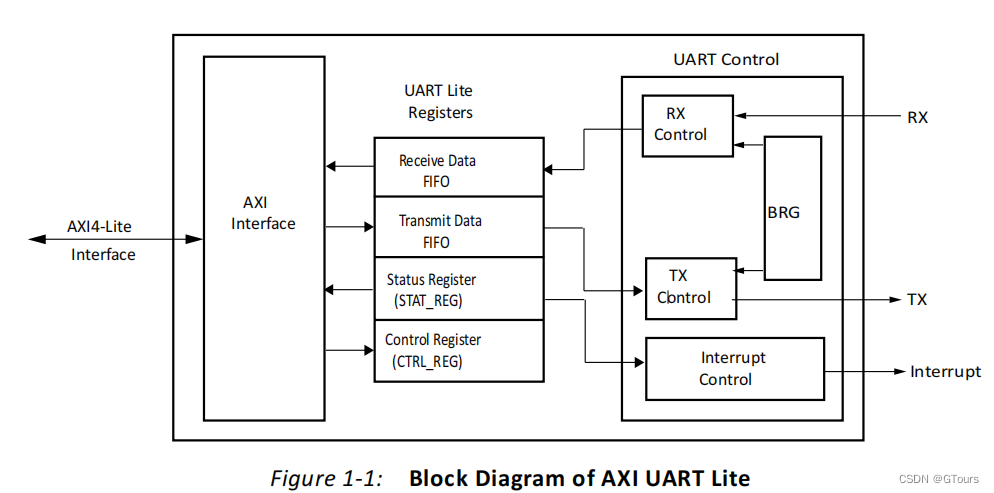

一、概述

AXI UART( Universal Asynchronous Receiver Transmitter) Lite IP核实现串口数据收发,支持AXI-Lite接口,全双工,16字节FIFO,5-8数据位,奇偶或无校验,波特率可配置(只能在Vivado或ISE中配置)。

二、框架

RX:UART RX引脚—>Receive Data FIFO

TX:Transmit Data FIFO—>UART TX引脚

BRG:Baud Rate Generator(只能在Vivado或ISE中配置)

Interrupt Control:中断使能控制。如果使能,Receive Data FIFO非空或Transmit Data FIFO清空时,触发(rising-edge sensitive)中断。

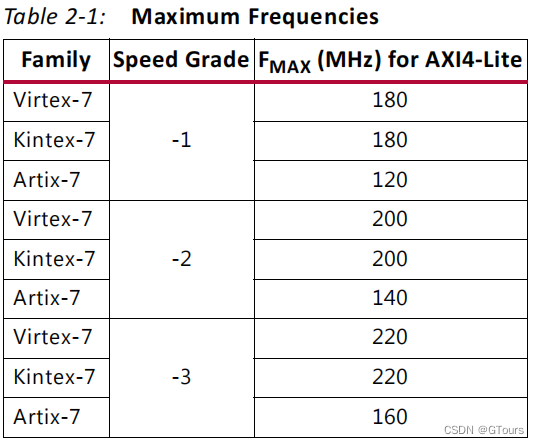

三、时钟

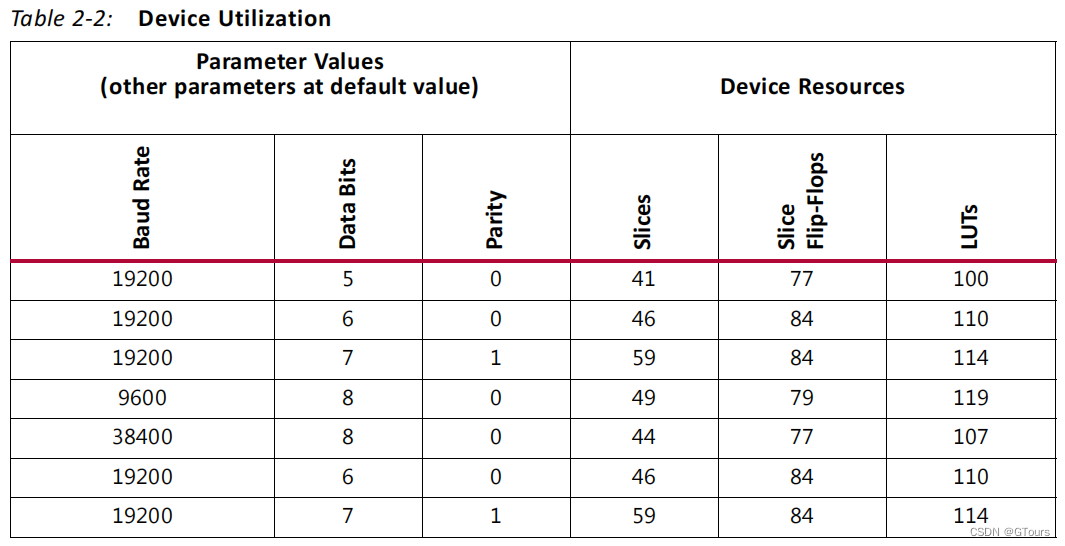

四、资源利用

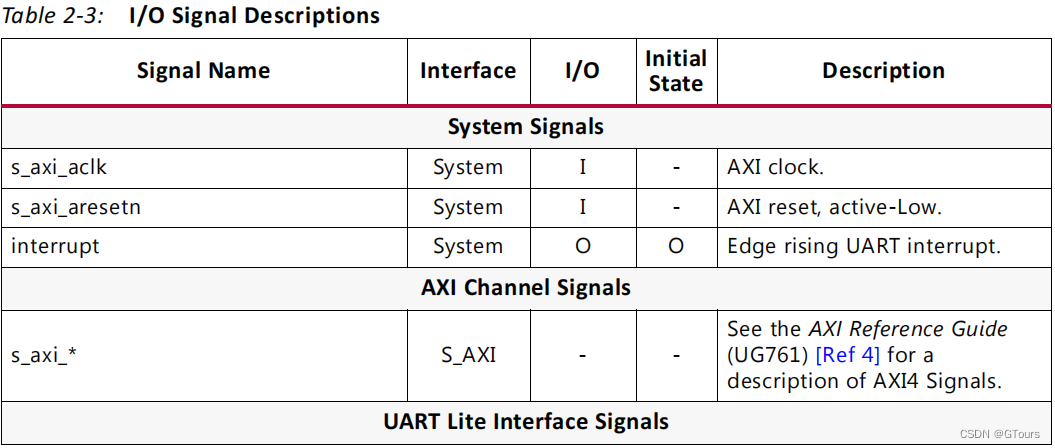

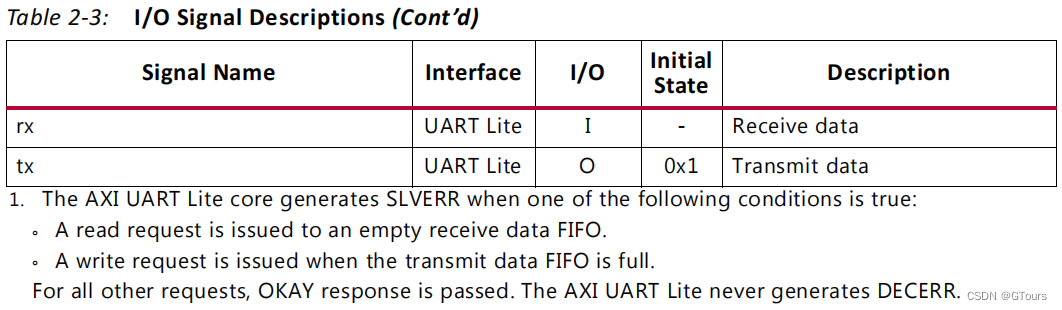

五、信号

SLVERR:传输过程中slave返回的响应:无法处理或内部错误

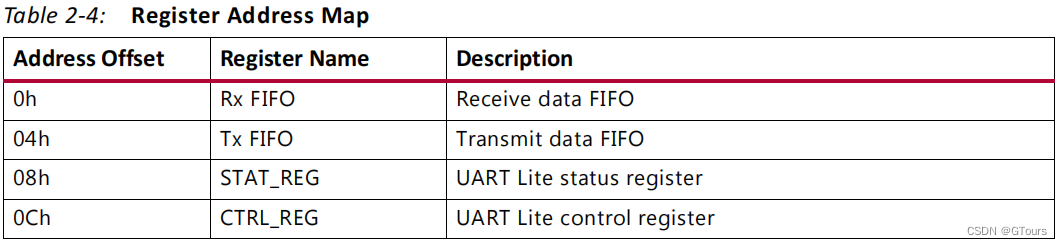

六、寄存器

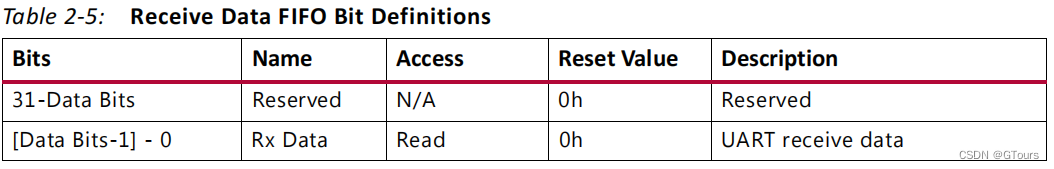

RX FIFO:When a read request is issued to an empty FIFO, a bus error (SLVERR) is generated and the result is undefined. The RX FIFO is a read-only register. Issuing a write request to this register has no effect.

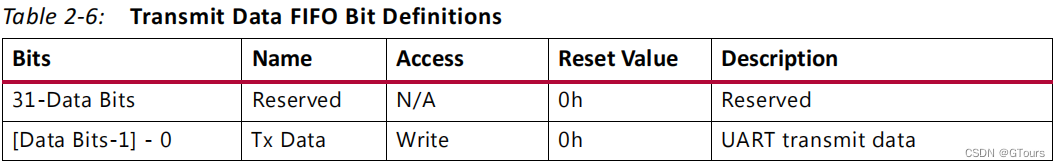

TX FIFO:When a write request is issued while the FIFO is full, a bus error (SLVERR) is generated and the data is not written into the FIFO. This is a write-only location. Issuing a read request to the transmit data FIFO generates the read acknowledgement with zero data.

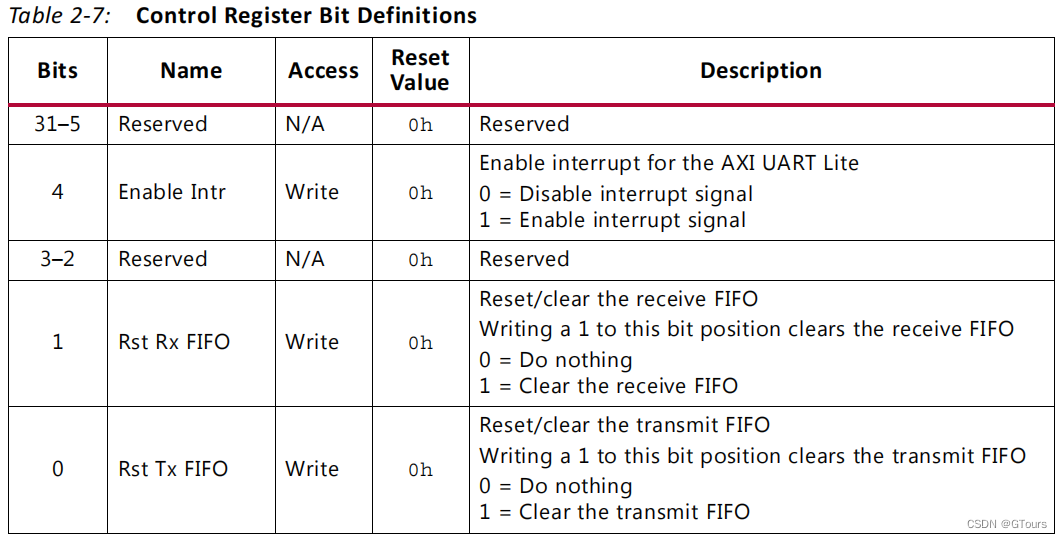

Control Register (CTRL_REG): This is a write-only register. Issuing a read request to the control register generates the read acknowledgement with zero data.

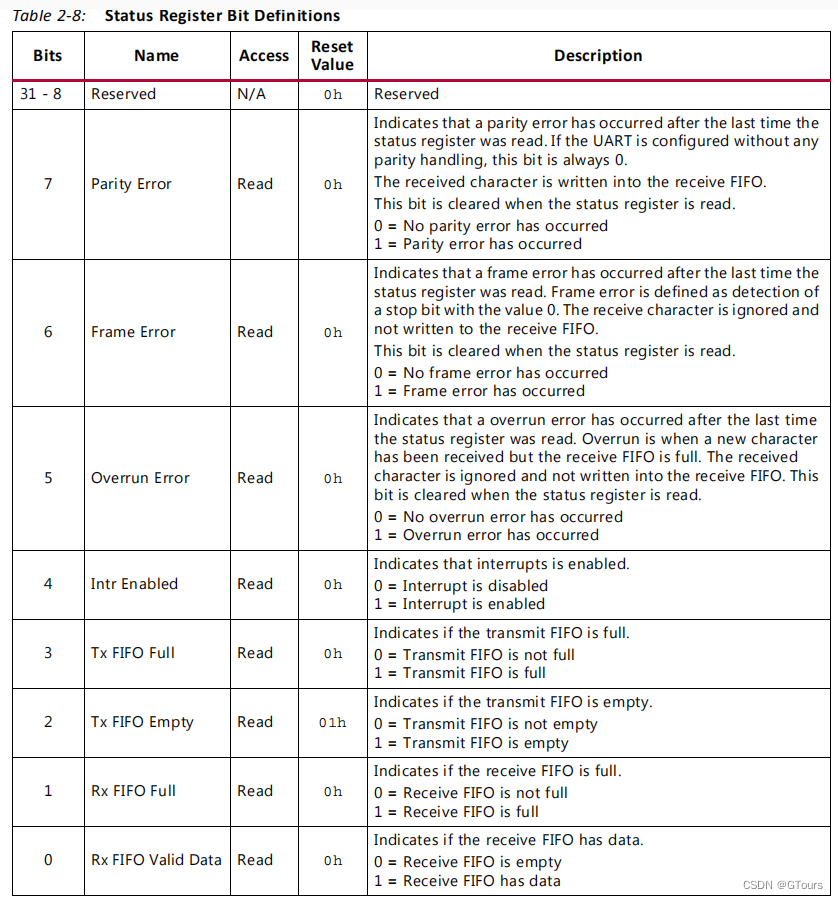

Status Register (STAT_REG):The status register contains the status of the receive and transmit data FIFOs when interrupts are enabled and errors are present. This is a read-only register. A write to this register has no effect.