- 1【NLP】信息抽取

- 2经典的Python爬虫和网络编程面试题

- 3安卓投屏神器 Scrcpy 安装与使用(支持 Mac、Windows、Linux)_scrcpy投屏软件

- 4智谱AI展示国产全自研大模型落地阶段性成果

- 5esp32s3 lvgl wifi sntp 实现时钟功能_esp32s3 不支持sntp

- 6Android13适配所有文件管理权限_pictureselector 安卓13

- 7uni-app开发经验分享十二: Android平台应用启动时读写手机存储、访问设备信息(如IMEI)等权限策略及提示信息...

- 8【view桌面虚拟化系列】1-vSphere搭建

- 9Element-UI - Vue项目整合Element-UI & Icon图标 & 自定义Icon图标_element-ui用自定义icon

- 10【Android】一步步实现手机拍照、录像及存储至相册(CameraX)_安卓开发相机拍照录像

[VIVADO] 集成逻辑分析仪(ILA)的4种使用方法_verilog中ila如何调用

赞

踩

目录

大家好,这里是程序员杰克。一名平平无奇的嵌入式软件工程师。

在日常FPGA开发过程中,逻辑代码设计完成后,为了验证代码逻辑的正确性,优先使用逻辑仿真(modesim)进行验证。仿真验证通过后进行板级验证时,使用逻辑分析仪进行分析和验证逻辑是否正确。FPGA两大主流厂商的软件集成逻辑分析仪供使用,Altera的Quartus自带SignalTap、Xilinx的Vivado自带ILA逻辑调试工具。

本篇总结和分享在Xilinx编译工具Vivado环境下,使用内嵌的逻辑分析仪(ILA)的4种方法:

-

HDL代码实例化ILA IP核

-

Block Design添加ILA IP核

-

Synthesis后对Nets执行Mark Debug操作

-

在HDL代码中使用属性关键字mark_debug

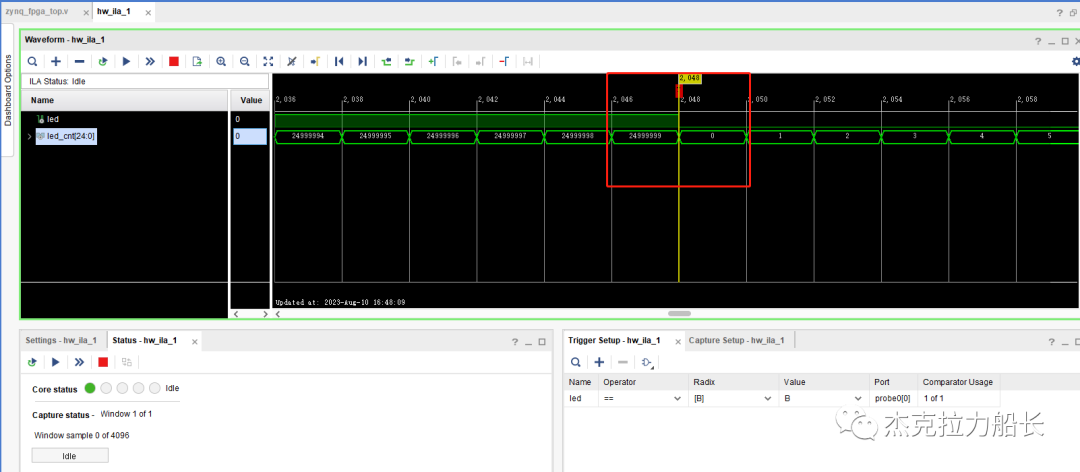

本文以"LED每0.5s间隔亮灭"工程为例,观测led[0]信号以及led_cnt[24:0]时钟计数信号,演示ILA使用的4种方法以及相关的注意事项。

01 HDL代码实例化ILA IP核

-

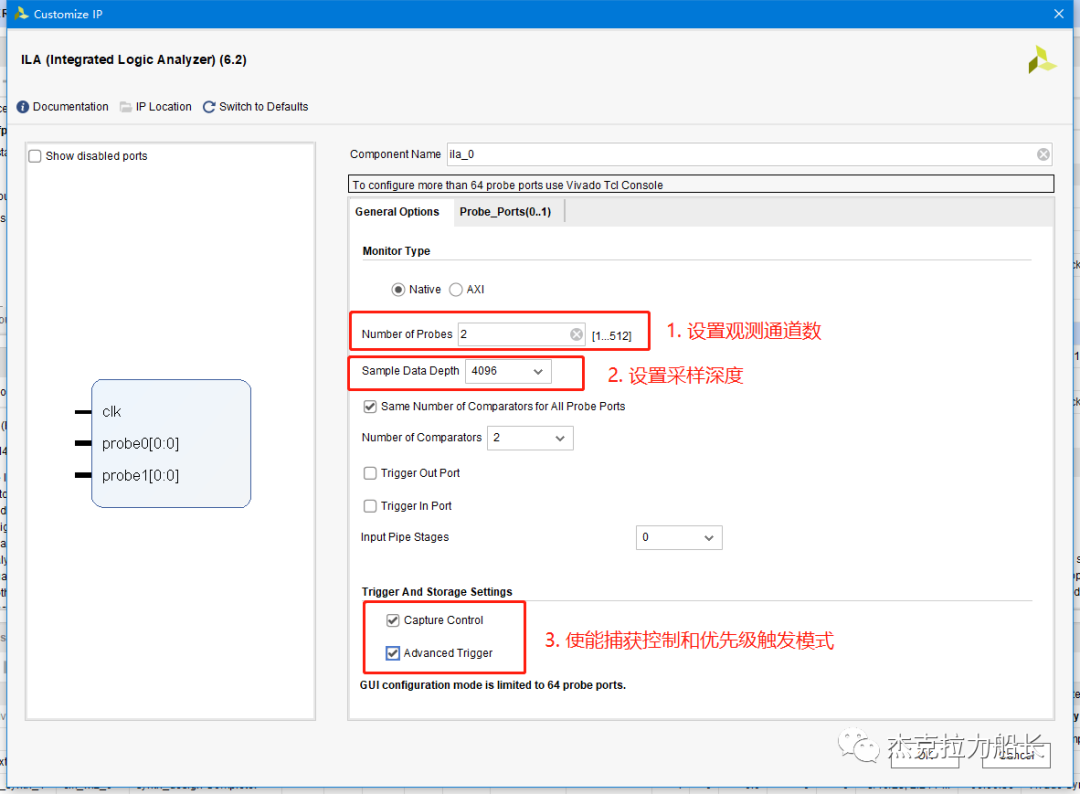

在IP Catalog中搜索ILA,然后双击该IP核进行配置。

-

本示例中led[0]、led_cnt[24:0]信号位宽分别为1、25bit,具体配置如下所示;配置完成后,点击“OK”;在弹出的界面点击“Generate”完成IP核的配置和生成。

-

在Verilog代码中对刚生成的ILA核进行实例化,在具体代码添加例化代码,如下所示:

- ila_0 ila_0_inst0 (

- .clk (clk ), // input wire clk

- .probe0 (led ), // input wire [0:0] probe0

- .probe1 (led_cnt) // input wire [24:0] probe1

- );

-

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

特别说明:对于纯FPGA工程,杰克推荐该方式去使用ILA;

02 Block Design添加ILA IP核

在Vivado中,除了使用HDL语言去描述设计,还可以通过Block Design图形化连接的方式进行设计。7系列的软核MicroBlaze、带硬核的SOC芯片(ZYNQ、MPSOC等)的设计都是通过Block和HDL相结合来描述设计。本文仍以纯FPGA方式来说明在Block Design中使用ILA核(纯FPGA开发不建议)。ILA使用操作如下:

-

创建/打开Block Design,在Diagram界面,点击“+”按钮,搜索ILA,然后双击该IP核进行配置。

-

参数配置的方式与上一小节一致,这里不作赘述。不同之处是在Block Design中使用ILA核,ILA核的实例化HDL代码会自动生成到Block Design文件中。

-

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

特别说明:

带MicroBlaze软核/ARM硬核的FPGA的复杂设计中,模块接口的信号观测ILA使用该方法;模块内部信号的观测ILA使用上一小节的方式;两者可结合使用。

03 综合后添加Mark Debug

-

对工程执行综合,综合完成后,找到要观测的信号的Nets,右键选择“Mark Debug”;

-

要观测信号的Nets选择并设置完成后,点击“Set Up Debug”;按照下面步骤配置Debug ILA参数;

-

Debug ILA配置完成后,保存SYNTHESIZED DESIGN后会在约束文件(.xdc)中生成ILA的配置约束,如下图所示:

-

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

特别说明:mark_debug仅可以对Nets类型进行操作,不能对Cells操作;

04 HDL中使用MARK_DEBUG

-

MARK_DEBUG描述

vivado设计IDE提供了一些属性供开发者使用,本篇推文主要是描述MARK_DEBUG属性约束的使用和注意事项。详细可参考UG912文档的内容。使用MARK_DEBUG的条件如下:

-

约束对象必须是Nets类型

-

在Nets信号的顶端声明处进行约束

vivado提供了包括Verilog、VHDL、XDC三种语法。三种语法如下所示:

- //Verilog语法

- 约束语法:

- (* MARK_DEBUG="value" *)

- #value = true/flase

- 使用示例:

- (* MARK_DEBUG="true" *) output wire led;

- (* MARK_DEBUG="true" *) reg [24:0] led_cnt;

-

-

- //VHDL语法

- 约束语法:

- 声明: attribute MARK_DEBUG : string;

- 语法: attribute MARK_DEBUG of signal_name : signal is "value";

- //signal_name-内部信号, value = TRUE/FALSE

- 使用示例:

- signal led : std_logic;

- attribute MARK_DEBUG : string;

- attribute MARK_DEBUG of led : signal is "TRUE";

-

-

- //XDC语法

- 约束语法:

- set_property MARK_DEBUG value [get_nets <net_name>]

- #value = TRUE/FLASE

- #net_name-是信号名

- 使用示例:

- set_property MARK_DEBUG TURE [get_nets led];

-

使用MARK_DEBUG标记生成ILA观测信号步骤

-

-

在led[0]、led_cnt[24:0]信号的顶端声明处进行约束,省略代码如下:

-

- module led_top(

- input wire clk_i,

- input wire rst_n,

- (* MARK_DEBUG="true" *) output wire led_o

- )

- ;

- ...

- (* MARK_DEBUG="true" *) reg [24:0] led_cnt;

- ...

- endmodule

-

-

执行综合操作,综合完成后,打开综合设计,然后点击“Set Up Debug”;

-

-

-

按照下面步骤配置Debug ILA参数;

-

-

Debug ILA配置完成后,保存SYNTHESIZED DESIGN后会在约束文件(.xdc)中生成ILA的配置约束,如下图所示:

-

-

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

-

特别说明:

MARK_DEBUG约束标记会阻止Vivado对该信号以及下级信号的优化。因此,在逻辑验证完成后,要删除Mark_DEBUG约束标记或者将其失能。

05 文章总结

上面总结和分享了4种Vivado下使用ILA的方法。杰克更推荐使用前面两种实例化的方法去使用ILA IP核。对于纯FPGA HDL开发,配置生成ILA核并在HDL代码中实例化使用便可;对于带软核/硬核的FPGA开发,在Block模块外部接口信号通过添加ILA核,Block模块内部信号则在HDL代码中实例化ILA核,两者结合使用。

参考文档:

vivado Design Suite Properties Reference Guide(UG912)

integrated Logic Analyzer V6.2 Product Guide(PG172)