双口ram的功能实在很妙,能把二个除理器合二为一,强强联合,发挥更强的功能。如小时候看过的动画片,当打不过怪物时,动画的主角总会合体,增加战斗力,把怪物打败。又口ram提供了处理器“合体”的方法和途径。

什么是双口ram呢?我做了以下笔记,仅供参考。

一 定义与简述:

双口RAM 是在一个SRAM 存储器上具有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统同时对该存储器进行随机性的访问。即共享式多端口存储器。

双口RAM最大的特点是存储数据共享。一个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。因为数据共享,就必须存在访问仲裁控制。

内部仲裁逻辑控制提供以下功能:对同一地址单元访问的时序控制;存储单元数据块的访问权限分配;信令交换逻辑(例如中断信号)等。

双口RAM可用于提高RAM的吞吐率,适用于作于实时的数据缓存。

二 CY7C028V介绍:

双口RAM芯片CY7C028作为一种性能优越的快速通信器件,大多CPU的高速数字系统中非常适用。其特点是:提供两套完全独立的数据线、地址线、读写控制线,允许两个CPU对双端口存储器同时进行操作;具有两套完全的中断逻辑,用于实现两个CPU之间的握手信号;具有完全独立的忙逻辑,可保护两个CPU对同一地址单元进行正确的读写操作。当两个CPU对双口RAM存取时,存在以下四种情况。

(1)两个CPU不同时对同一地址单元存取数据。

(2)两个CPU同时对同一地址单元读出数据。

(3)两个CPU同时对同一地址单元写入数据。

(4)两个CPU同时对同一地址单元操作,一个写入数据,另一个读出数据。

不难看出,在第一和第二种情况下,两个端口的存取不会出现错误,而第三种情况会出现写入错误,第四种情况会出现读出错误。为了避免两个CPU对同一地址单元进行访问时由于地址数据争用而造成的数据读写错误,CY7C028主要提供了以下几种工作方式,下面逐一介绍。

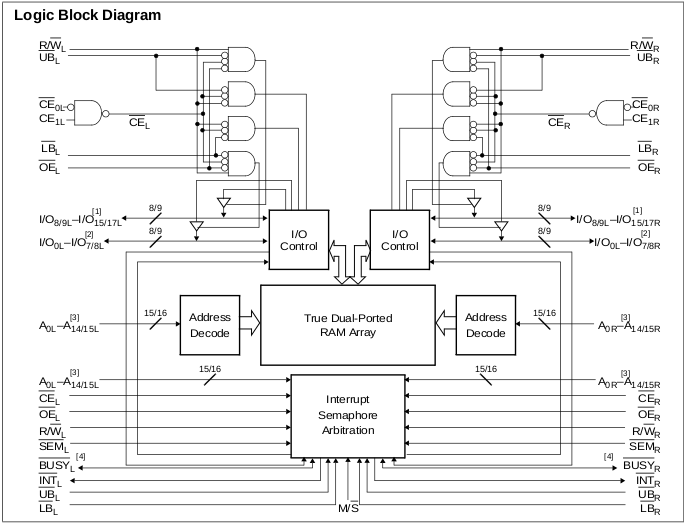

图1 功能框图

1.1 硬件判优方式

双口RAM CY7C028具有解决两个处理器同时访问同一地址单元的硬件仲裁逻辑。在双口RAM的两套控制线中,各有一个BUSY引脚。当两端的CPU不对双口RAM的同一地址单元存取时,BUSYL=H、BUSYR=H,可正常存储;当两端的CPU对双口RAM同一地址单元存取时,哪个端口的存取请求信号出现后,则其对应的BUSY=L,禁止其存取数据;在无法判定两个端口存取请求信号出现的先后顺序时,控制线BUSYL、BUSYR只有一个为低电平。这样,就能够保证对应于BUSY=H的端口能进行正常存取,对应于BUSY=L的端口不能存取,从而避免了两个CPU同时竞争地址资源而引发错误的可能。

1.2 中断判优方式

中断判优方式又称邮箱判优方式。CY7C028具有两套中断逻辑,通过两个INT引脚分别接收到两个CPU的中断引脚上,以实现CPU的握手。在双口RAM的数据传送中,两端的CPU都把双口RAM作为自己存储器的一部分。当两个CPU需要数据传送时,假设左端CPUL向右端CPUR传送,首先CPUL将需要传送的数据存放到双口RAM某段约定的地址单元中,然后向双口RAM的最高奇地址单元0xFFFF即右端口的邮箱进行写操作,用以向CPUR发出一个中断,这样CPUR就进入其相应的中断服务子程序,将约定地址单元的数据读出,然后对双口RAM右端口的邮箱进行写操作,用以清除该中断。

1.3 令牌判优方式

令牌判优方式是一种快速数据交换方式。在此方式中有信令锁存逻辑,CY7C028内部提供了八个相互独立的锁存逻辑单元,最多可将RAM空间分成八个区段。这些锁存逻辑单元独立于双口RAM存储区,并不能控制RAM区、封锁两端CPU的读/写操作,而是被作为命令,只提供指示逻辑,由两端CPU按约定的规则,轮流地占用它们划定的RAM区,各区的大小及地址由软件自由设定,且左右端操作完全一样,只要不超过令牌的限制次数即可。当左右端同时申请同一令牌时,令牌逻辑裁定谁先占用,从而保证只有一个端口获取令牌。而在占用令牌期间,CPU可以按最高速无等待存取数据,这对实现高速、多CPU数据采集与处理系统无疑是非常有利的。但是,为了避免令牌方式争用出错,应尽可能使两端CPU分时占用同一RAM区。