- 1ROCK Pi N10(Rk3399Pro)开发记录 —— 基于Debian10系统的开发环境配置_rock pi系统

- 2【计算机毕业设计】115乐购游戏商城系统

- 3【Linux】anaconda安装

- 4探索Python中的强化学习:Q-learning_python q learning

- 523届春招结束_分享java岗面试心得_23届的java大专

- 62024年运维最新总结一下:运维工程师面试的经历及面试相关问题(1),【2024Linux运维最新学习路线

- 7【应用】【正则化】L1、L2正则化_l1正则化和l2正则化

- 8PDF Squeezer for Mac,让PDF压缩更高效

- 9IDEA下载Maven依赖包报错:Could not transfer artifact org.springframework.boot:spring-boot-starter-parent:pom_idea could not transfer artifact org.springframewo

- 10Git详细安装教程(windows)_windows系统git安装教程(详解git安装过程) - 知乎

OFDM802.11a的FPGA实现(十四)data域的设计优化,挤掉axi协议传输中的气泡

赞

踩

原文链接(相关文章合集):OFDM 802.11a的xilinx FPGA实现

目录

1.前言

前面12篇文章详细讲述了,OFDM 802.11a发射部分data域的FPGA实现和验证,今天对data域的设计做一个总结。在总结过程中,发现了设计中存在bug,经过检查和调试成功的解决了bug,现在对整个过程进行详细描述。

2.data域的时序要求

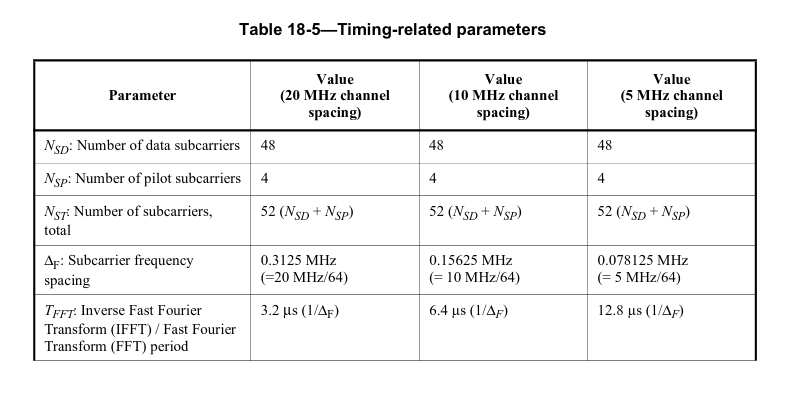

前面设计的时候说到过,根据信道间隔(channel spacing)的不同,可以计算出如下一些参数:

时序参数

时序参数

可以看到当信道间隔为20MHz时,一个OFDM的符号的有效数据周期是3.2us,一个OFDM的符号周期是4us。假设采样率是20M,那么该采样率下的采样周期是50ns,因此一个OFDM符号的有效周期需要64个采样点。所以我们只要保证IFFT的输出数据速率大于20MHz即可,后续在DAC输出的时候,再将数据速率降到20M,由于我们设计的时候数据流一直采用的是vaild-ready握手机制,DAC没有输出完当前数据会对前面的一系列处理形成反压,进而可以保证OFDM符号间不会存在间隙。

考虑到IFFT的输出需要满足20MHz的数据速率,使用最快的传输方案,64-QAM调制+3/4编码效率。编码前的数据速率应该为2063/4=90MHz;编码后的数据速率为20*6=120MHz。为了仿真方便,系统时钟选取125MHz。

总而言之,就是data域的数据必须是以20MHz的速率送给DAC,可以大于20M,但是不能低于20M。也就是,上一个IFFT输出(经过加循环前缀和加窗之后)的80个数据,和下一个之间的时间间隔不能大于8us。

3.Debug

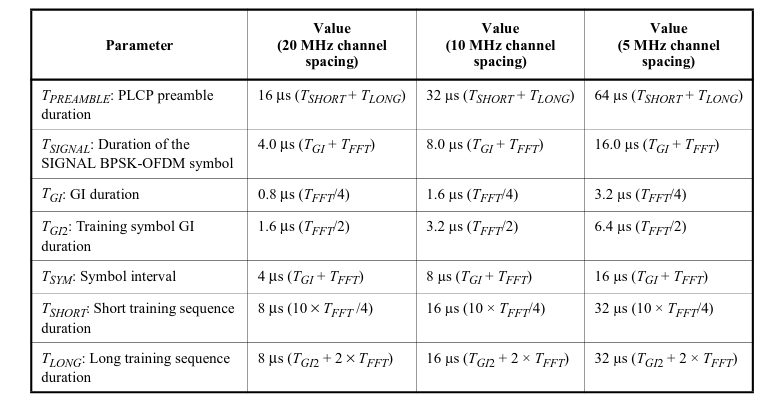

对于之前的设计,按照如下连接方式进行测试:

data域模块连接图

采用64-QAM调制+3/4编码效率。之前的设计仿真结果如下:

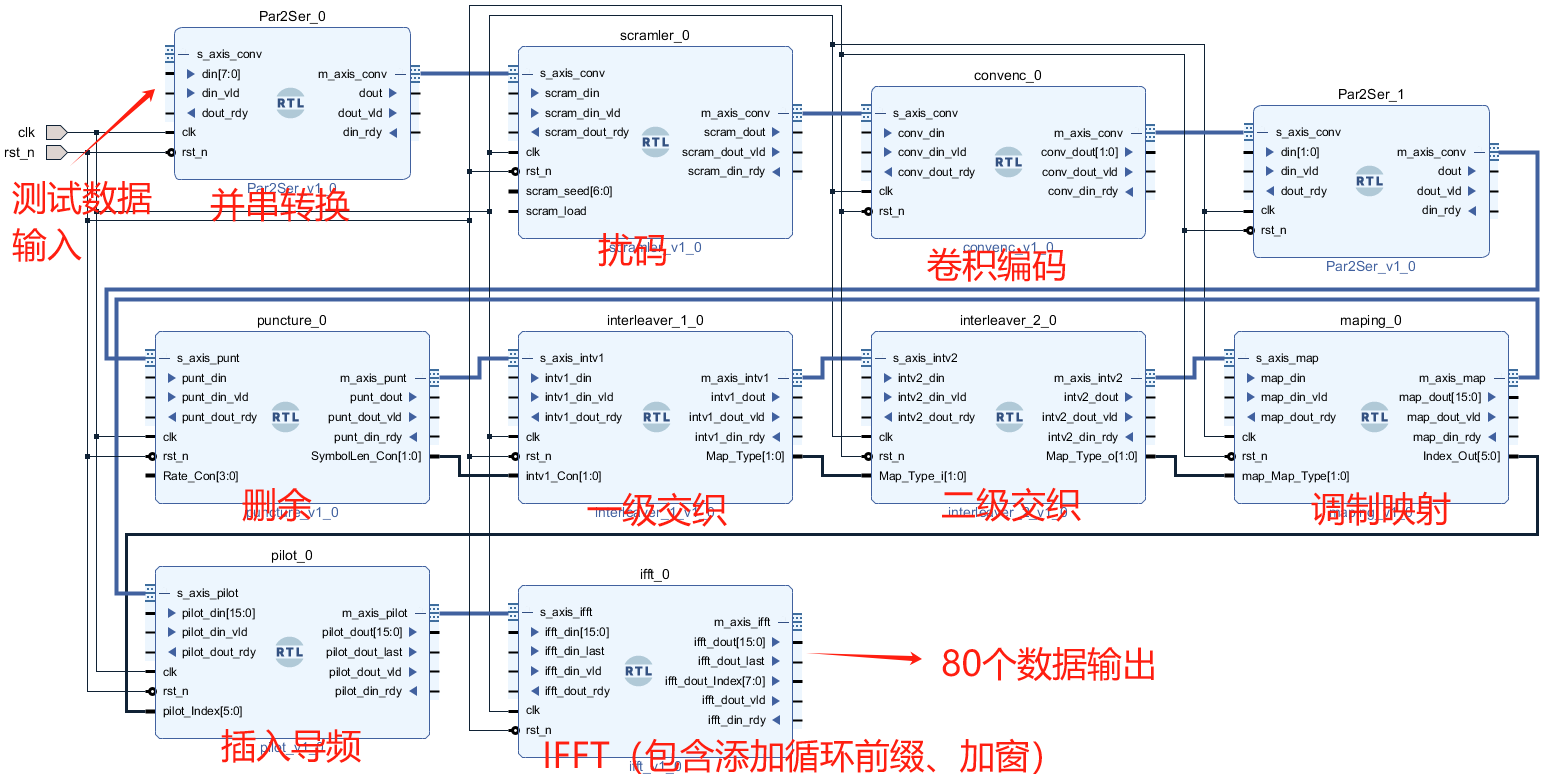

之前有bug的设计仿真结果

从上图可以看到,每个IFFT输出之间,间隔为,是不能够保证OFDM符号间不会存在间隙的,除非将系统时钟提高,但是这样会带来更大的挑战。所以还是着手于去排查问题,检查中间传输是否存在气泡,影响效率。

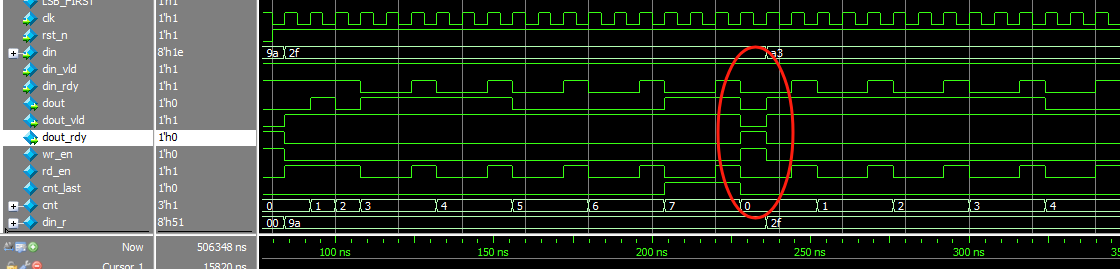

并串转换存在传输气泡

如上图所示,并串转换模块在进行最后一个数据输出后,隔了一个时钟才开始像上游请求接收数据。按理说,应该在传输完最后一个数据,dout_rdy立即拉高,向上游请求接收数据,这里延迟了一个时钟导致产生了一个传输气泡。由于64-QAM调制+3/4编码效率,测试数据一个OFDM符号为216个数,第一次并串转换和后面卷积编码和删余之间使用的模2的并串转换,均会产生大量传输气泡,大大增加了系统延时。点此跳转到之前设计的并串转换模块

更正设计,挤掉传输气泡,代码如下(其中counter为自己设计的计数器IP核点此跳转到计数器篇):

- assign wr_en = dout_rdy & din_vld ;//与上游握手成功,开始接收数据

- assign rd_en = din_rdy & dout_vld ;//与下游握手成功,启动读计数器,开始输出

-

- counter #(.CNT_NUM(WIDTH),

- .ADD(LSB_FIRST))

- u_counter(

- .clk (clk ),

- .rst_n (rst_n ),

- .En_cnt (rd_en ),

- .cnt (cnt ),

- .cnt_last (cnt_last )

- );

-

- assign dout = din_r[cnt];

- always @(posedge clk or negedge rst_n)

- if(!rst_n)begin

- din_r <= 'd0;

- dout_vld <= 1'b0;

- end

- else if(wr_en)begin

- din_r <= din;

- dout_vld <= 1'b1;//写进数据时,输出有效

- end

- else if(rd_en & cnt_last)

- dout_vld <= 1'b0;//输出完成,输出无效;只有在输入数据无效的时候才会进入次判断,保证无气泡传输

-

- /* //初始化时,或输出数据完成,可以接收数据(之前含有气泡的设计)

- always @(posedge clk or negedge rst_n)

- if(!rst_n)

- dout_rdy <= 1'b1;

- else if(cnt_last & rd_en)

- dout_rdy <= 1'b1;

- else if(wr_en)

- dout_rdy <= 1'b0; */

- assign dout_rdy = cnt_last & rd_en | ~dout_vld;//更正后挤掉气泡

如下图所示,可以看到更正之后,数据连续传输,没有气泡。

挤掉并串转换传输气泡

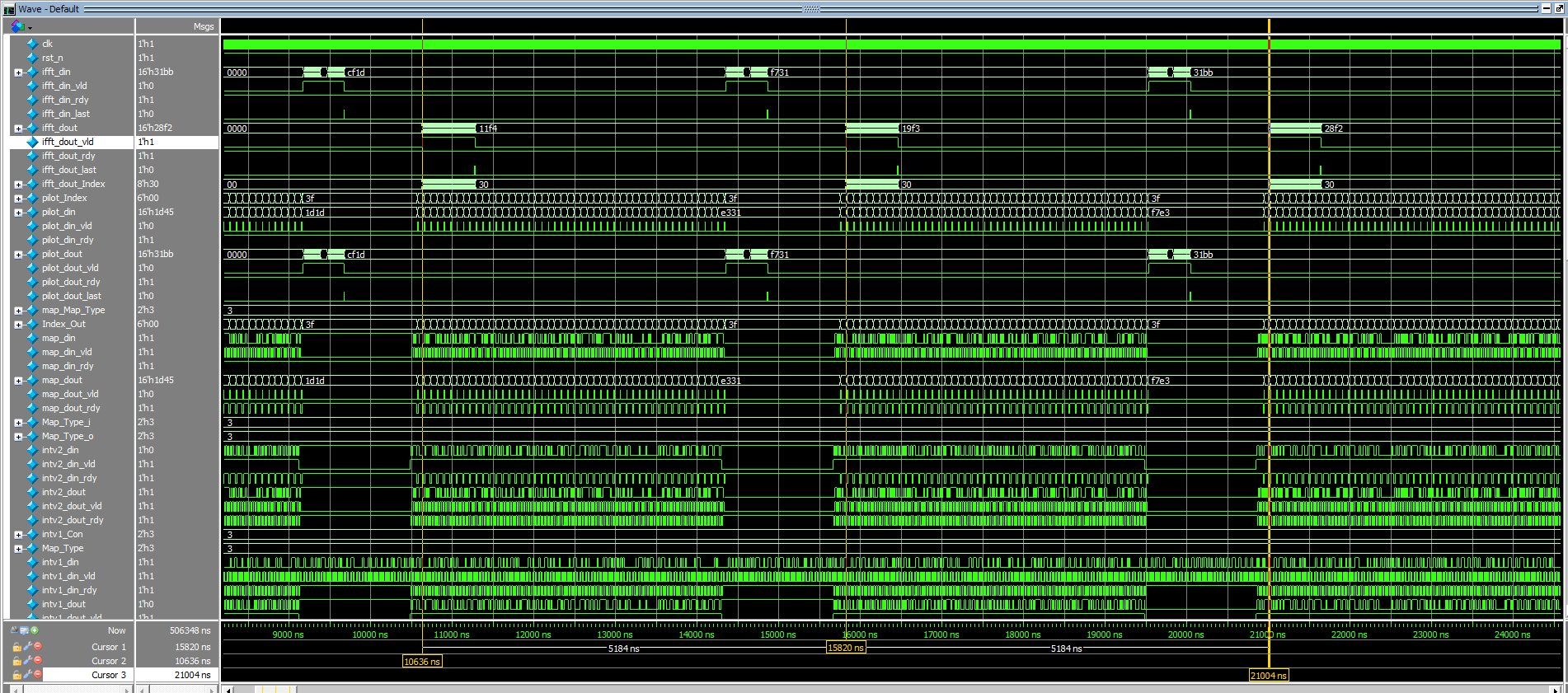

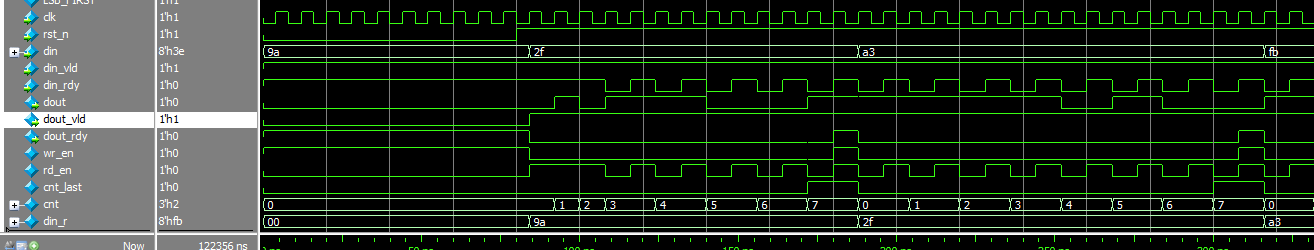

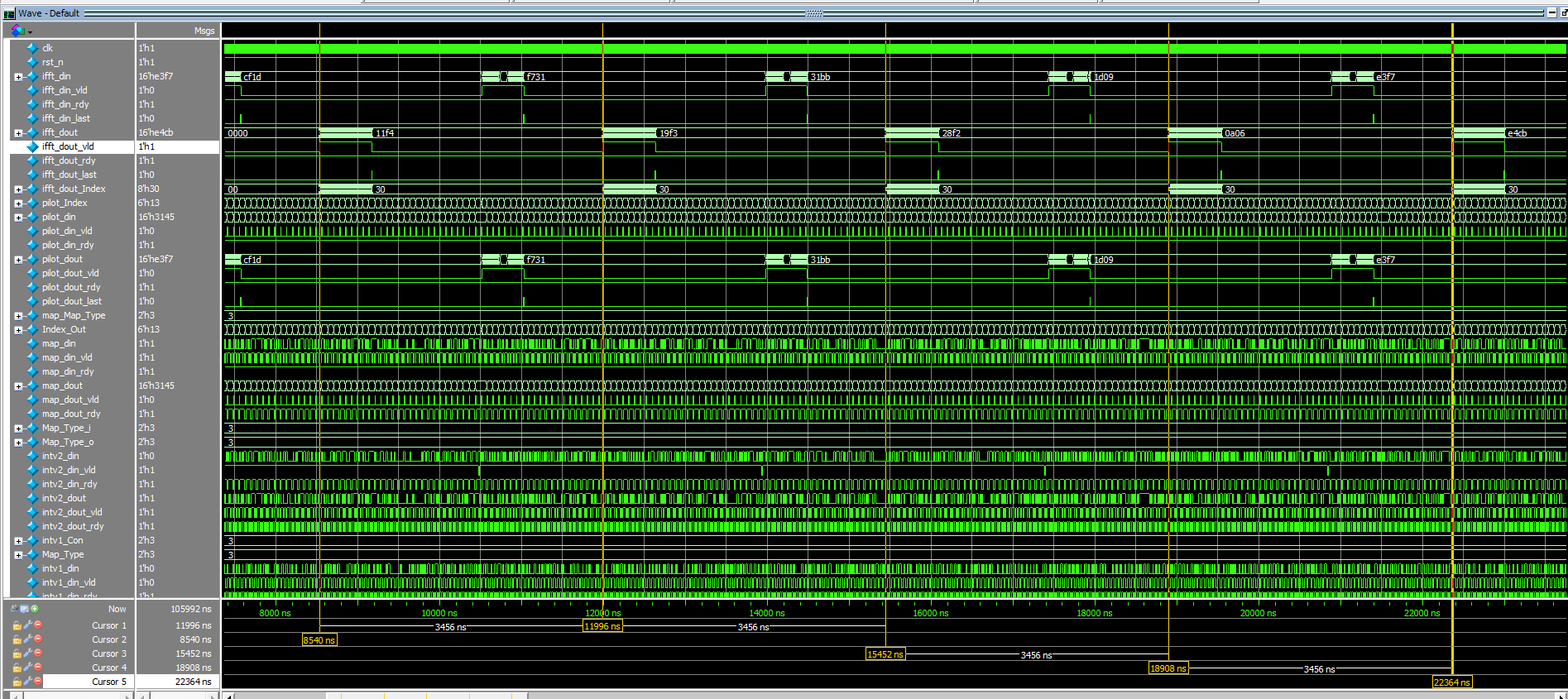

对IFFT输出间隔进行测量:

Debug后IFFT输出间隔

如上图所示,输出间隔为,符合802.11a协议的要求。64-QAM调制+3/4编码效率,符合要求,那么802.11a中其他调制方式也肯定符合要求。

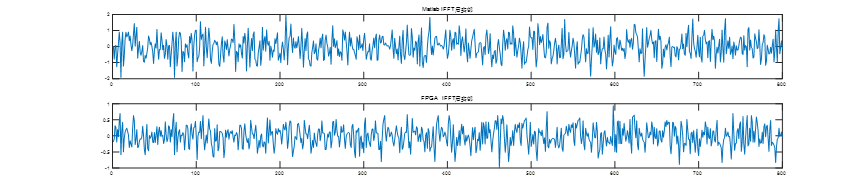

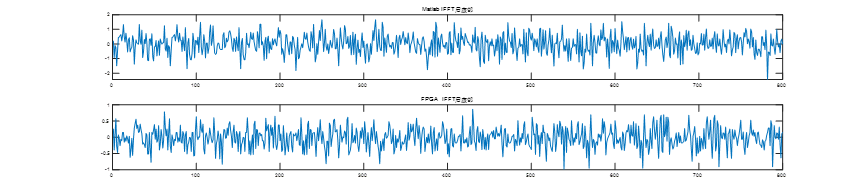

下面是10个OFDM符号,采用64-QAM调制+3/4编码效率,加窗后,FPGA输出和Matlab仿真对比。

实部

虚部

原文链接(相关文章合集):OFDM 802.11a的xilinx FPGA实现