热门标签

热门文章

- 1Lombok常用注解使用方式和Lombok的@EqualsAndHashCode(callSuper = false)存在的问题_lombok callsuper

- 2jquery-淡入淡出效果_jquery循环淡入淡出

- 3面试常见算法题(一)_无序数组倒数第k个

- 4java中http调用组件深入详解_java调用http接口一般用什么组件

- 5【2022届春招经验帖】秋招适用,涵盖简历笔试面试_春招经验分享 怎么丰富简历 怎么匹配工作 避坑大盘点

- 6达梦数据库删除用户_达梦数据库的用户管理

- 7UTF-8字符集_utf8编码对照表

- 8阿里云云产品流转规则设置全攻略【M2M通信】

- 9Pytest中实现自动生成测试用例脚本代码!_使用注解生成pytest自动化测试代码_自动解析需求文档编写测试用例并生成测试代码执行

- 10【总结在ubuntu上源码安装mysql全过程以及错误解决方案】_ubuntu安装mysql报错

当前位置: article > 正文

QuartusDDS信号发生器Verilog代码仿真_dds信号发生器quartus ii 仿真软件编写

作者:菜鸟追梦旅行 | 2024-06-03 10:51:26

赞

踩

dds信号发生器quartus ii 仿真软件编写

名称:QuartusDDS信号发生器Verilog代码仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

DDS信号发生器

可以输出正弦波、方波、三角波

可以改变波形的频率

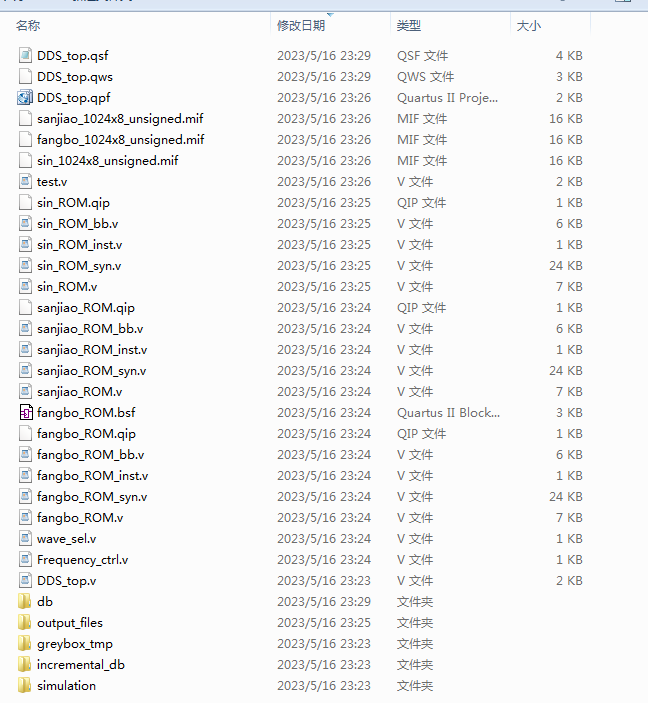

1. 工程文件

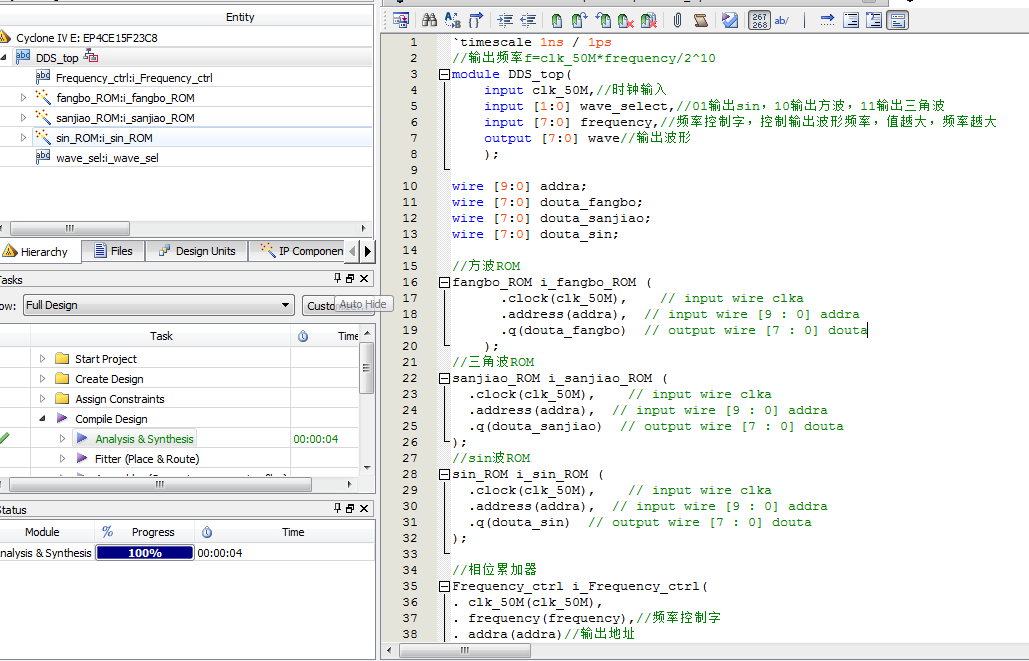

2. 程序文件

3. 程序编译

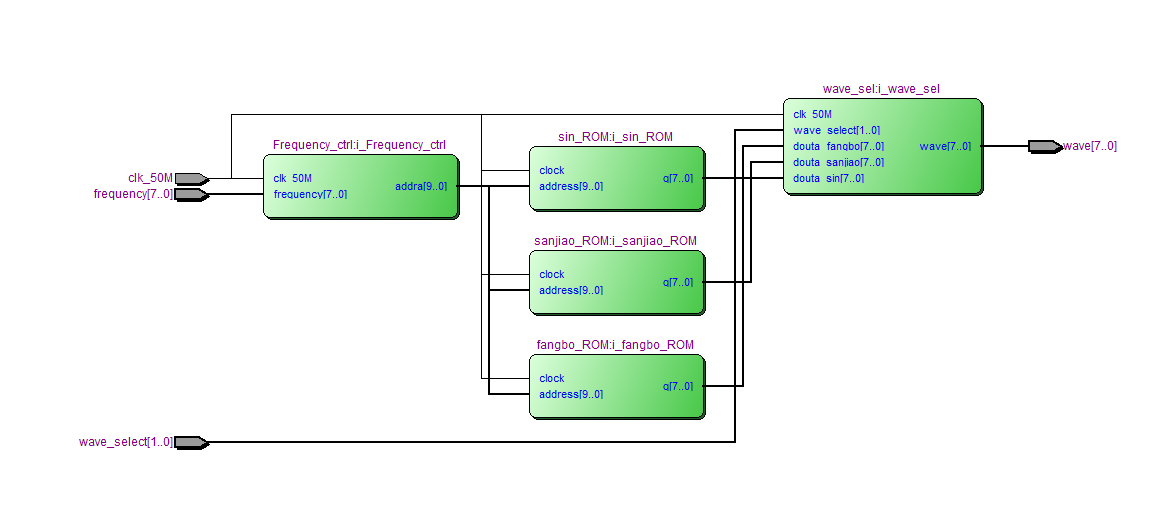

4. RTL图

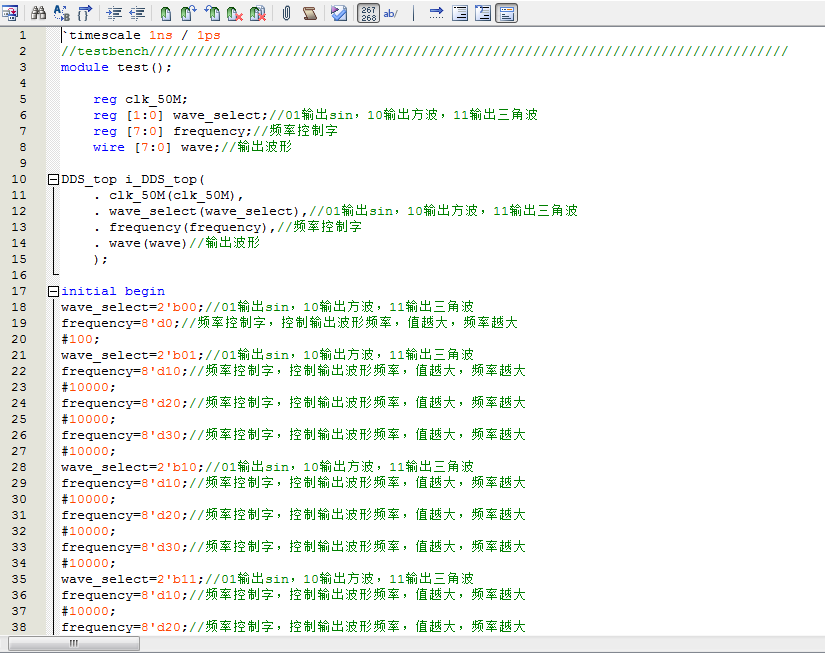

5. Testbench

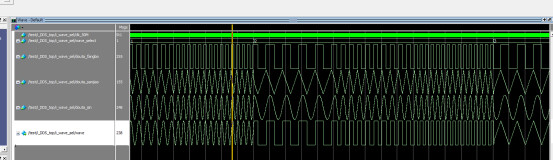

6. 仿真图

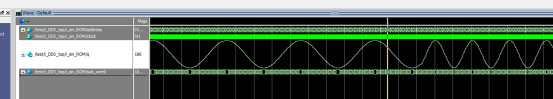

整体仿真图

方波ROM模块

三角波ROM模块

Sin波ROM模块

相位累加器模块

波形选择控制模块

部分代码展示:

`timescale 1ns / 1ps //输出频率f=clk_50M*frequency/2^10 module DDS_top( input clk_50M,//时钟输入 input [1:0] wave_select,//01输出sin,10输出方波,11输出三角波 input [7:0] frequency,//频率控制字,控制输出波形频率,值越大,频率越大 output [7:0] wave//输出波形 ); wire [9:0] addra; wire [7:0] douta_fangbo; wire [7:0] douta_sanjiao; wire [7:0] douta_sin; //方波ROM fangbo_ROM i_fangbo_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_fangbo) // output wire [7 : 0] douta ); //三角波ROM sanjiao_ROM i_sanjiao_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_sanjiao) // output wire [7 : 0] douta ); //sin波ROM sin_ROM i_sin_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_sin) // output wire [7 : 0] douta ); //相位累加器 Frequency_ctrl i_Frequency_ctrl( . clk_50M(clk_50M), . frequency(frequency),//频率控制字 . addra(addra)//输出地址 ); //波形选择控制 wire [7:0] wave_rom; wave_sel i_wave_sel( . clk_50M(clk_50M), . wave_select(wave_select),//01输出sin,10输出方波,11输出三角波 . douta_fangbo(douta_fangbo),//方波 . douta_sanjiao(douta_sanjiao),//三角 . douta_sin(douta_sin), //正弦 . wave(wave_rom)//输出波形 ); assign wave=wave_rom; endmodule

完整代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/666921

推荐阅读

相关标签