- 1vue2公众号跳转小程序 wx-open-launch-weapp 超完整流程

- 2Unity用ZXing插件生成二维码_zxing unity

- 3获取本机软件安装目录_获取软件安装目录

- 48- app如何修改包名_raname

- 5sqoop导入mysql到hbase报错 java.lang.NoSuchMethodError: org.apache.hadoop.hbase.client.HBaseAdmin.

- 6基于MATLAB的遗传算法优化卡车和两架无人机的配送路径规划_卡车无人机协同配送代码

- 7Spring Boot Actuator未授权访问远程代码执行_eureka_XStream反序列化_springeureka平台未授权访问

- 8zookeeper连接不上/Session 0x0 for server null, unexpected error, closing socket connection

- 9AI-如何有效测试机器学习模型_机器学习测试

- 10必须要掌握的【Hbase Shell】_create 'scores2',{name=>'course',versions=>3},{nam

基于simulink的模拟锁相环和数字锁相环建模与对比仿真_simulink中倍频器器在哪里

赞

踩

目录

1.课题概述

模拟锁相环和数字锁相环建模的simulink建模,对比收敛曲线,对比锁定频率值。

2.系统仿真结果

3.核心程序与模型

版本:MATLAB2022a

47

4.系统原理简介

4.1 模拟锁相环(PLL)的基本原理

模拟锁相环主要由以下几个部分组成:鉴相器(Phase Detector)、低通滤波器(LPF)、压控振荡器(Voltage Controlled Oscillator, VCO)和分频器(有时还有倍频器)。

鉴相器(PD): 当输入信号f_in(t)与VCO输出信号f_vco(t)的相位差为Δθ时,鉴相器会产生一个误差电压e(t),通常表达为:

其中,K_p是鉴相增益。

低通滤波器(LPF): LPF主要用于滤除高频噪声和瞬态误差,提取出平均相位偏差,经过滤波后的电压V_c(t)可表示为:

其中,h(t)是LPF的脉冲响应函数。

压控振荡器(VCO): VCO的频率f_vco与控制电压V_c成正比关系,一般形式为:

其中,K_v是VCO的频率灵敏度。

锁相环最终的目标是使f_vco锁定在f_in的某个整数倍上,即达到相位锁定状态。

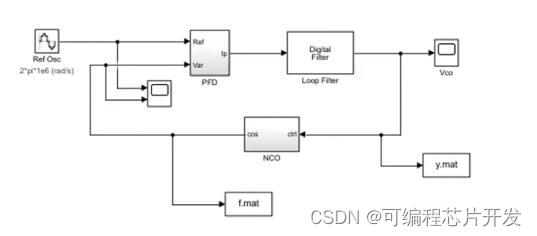

4.2 数字锁相环(DPLL)的基本原理

数字锁相环与模拟PLL类似,但工作在离散时间域,通常包括数字鉴相器、数字滤波器和数字控制的DDS(Direct Digital Synthesizer)或NCO(Numerically Controlled Oscillator)。

数字鉴相器(DPD): 数字鉴相器基于采样数据计算输入信号与本地信号的相位差,误差信号e[k]可以写作:

其中,K_d是数字鉴相增益,k是采样时刻索引。

数字滤波器(DF): DF在数字域中执行低通滤波操作,更新控制量C[k],例如使用IIR滤波器或FIR滤波器的递推公式:

或更复杂的滤波算法,其中α是滤波系数。

数字频率合成器(DDS或NCO): DDS或NCO根据控制量C[k]生成频率可控的数字正弦波,其输出频率与C[k]的关系为:

其中,F_s是采样率,N是DDS的频率分辨率位数。

5.完整工程文件

v