热门标签

热门文章

- 1黄仁勋提到的机器人世界,还需要AI数据来“调教” | CVPR 2024_具身智能 真实世界数据获取

- 2(四)根文件系统--从零开始自制linux掌上电脑(F1C200S)<嵌入式项目>

- 3Linux中信号的机制

- 4SQL常用语法( WITH 语句)_sql with

- 5Pandas中round函数的用法_pandas round

- 6数据预处理:独热编码_独热编码后的数据集怎么重塑

- 7mysql 函数和存储过程demo_$$gdatefrom

- 8超详细 springboot 整合 Mock 进行单元测试!本文带你搞清楚!_springboot mock

- 9Flink作业执行之 3.StreamGraph

- 10Rasa中文聊天机器人开发指南(3):Core篇_rasa 中文聊天机器人

当前位置: article > 正文

基于System-Verilog的FPGA设计与仿真

作者:菜鸟追梦旅行 | 2024-06-16 09:45:40

赞

踩

基于System-Verilog的FPGA设计与仿真

@TOC

一、System-Verilog实现流水灯

1.流水灯代码

led_flow.sv

module led_flow ( input logic clk, // 时钟信号 input logic rst_n, // 复位信号(低有效) output logic [7:0] led // 8位LED输出 ); logic [23:0] counter; // 24位计数器,用于产生慢时钟信号 // 计数器逻辑 always_ff @(posedge clk or negedge rst_n) begin if (!rst_n) counter <= 24'd0; else counter <= counter + 1; end // LED流水灯逻辑 always_ff @(posedge counter[23] or negedge rst_n) begin if (!rst_n) led <= 8'b0000_0001; else led <= {led[6:0], led[7]}; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

module led_flow_tb; logic clk; logic rst_n; logic [7:0] led; // 实例化待测试的流水灯模块 led_flow uut ( .clk(clk), .rst_n(rst_n), .led(led) ); // 时钟信号生成 initial begin clk = 0; forever #10 clk = ~clk; // 50MHz时钟周期为20ns end // 测试逻辑 initial begin // 初始化信号 rst_n = 0; #100; rst_n = 1; // 仿真运行一段时间后结束 #1000000; $stop; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

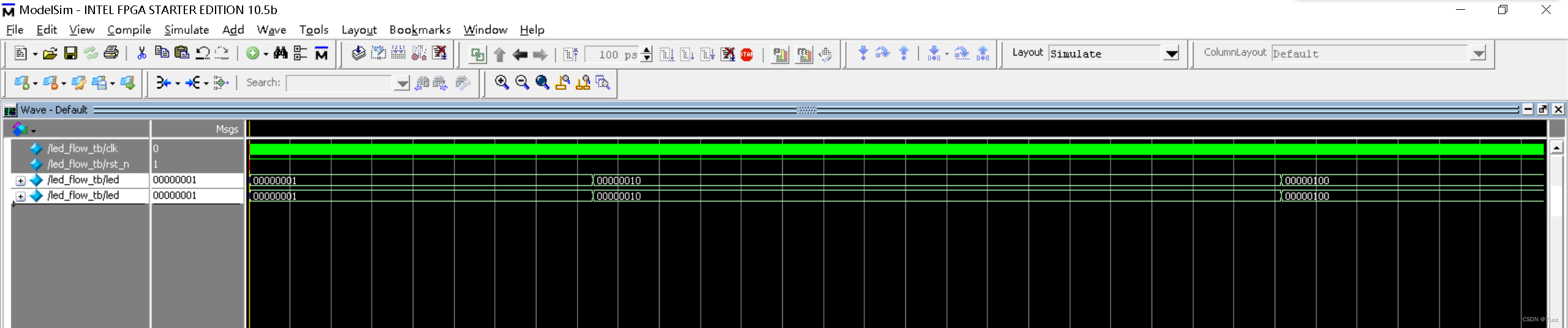

2.实验结果

3.testbench

二、参考资料

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/726144

推荐阅读

相关标签